## Aufgaben zum Thema „Speicherverwaltung“

H1. In einem virtuellen Speicher mit drei Rahmen sollen fünf Seiten verwaltet werden. Die Referenzfolge der Seiten sei 0 1 4 3 2 3 0 1 0 3 0 2.

Geben Sie für die Strategien LRU und FIFO jeweils die Folge der Speicherbelegungen an, und bewerten Sie die beiden Strategien sowohl qualitativ als auch quantitativ! Beschreiben Sie jeweils eine mögliche Implementation der Strategien! 94/7

H2. Ordnen Sie den Begriff „Arbeitsmengenmodell“ in das Gebiet Betriebssysteme ein! Erläutern Sie den Begriff anhand folgenden Beispiels:

Seitenreferenzfolge eines Prozesses: 1 2 3 3 2 4 5 2 6 4 5 2 5 7 4

Arbeitsmengenparameter: a) 3 Seitenreferenzen b) 4 Seitenreferenzen.

Beschreiben Sie Vor- und Nachteile des Verfahrens!

94/11

H3. a) Erläutern Sie den Unterschied zwischen einer physischen und einer virtuellen Adresse!

b) Betrachten Sie folgendes Beispiel: Die virtuellen Adressen haben eine Länge von 16 Bit, der physische Hauptspeicher beträgt 32 KByte, die Kachelgröße 4KByte. Die Ausschnitte der Seitentabellen zweier Prozesse lauten (P: Präsenzbit):

Seitentabelle Prozeß 1

|   | P   |   |

|---|-----|---|

| 7 | ... |   |

|   | 101 | 1 |

| 8 | 000 | 0 |

| 9 | 011 | 1 |

|   | ... |   |

|   | ... |   |

Seitentabelle Prozeß 2

|    | P   |   |

|----|-----|---|

| 11 | ... |   |

|    | ... |   |

|    | 100 | 1 |

| 12 | 101 | 1 |

| 13 | 011 | 1 |

|    | ... |   |

|    | ... |   |

Beschreiben Sie die zugehörige invertierte Seitentabelle! Welches grundsätzliche Problem wird an dem Beispiel deutlich? 95/2

H4. Ein Rechner mit 32-Bit-Adressen benutze eine zweistufige Seitentabelle. Die virtuellen Adressen werden aufgeteilt in ein 9-Bit-Feld der ersten Seitentabellenstufe, ein 11-Bit-Feld der zweiten Seitentabellenstufe und ein Offset. Wie groß sind die Seiten und wie viele sind es im virtuellen Adressraum? 96/2

H5. Erläutern Sie die Begriffe virtueller Speicher, page table und inverted page table! Gehen Sie jeweils auf Vor- und Nachteile ein! 96/8

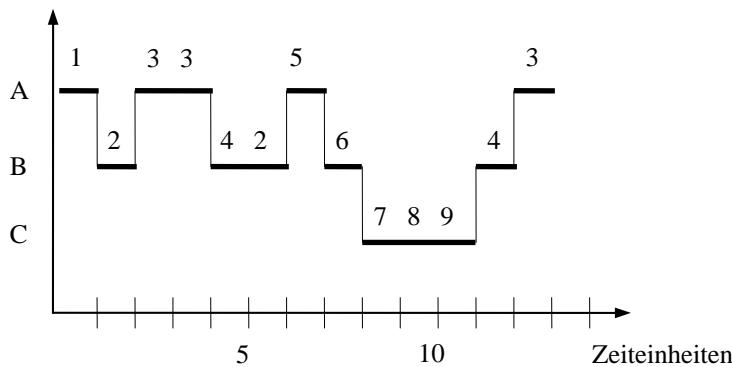

H6. Was ist ein „working set“ (Arbeitsmenge)? Welchem Ziel dient dieser Begriff? Beschreiben Sie die Vorgehensweise, und skizzieren Sie den sich ändernden Speicherinhalt für die abgebildete Referenzfolge dreier Prozesse A, B, C. Dabei soll gelten:

$m = 5$  Rahmen (Kacheln)

$\tau = 2$  Fenstergröße (Arbeitsmengenparameter).

96/8

H7\*. Ein Rechner besitze vier Kacheln (Seitenrahmen). Der Zeitpunkt des Ladens (Uhrtick), des letzten Zugriffs sowie das Referenzbit R für jede Kachel lauten:

| Kachel | Ladezeit | letzte Referenz | R |

|--------|----------|-----------------|---|

| 0      | 126      | 218             | 0 |

| 1      | 230      | 260             | 1 |

| 2      | 120      | 272             | 1 |

| 3      | 160      | 207             | 0 |

- a) Geben Sie jeweils (mit Begründungen!) die Kachel an, deren Inhalt bei den Strategien FIFO – LRU – Second Chance verdrängt wird (nehmen Sie im letzten Fall an, daß der Algorithmus zum ersten Mal angewendet wird)!

b) Angenommen, das Modified-Bit M habe bei Kachel 3 den Wert M = 1. Was ist daran ungewöhnlich? Was ist eine mögliche Erklärung dafür? 97/2

H8. Erläutern und bewerten Sie das Verfahren LRU an den Beispielen

- Seitenaustausch bei virtuellem Speicher

- Filecaching bei AFS!

97/7

H9.

- a) Erläutern Sie die Begriffe virtueller Speicher, page table und inverted page table! Gehen Sie jeweils auf Vor- und Nachteile ein!

b) Betrachten Sie folgendes Beispiel: die virtuellen Adressen haben eine Länge von 16 Bit, der physische Hauptspeicher beträgt 32 KByte, die Kachelgröße (Rahmengröße) 8KByte. Ein Ausschnitt der Seitentabelle eines Prozesses A lautet (P: Präsenzbit):

Prozeß A:

| P   |     |     |  |

|-----|-----|-----|--|

| 0   | 01  | 1   |  |

| 1   | 00  | 0   |  |

| 2   | 11  | 1   |  |

| 3   | 00  | 1   |  |

| ... | ... | ... |  |

Ein Prozeß B verlangt, daß sich mindestens Seite 0 und 1 im Hauptspeicher befinden müssen, wobei die zur Seite 1 gehörende Kachel gemeinsam mit der von Seite 2 des Prozesses A genutzt wird. Geben Sie für beide Prozesse jeweils eine mögliche vollständige Seitentabelle an! Stellen Sie die invertierte Seitentabelle auf, soweit dies möglich ist! Welches grundsätzliche Problem invertierter Seitentabellen wird an dem Beispiel deutlich? 00/8

- H10. Betrachtet werden drei Prozesse  $P_1, P_2, P_3$ , die in einem System mit Zeitscheiben-Scheduling abgearbeitet werden; die Größe einer Zeitscheibe sei  $Q$ . Dabei ergeben sich für die Prozesse einzeln (lokal) die folgenden Seitenreferenzfolgen (es wird während jeder Zeitscheibe auf genau 1 Seite zugegriffen):

$P_1: 1\ 2\ 3\ 2\ 2\ 2$

$P_2: a\ b\ b\ c\ d\ e$

$P_3: F\ F\ F\ G\ H\ H$

Für die Speicherzuteilung wird das Arbeitsmengenmodell genutzt mit einer prozeßlokalen Fenstergröße (Arbeitsmengenparameter) von  $\tau = 3Q$ .

- Bestimmen Sie die Folge der Arbeitsmengen jedes der drei Prozesse!

- Zu Beginn der Betrachtung sind alle drei Prozesse bereit (die Bearbeitungsreihenfolge ist also Prozesse  $P_1P_2P_3P_1P_2\dots$  solange keiner der Prozesse blockiert ist). Weiter stehen den Prozessen 6 Rahmen zur Verfügung. Geben Sie den weiteren Prozeßfortschritt und eine mögliche Hauptspeicherbelegung (vom Beginn an) an, wenn die Rahmen global genutzt werden können! Erläutern Sie besonders die im Zusammenhang mit dem Arbeitsmengenmodell entscheidenden Änderungen der Speicherbelegung! (Die Zeit für das Ein- und Auslagern von Seiten werde vernachlässigt.)

01/2, 98/2

- H11. Gegeben sei ein System mit virtuellem Speicher, das folgende Eigenschaften hat:

- 32-Bit-Adressen im virtuellen und physischen Speicher

- 64MByte physischer Speicher

- Seitengröße 4Kbyte

- einstufige Seitentabellen.

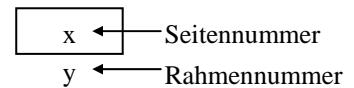

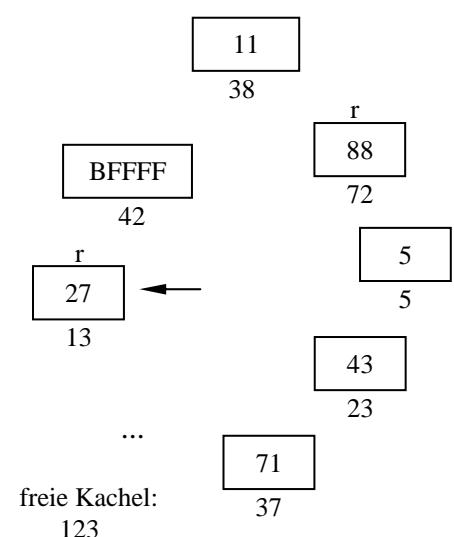

In diesem System laufe ein Prozeß, dessen Adreßraum die in Abb. 1 dargestellte Struktur hat (die Adressen kennzeichnen jeweils den Beginn der entsprechenden Bereiche); der Textbereich ist nur lesbar, die anderen Bereiche (Data, BSS, Stack) auch schreibbar. Abb. 2 beschreibt den aktuellen Zustand der Seitentabelle; Seiten mit COW-Bit werden noch von anderen Prozessen benutzt. Das Betriebssystem verwendet zur Seitenersetzung den Clock-Algorithmus; die aktuelle Liste ist in Abb. 3 dargestellt, Bedeutung:

(der Zeiger wird im Uhrzeigersinn gedreht).

Gegenwärtig ist nur noch Kachel (Rahmen) 123 frei verfügbar. Sämtliche Zahlenangaben sind hexadezimal.

| OS    | C0000000  | ...   |     |     |    |   |

|-------|-----------|-------|-----|-----|----|---|

| Stack | BFFFFE000 | E     | 53  | u   | ro |   |

| frei  | 18000     | F     | 200 | u   | ro | p |

| BSS   | 15000     | 10    | 340 | u   | ro | p |

| Data  | 13000     | 11    | 38  | u   | ro | p |

| Code  | F000      | 12    | 68  | u   | ro |   |

| frei  | 0         | 13    | 88  | u   | rw |   |

|       |           | 14    | 321 | cow | u  | p |

|       |           | 15    | 657 | u   | rw |   |

|       |           | ...   |     |     |    |   |

|       |           | BFFFF | 42  | u   | rw | p |

|       |           | ...   |     |     |    |   |

Abb. 1. Adreßraumstruktur

Abb. 2. Seitentabelle (Ausschnitt)

Abb. 3. Clock-Liste (Ausschnitt)

Vollziehen Sie die Reaktionen von Betriebssystem und Hardware auf die in der Tabelle angegebene Folge von Speicherzugriffen des Prozesses im User-Mode nach. Bestimmen Sie jeweils die physische Adresse, tragen Sie die ggf. erforderlichen Änderungen in Abb. 2 und 3 ein. Ist ein Zugriff illegal, so begründen Sie dies in der Tabelle und ignorieren Sie den Zugriff für das weitere Vorgehen (normalerweise würde der Prozeß abgebrochen). 02/2

| virtuelle Adresse | Modus | physische Adresse bzw. Begründung |

|-------------------|-------|-----------------------------------|

| BFFFFABE          | read  |                                   |

| 1038A             | write |                                   |

| 12034             | read  |                                   |

| 13304             | write |                                   |

| 11200             | read  |                                   |

| 14198             | write |                                   |

| E278              | read  |                                   |

H12. Betrachtet werde das folgende Beispiel eines virtuellen Speichers. Die virtuellen Adressen haben eine Länge von 16 Bit, die Größe des physischen Hauptspeichers beträgt 32 KByte, die Kachelgröße (Rahmengröße) 8KByte; ein Seitentabelleneintrag besteht vereinfacht lediglich aus der Kachelnummer und dem Präsenzbit P. Ein Prozeß A hat drei Seiten im physischen Speicher, der Anfang seiner Seitentabelle lautet:

Prozeß A:  $P$

|     |     |     |

|-----|-----|-----|

| 0   | 1   | 1   |

| 1   | 0   | 0   |

| 2   | 3   | 1   |

| 3   | 0   | 1   |

| ... | ... | ... |

Ein weiterer Prozeß B hat genau Seite 0 und 1 im Hauptspeicher, wobei die zur Seite 1 gehörende Kachel gemeinsam mit der von Seite 2 des Prozesses A genutzt wird.

- Wieviele Einträge hat die Seitentabelle, wieviele Rahmen gibt es?

- Geben Sie für beide Prozesse jeweils eine vollständige Seitentabelle an!

- Stellen Sie die invertierte Seitentabelle auf, soweit dies möglich ist! Welches grundsätzliche Problem invertierter Seitentabellen wird an dem Beispiel deutlich?

- Angenommen, Prozeß B greift nun auf Seite 5 seines Adressraumes zu. Was geschieht dann? Beschreiben Sie die daraus resultierenden möglichen Reaktionen des Betriebssystems! 02/8

H13. Betrachtet werde folgende prozeßlokale Strategie zur Verdrängung von Seiten in einem virtuellen Speichersystem. Es bezeichne:

- GZ Gesamtzahl der Referenzen zu irgendeiner Seite seit Prozeßstart

EZ(i) Wert von GZ zum Zeitpunkt der Einlagerung von Seite i

RZ(i) Zahl der Referenzen auf die Seite i seit EZ(i).

Wenn eine Seite verdrängt werden muß, so wird daraus die Größe RD(i) gemäß

$$RD(i) = RZ(i)/(GZ - EZ(i))$$

berechnet, und es wird die Seite mit dem kleinsten RD(i)-Wert verdrängt.

- a) Gegeben sei die bisherige Referenzfolge eines Prozesses:

1 3 1 1 3 2 1 1 4 2 1 4 2 3 1 2 1.

In dieser Situation (GZ hat also den Wert 17) sei eine Seite des Prozesses zu verdrängen. Welche wird ausgewählt?

- b) Nennen und begründen Sie je einen Vorteil und einen Nachteil im Vergleich zu einer der Strategien FIFO, LFU (least frequently used) oder LRU (least recently used)! 03/3

- H14. Betrachtet werde folgendes (realitätsferne) Beispiel eines virtuellen Speichers. Die virtuellen Adressen haben eine Länge von 14 Bit, die Größe des physischen Speichers beträgt 2 KByte, die Seitengröße 256 Byte. Ein Eintrag in der Seitentabelle ist 8 Bit groß, wobei die ersten vier Bit für die Rahmenadresse verwendet werden.

- a) Wie groß ist dann die Seitentabelle?

- b) Ein Ausschnitt der Seitentabelle eines Prozesses laute (Angaben hexadezimal):

|     | ... | R/W | P   |

|-----|-----|-----|-----|

| 0   | 5   | ... | 1   |

| 1   | 7   | ... | 0   |

| 2   | 7   | ... | 1   |

| 3   | 9   | ... | 1   |

| ... | ... | ... | ... |

P: Präsentbit

R/W-Bit = 0: Seite nur lesbar

- α) Ist dies eine zulässige Seitentabelle? (Begründung!)

- β) Der Prozeß greife jeweils schreibend auf folgende virtuellen Adressen (hexadezimal) zu:

210 – 012 – 1A4.

Ist der Zugriff möglich? Wenn ja, bestimmen Sie die zugehörige physische Adresse; wenn nein, begründen Sie dies und erläutern Sie, wie das Betriebssystem auf einen solchen Zugriff reagiert! 03/3

- H15. Ist eine 24 Bit lange virtuelle Adresse mit einer physischen Adressbreite von 32 Bit vereinbar?

Wenn ja: Begründung; worin liegt der Vorteil?

Wenn nein: Wie ist es dann möglich, den gesamten physischen Speicher zu nutzen? 04/3

- H16. Eine fiktive 64-bit-Prozessorarchitektur soll einen vollen 64-bit-adressierbaren physischen Adressraum unterstützen. Die Seitengröße dieser Architektur sei 4 KByte. Die Architektur implementiert eine mehrstufige Seitentabelle (multi-level page table), wobei die zu jeder einzelnen Stufe gehörige Tabelle in jeweils einer Seite gespeichert werden soll.

- a) Wie groß muß ein Seitentabelleneintrag in dieser Architektur mindestens sein, wenn zusätzlich noch die nachfolgend angegebenen Bits gespeichert werden sollen?

a = accessed    p = present    s = supervisor    w = writable    x = executable

Welche Größe eines Eintrag würden Sie folglich für eine Realisierung wählen und warum?

- b) Im folgenden seien die Einträge in eine Seitentabelle 1 Maschinenwort groß. Wie viele Einträge können dann in einer Stufe der Seitentabelle (d. h. in 4 KByte) gespeichert werden?

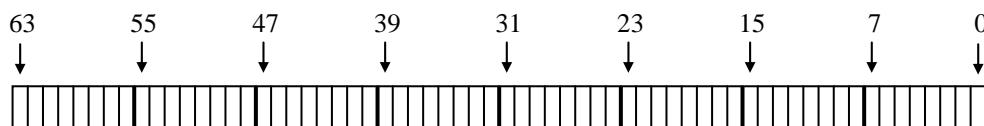

- c) Wie viele Stufen hat die Seitentabelle? Markieren Sie in dem unten angegebenen Bild, welche Bits einer virtuellen Adresse welche Stufe der Seitentabelle indizieren! 04/3

H17. Betrachtet werde folgendes Beispiel eines virtuellen Speichers. Die virtuellen Adressen haben eine Länge von 18 Bit, die Größe des physischen Speichers beträgt 32 KByte, die Seitengröße 256 Byte.

- Wie viele Einträge (Zeilen) hat dann eine einstufige Seitentabelle?

- Ein Ausschnitt der Seitentabelle eines Prozesses laute:

|     | COW | R/W | P   |

|-----|-----|-----|-----|

| 0   | 18  | 0   | 0   |

| 1   | 2A  | 0   | 1   |

| 2   | 05  | 0   | 1   |

| 3   | 2B  | 0   | 1   |

| 4   | 1C  | 1   | 0   |

| ... | ... | ... | ... |

P: Präsentzbit;

R/W-Bit = 0: Seite nur lesbar;

COW: copy-on-write-Bit;

restliche Zahlenangaben hexadezimal

Der Prozeß greife jeweils schreibend auf folgende virtuellen Adressen zu:

0x377 – 0x26A – 0x0C4 – 0x42D.

Bestimmen Sie entweder die zugehörige physische Adresse, oder beschreiben Sie die Reaktion des Betriebssystems, falls der Zugriff auf die Adresse nicht (unmittelbar) möglich ist!

- Die nachstehende Seitentabelle enthält einen Fehler. Welchen? Begründung!

04/8

|     | COW | R/W | P   |

|-----|-----|-----|-----|

| 0   | 98  | 0   | 0   |

| 1   | 2A  | 0   | 1   |

| 2   | 06  | 1   | 1   |

| 3   | 2A  | 0   | 1   |

| 4   | 14  | 1   | 0   |

| ... | ... | ... | ... |

H18. Gegeben sei nachstehende Seitenreferenzfolge eines Prozesses: 1 0 2 0 1 7 2 0 6 2 5 7.

- Tragen Sie in die unten stehenden Tabellen für die Verdrängungsstrategien FIFO und LRU die Folge der Speicherbelegungen ein unter der Annahme, daß der Prozeß drei Rahmen (Kacheln) nutzen kann! Kennzeichnen Sie das Auftreten von Seitenfehlern!

| FIFO: | Rahmen | 1 | 0 | 2 | 0 | 1 | 7 | 2 | 0 | 6 | 2 | 5 | 7 |

|-------|--------|---|---|---|---|---|---|---|---|---|---|---|---|

|       | 0      |   |   |   |   |   |   |   |   |   |   |   |   |

|       | 1      |   |   |   |   |   |   |   |   |   |   |   |   |

|       | 2      |   |   |   |   |   |   |   |   |   |   |   |   |

| LRU: | Rahmen | 1 | 0 | 2 | 0 | 1 | 7 | 2 | 0 | 6 | 2 | 5 | 7 |

|------|--------|---|---|---|---|---|---|---|---|---|---|---|---|

|      | 0      |   |   |   |   |   |   |   |   |   |   |   |   |

|      | 1      |   |   |   |   |   |   |   |   |   |   |   |   |

|      | 2      |   |   |   |   |   |   |   |   |   |   |   |   |

- b) Jemand schlägt vor, in einem System statt der bisherigen Ersetzungsstrategie LRU die Strategie FIFO zu verwenden. Geben Sie je ein Argument für und gegen diesen Vorschlag an! Welches Argument wiegt schwerer?

- c) Ist im vorliegenden Fall eine der beiden Strategien optimal? (Begründung!) 07/8, 04/8

H19. In einem Rechensystem werde der Hauptspeicher nach dem Arbeitsmengenmodell (working set) zugeteilt. Die Fenstergröße betrage dabei prozeßlokal 4, ein Prozeß kann also maximal vier Rahmen belegen. Die Abbildung zeigt einen Ausschnitt aus dem virtuellen Adressraum eines Prozesses A und seiner Seitentabelle. Die Seitengröße beträgt 4 KByte, alle Adressangaben sind hexadezimal. Weiterhin werde angenommen, daß die vier angegebenen Befehle die ersten Befehle des Prozesses sind, beginnend ab Adresse 1000. Dabei bedeute beispielsweise `ADD AX<- [ 4280 ]`: addiere den auf Adresse 4280 stehenden Inhalt zum Inhalt von Register AX. Die Freispeicherliste wird als Stack behandelt; das oberste Element ist Rahmen 11, daran schließen sich die Rahmen 7, 17 und 12 an.

- a) Wie lautet die Seitenreferenzfolge nach Ausführung der vier Befehle?

- b) Geben Sie im oberen Teil (Seitentabelle 1) ein vollständiges Bild der Seitentabelle an, nachdem die ersten drei Befehle ausgeführt worden sind! Eintragungen, die aus der Aufgabenstellung nicht hervorgehen, lassen Sie frei.

- c) Tragen Sie in dem unteren Bild (Seitentabelle 2) die Situation ein, die nach Ausführung des vierten Befehls (Speichern des Inhalts von Register AX auf die Adresse 26A4) entsteht! 05/2

virt. Adressraum von A

|      |                  |                  |                   |                  |

|------|------------------|------------------|-------------------|------------------|

| 0    |                  |                  |                   |                  |

| 1000 | MOV AX<- [ 200 ] | MOV [ 3B00 ]<-AX | ADD AX<- [ 4280 ] | MOV [ 26A4 ]<-AX |

| 2000 |                  |                  |                   |                  |

| 3000 |                  |                  |                   |                  |

| 4000 |                  |                  |                   |                  |

| 5000 |                  |                  |                   |                  |

Seitentabelle 1

| Seite | Rahmen | P | W | A | D |

|-------|--------|---|---|---|---|

| 0     |        |   |   |   |   |

| 1     |        |   |   |   |   |

| 2     |        |   |   |   |   |

| 3     |        |   |   |   |   |

| 4     |        |   |   |   |   |

| 5     |        |   |   |   |   |

Seitentabelle 2

| Seite | Rahmen | P | W | A | D |

|-------|--------|---|---|---|---|

| 0     |        |   |   |   |   |

| 1     |        |   |   |   |   |

| 2     |        |   |   |   |   |

| 3     |        |   |   |   |   |

| 4     |        |   |   |   |   |

| 5     |        |   |   |   |   |

P Present-Bit

W Working-Set-Bit

W = 1: Seite gehört zu working set

A Accessed Bit

(used, referenced)

D Dirty Bit (modified)

12

17

7

11

frei

H20.

- a) Wozu dient eine einfache Seitentabelle? Wie ist in dieser Tabelle ein Eintrag aufgebaut?

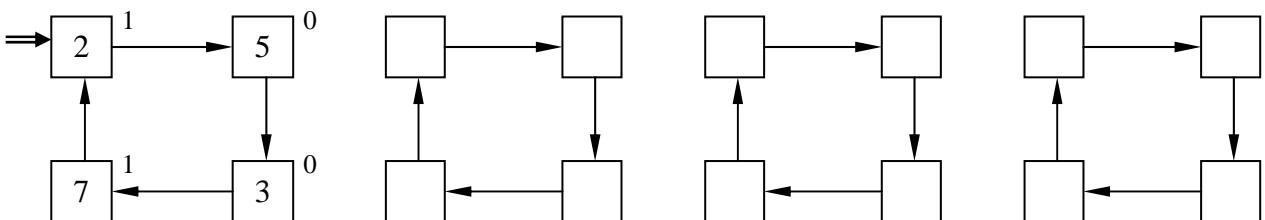

- b) In einem virtuellen Speichersystem wird zur Seitenverdrängung der Second-Chance-Algorithmus (Clock-Algorithmus) verwendet. Es werde angenommen, daß ein Prozeß vier Rahmen nutzen kann. Die aktuelle Clock-Liste habe den unten links angegebenen Zustand; der Zeiger zeigt auf die Seite, die als nächste zu untersuchen ist (also auf die Seite *nach* der letzten Einlagerung). In dieser Situation wird die Seitenreferenzfolge

2 3 2 4 7 4 6

betrachtet. Geben Sie in den nachfolgenden Bildern den Zustand der Clock-Liste unmittelbar nach Beheben der auftretenden Seitenfehler an (nachdem jeweils eine Seite in den entsprechenden Rahmen eingelagert wurde) einschließlich Angabe der R-Bits und des Zeigers; dabei werde angenommen, daß keine freien Rahmen verfügbar sind.

09/2, 08/8, 05/8

H21. Zur Verwaltung eines 4GByte großen virtuellen Adreßraums werde eine zweistufige Adreßumsetzung verwendet. Dabei werden die virtuellen Adressen aufgeteilt in ein 8-Bit-Feld der ersten Stufe und ein 10-Bit-Feld der zweiten Stufe, der Rest wird als Offset benutzt.

- a) Wie groß ist eine Seite (in KByte), wie viele Seiten enthält der virtuelle Adreßraum?

- b) Worin liegt der entscheidende Vorteil einer zweistufigen gegenüber einer einstufigen Adreßumsetzung? Hat diese Vorgehensweise auch Nachteile?

- c) Was spricht für eine Aufteilung der Adresse auf die beiden Stufen in der angegebenen Weise, in welcher Situation ist eine umgekehrte Aufteilung (10 Bit für 1. Stufe, 8 Bit für 2. Stufe) günstiger?

07/8, 06/3

H22. Betrachtet werde eine Rechnerarchitektur mit einer Verarbeitungsbreite von 48 Bit, in der ein physischer Speicher mit einer maximalen Größe von 4 GByte und einer Rahmengröße von 64 KByte unterstützt werden soll.

- a) Wieviel Einträge hat dann eine einstufige Seitentabelle zur vollständigen Beschreibung des virtuellen Adreßraums? Was folgt daraus für die Eignung einer solchen Tabelle in der betrachteten Architektur? Welches Problem wird damit deutlich, wie kann es gelöst werden?

- b) Nennen Sie jeweils einen Vorteil und einen Nachteil für die Rahmengröße von 64 KByte im Vergleich zu einer Größe von 4 KByte!

06/8 ≈ 09/2

H23. Die Adreßraumgröße eines virtuellen Speichers betrage 64 KByte, die Seitengröße 256 Byte, und es stehe ein physischer Speicher von 16 KByte zur Verfügung.

- a) Wieviel Seiten gibt es, welches ist die größtmögliche hexadezimale Rahmennummer?

- b) Der virtuelle Adreßraum werde durch eine einstufige Seitentabelle beschrieben. Ein Eintrag hat folgende Struktur, wobei COW für copy on write, W für schreibbar und P für present steht (leere Felder bedeuten nicht gesetztes Bit):

|                   |     |   |   |

|-------------------|-----|---|---|

| page frame number | COW | W | P |

|-------------------|-----|---|---|

Gegeben sei der in Tab. 1 dargestellte Ausschnitt einer Seitentabelle (leere Felder bedeuten nicht gesetztes Bit). Prüfen Sie den Zugriff auf die in Tab. 2 enthaltenen Adressen. Beschreiben Sie die Reaktion des Betriebssystems, falls der Zugriff nicht gestattet ist! Geben Sie andernfalls die zugehörige physische Adresse an!

|      |      |     |   |   |

|------|------|-----|---|---|

| 0x00 | 0x3E |     |   | P |

| 0x01 | 0x72 |     | W |   |

| 0x02 | 0x13 |     |   | P |

| ...  |      |     |   |   |

| 0xC4 | 0x2A |     | W | P |

| 0xC5 | 0x18 | COW |   | P |

Tabelle 1.

| Zugriff auf | Art        |

|-------------|------------|

| 0x02C1      | schreibend |

| 0xC4CA      | schreibend |

| 0x0020      | lesend     |

| 0x014B      | schreibend |

| 0xC557      | schreibend |

Tabelle 2.

09/8, 07/2, 06/3, 01/2

H24. Die Adressraumgröße eines virtuellen Speichers betrage 256 KByte, die Länge des Offsets sei 12 Bit. Der physische Speicher mit einer Größe von 64 KByte werde nach dem Arbeitsmengen-Modell vergeben. Der Arbeitsmengenparameter („Fenstergröße“) ist prozeßlokal 2, wobei den Nutzerprozessen insgesamt vier Rahmen zur Verfügung stehen.

Betrachtet werden zwei Prozesse A und B, die beide die in Tab. 1 gegebene (vereinfachte) Adressraumstruktur haben (die Einträge sind jeweils Seitennummern, keine Adressen). Die Abarbeitung der Prozesse habe zu der Referenzfolge geführt, die in nachstehender Tabelle angegeben ist. Ein einzelner Eintrag bedeutet dabei:

Prozeß: Nummer der referenzierten Seite, Art des Zugriffs.

- Wieviel Seiten gibt es, welches ist die größtmögliche Rahmennummer?

- Tragen Sie in Tab. 2 die jeweilige Arbeitsmenge sowie die Zuordnung von Seiten zu Rahmen unter Berücksichtigung von Tab. 1 ein (freie Rahmen werden aufsteigend nach ihrer Nummer vergeben, beginnend mit 0). Markieren Sie das Auftreten von Seitenfehlern!

08/2, 07/2

|       | Anfang | Ende | Attribut |

|-------|--------|------|----------|

| Code  | 0      | 3    | ro       |

| Daten | 4      | 6    | rw       |

Tabelle 1.

| Referenz     | A: 0 r | A: 4 w | B: 0 r | B: 5 r | A: 0 r | A: 5 w | B: 1 r | B: 0 r | A: 5 r | B: 6 w | A: 1 w |

|--------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| Arbeitsm. A  |        |        |        |        |        |        |        |        |        |        |        |

| Arbeitsm. B  |        |        |        |        |        |        |        |        |        |        |        |

| Rahmen       |        |        |        |        |        |        |        |        |        |        |        |

| Seitenfehler |        |        |        |        |        |        |        |        |        |        |        |

Tabelle 2.