# Diplomarbeit

# **Remote Debugging via Firewire**

Julian Stecklina

30. April 2009

Technische Universität Dresden Fakultät Informatik Institut für Systemarchitektur Professur Betriebssysteme

Betreuender Hochschullehrer: Prof. Dr. rer. nat. Hermann Härtig

Betreuender Mitarbeiter: Dipl.-Inf. Bernhard Kauer

#### AUFGABENSTELLUNG FÜR DIE DIPLOMARBEIT

Name des Studenten: Julian Stecklina

Studiengang: Informatik Immatrikulationsnummer: 3014126

Thema: Remote Debugging via Firewire

#### Zielstellung:

IEEE 1394, auch Firewire genannt, definiert ein weitverbreitetes serielles Bussystem, mit dem man Geräte und mehrere Rechner verbinden kann. Die dafür eingesetzten OHCI Controller unterstützen dabei einen Betriebsmodus, der direkten Zugriff auf den Hauptspeicher sowie das Auslösen von Interrupts ohne Beteiligung des Betriebssystemes erlaubt.

Gute Debugfähigkeiten von Kern und Anwendungen sind obligatorisch für das Minimieren des Entwicklungsaufwandes und die Akzeptanz eines Betriebssystems. Bisherige, speziell auf das entsprechende Betriebssystem zugeschnittene Debugger sind mit erheblichen Eingriffen in den Kern verbunden.

Ziel dieser Arbeit ist es, aufbauend auf GDB, eine Debugarchitektur zu entwickeln, die Remote Debugging über Firewire erlaubt. Besonderes Augenmerk ist auf möglichst minimale Änderungen im untersuchten System zu legen. Weiterhin sollte diese Architektur auch einfach in virtuellen Maschinen wie Qemu oder KVM implementierbar sein.

Um die Anwendbarkeit dieser Architektur unter Beweis zu stellen, ist ein Prototyp eines Debuggers für Nova zu entwickeln.

verantwortlicher Hochschullehrer: Prof. Dr. Hermann Härtig

Betreuer: Dipl.-Inf. Bernhard Kauer

Institut:SystemarchitekturProfessur:BetriebssystemeBeginn:01. 11. 2008Einzureichen:30. 04. 2009

Dresden, 30. 10. 2008

| Erklärung  Hiermit erkläre ich dess ich diese Arbeit selbstständig erstellt und keine anderen als die                             |

|-----------------------------------------------------------------------------------------------------------------------------------|

| Hiermit erkläre ich, dass ich diese Arbeit selbstständig erstellt und keine anderen als die angegebenen Hilfsmittel benutzt habe. |

| Dresden, den 30. April 2009                                                                                                       |

|                                                                                                                                   |

| Julian Stecklina                                                                                                                  |

| Januar Stockimu                                                                                                                   |

|                                                                                                                                   |

|                                                                                                                                   |

#### **Abstract**

Traditionally, the legacy RS-232 serial port has been used to connect a remote debugger to its target system. The debugged operating system had to be enhanced with support code to handle this connection. This thesis explores a novel approach to debugging that uses the Firewire bus not only as fast communication medium but also as remote manipulation tool. This approach promises to minimize support code in the debugged system by injecting the code needed for remote debugging at runtime.

Based on the GNU Debugger, a remote debugger for the NOVA microhypervisor has been implemented that fulfils these promises. The result is a fully functional debugger fit for everyday use. Furthermore, the bulk of its implementation is not specific to NOVA and can be quickly adapted to other kernels in need of a debugger.

# **Contents**

| 1 | Intr | oduction                                              | 1  |

|---|------|-------------------------------------------------------|----|

|   | 1.1  | The Need for a Kernel Debugger                        | 1  |

|   | 1.2  | Systems Programming and Reusable Tools                | 1  |

|   | 1.3  | Avoiding Stale Code                                   | 2  |

|   | 1.4  | Remote Debugging                                      | 3  |

|   | 1.5  | Enter: Firewire                                       | 3  |

|   | 1.6  | Goals                                                 | 4  |

|   | 1.7  | Terminology                                           | 4  |

|   | 1.8  | Organization of This Thesis                           | 4  |

| 2 | Tecl | nnical Background                                     | 5  |

|   | 2.1  | The Serial Port                                       | 5  |

|   | 2.2  | The PCI Bus                                           | 5  |

|   | 2.3  | The Universal Serial Bus                              | 6  |

|   | 2.4  | The Firewire Bus                                      | 7  |

|   | 2.5  | The Open Host Controller Interface                    | 9  |

|   | 2.6  | An Overview of Interrupt Handling on the PC           | 11 |

|   | 2.7  | Summary                                               | 13 |

| 3 | Rela | ated Work                                             | 15 |

|   | 3.1  | Approaches to System Debugging                        | 15 |

|   | 3.2  | Debuggers Using Firewire                              | 17 |

|   | 3.3  | The GNU Debugger                                      | 18 |

|   | 3.4  | Summary                                               | 20 |

| 4 | A Fı | amework in Three Parts                                | 21 |

|   | 4.1  | Initial Considerations                                | 21 |

|   | 4.2  | The Bird's Perspective                                | 22 |

|   | 4.3  | The Monitor                                           | 23 |

|   | 4.4  | The Target Kernel Stub                                | 25 |

|   | 4.5  | Summary                                               | 29 |

| 5 | Imp  | lementation                                           | 31 |

|   | 5.1  | The NOVA Microhypervisor                              | 31 |

|   | 5.2  | Mapping the Design onto the 32-bit Intel Architecture | 31 |

|   | 5.3  | Implementing the Monitor                              | 34 |

|   | 5.4  | Integration into the NOVA Microhypervisor             | 36 |

|   | 5.5  | Integration into the Linux Kernel                     | 38 |

|     | 5.6 Performance Improvements                              | 38 |

|-----|-----------------------------------------------------------|----|

|     | 5.7 Programming the OHCI                                  |    |

|     | 5.8 Summary                                               | 39 |

| 6   | Evaluation                                                | 41 |

|     | 6.1 Revisiting the Goals                                  | 41 |

|     | 6.2 Measuring Monitor Performance: A Statistical Profiler | 45 |

|     | 6.3 Summary                                               | 47 |

| 7   | Future Work                                               | 49 |

|     | 7.1 Porting to 64-Bit                                     | 49 |

|     | 7.2 Supporting Multiprocessor Systems                     | 50 |

|     | 7.3 Build One to Throw Away                               | 50 |

|     | 7.4 Summary                                               | 51 |

| 8   | Conclusion And Outlook                                    | 53 |

| Acr | ronyms                                                    | 55 |

| Bib | bliography                                                | 56 |

# **List of Tables**

| 1.1 | The size of Fiasco's kernel debugger                    | 2  |

|-----|---------------------------------------------------------|----|

| 1.2 | Comparing the bandwidth of Firewire and the serial port | 3  |

| 2.1 | Features of the serial port, USB, and Firewire          | 7  |

| 4.1 | Direct support for remote debugging operations          | 22 |

| 6.1 | The size of kernel code devoted to the debugger stub    | 42 |

| 6.2 | Cost of a single monitor interrupt                      | 45 |

# **List of Figures**

| 2.1 | A typical PCI card                                    | 5  |

|-----|-------------------------------------------------------|----|

| 2.2 | The USB Type A connector                              | 6  |

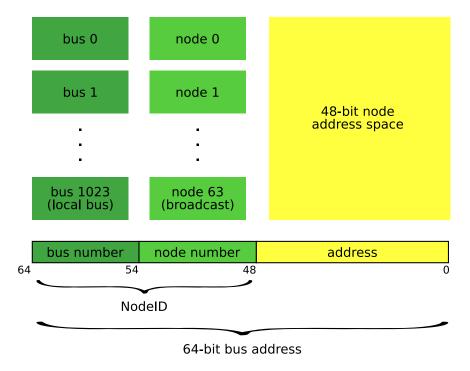

| 2.3 | Firewire 64-bit bus address space                     | 8  |

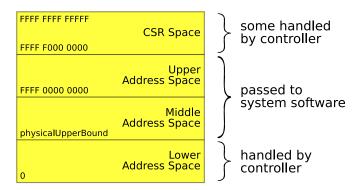

| 2.4 | A node's address space                                | 9  |

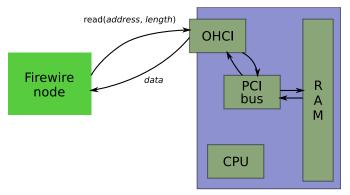

| 2.5 | Remote memory access using the Firewire bus           | 10 |

| 3.1 | The Emacs GDB frontend GUD                            | 19 |

| 3.2 | A DDD session                                         | 19 |

| 4.1 | The three parts of the framework                      | 23 |

| 4.2 | Components of the monitor                             | 24 |

| 4.3 | Command space layout                                  | 26 |

| 4.4 | Halting the target                                    | 27 |

| 4.5 | Resuming execution of the target                      | 28 |

| 4.6 | Handling debug events                                 | 29 |

| 5.1 | Injecting the kernel stub                             | 37 |

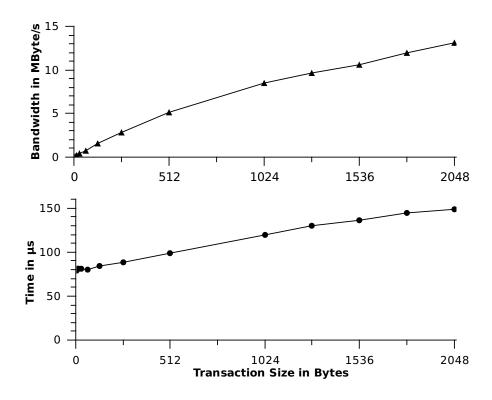

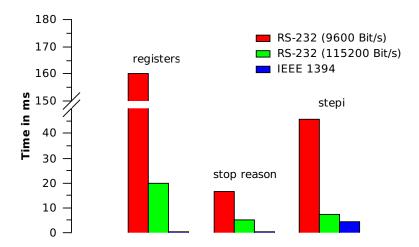

| 6.1 | Cost of Firewire transactions                         | 43 |

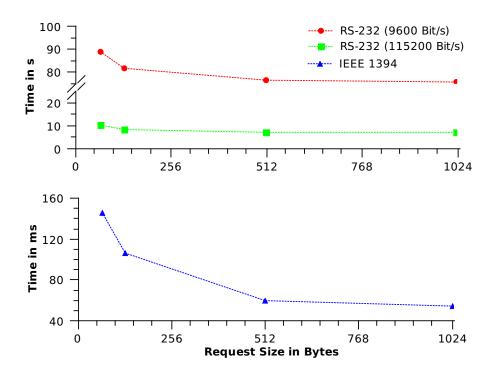

| 6.2 | Amount of time needed for common debugging operations | 44 |

| 6.3 | Latency of memory read operations                     | 44 |

| 6.4 | Sampling execution state                              | 46 |

| 7.1 | Design changes for multiprocessor systems             | 50 |

# 1 Introduction

"There are two ways to write error-free programs; only the third one works."

Alan J. Perlis

# 1.1 The Need for a Kernel Debugger

The kernel is one of the most critical parts in a reliable and secure system. A single bug in the kernel can potentially undermine both of these qualities, reliability and security. Yet despite decades of research in programming languages and methodology, there is still no silver bullet that lives up to its promise of advancing software engineering to a point, at which bug-free software becomes reality [10]. Thus every sufficiently complex program contains errors.

It is commonly known that the amount of errors in a program correlates to lines of code. By minimizing lines of code, the amount of—potentially disastrous—bugs can be reduced. The microkernel approach [23] is one way of achieving code reduction in the kernel.

Due to high complexity of systems code, a potential for errors remains even in microkernels and different methods can be used to spot them. One approach is to use formal verification to prove correctness against a specification. Although initial success is reported in the literature [19, 30, 36], a complete verification would encompass not only the kernel, but also the compiler and the processor to be truly meaningful.<sup>1</sup> Given the complexity of modern general-purpose microprocessors, a complete verification may not be practical.

Another approach is using a programming language for systems code that aids in the discovery of bugs at compile time. One recent proposal is the *BitC* language [29], which supports a rich type system that enables the programmer to express even complicated operations without resorting to type-unsafe code. While BitC looks promising, it has yet to spread beyond its origin, the EROS group. The vast majority of systems code is still implemented in unverified C or C++.

# 1.2 Systems Programming and Reusable Tools

Writing systems programs still remains an art of engineering. According to popular lore, a good workman—and, by extension, engineer—is known by his tools. The proverb probably predates the information age by a fair number of years, but its essence survives unchanged.

<sup>&</sup>lt;sup>1</sup> Even a verified compiler can fail to meet its specification. This situation is illustrated best by "transitive" trojan horses [26]. A malicious compiler can substitute arbitrary code when compiling the verified compiler, resulting in a compromised binary [35]. The same reasoning applies to *buggy* compilers. A buggy compiler may introduce hard-to-find bugs in every binary program it produces. Processors are, of course, susceptible to the same problem.

The quality of the systems programmer's work is greatly influenced by the availability and quality of his tools.

Tools available to systems programmers are mostly written and maintained by themselves, yet time spent on such tools is mostly frowned upon by chief executives, as there is no tangible progress of the project. One consequence is that tools are largely neglected or considered a burden instead of being improved when they fail to meet expectations [15].

A quickly retargetable system debugger is such a tool with the potential of boosting productivity in a working or scientific environment in which experimental systems code is written to evaluate new ideas. Such projects commonly do not have the resources to develop a suitable debugger. Being able to use a proper debugging environment from the start of a project, can be a great asset to productivity.

But before developing this idea further, I want to shift the focus to Fiasco's debugging facilities to make another point.

## 1.3 Avoiding Stale Code

For a decade the Fiasco kernel [20], a second-generation microkernel, has been one of the research vehicles of the Operating Systems Group of Technische Universität Dresden. It contains *JDB*, a sophisticated in–kernel debugger.

| Component          | Lines of code | Percentage |

|--------------------|---------------|------------|

| JDB                | 20,614        | 23 %       |

| Support code       | 9,914         | 11 %       |

| JDB + Support code | 30,528        | 34 %       |

| Fiasco total       | 88,215        | 100 %      |

Table 1.1: The size of JDB, the kernel debugger of the Fiasco microkernel, compared to the size of Fiasco itself. The measurement includes machine–specific code for all platforms Fiasco supports.

JDB alone accounts for about one fourth of Fiasco's source code.<sup>2</sup> Adding libraries that are only used by JDB, the part of Fiasco devoted to debugging grows to one third. These libraries are used to process compressed data, disassemble instructions, and evaluate regular expressions.

A quick review of the code reveals that the compression library, an ancient version of *zlib*,<sup>3</sup> is vulnerable to specially crafted compressed data streams. These vulnerabilities are not security relevant. An attacker with access to the kernel debugger does not need to bother with security vulnerabilities.

However, this stale library and its long-fixed bugs hint that accumulating code in the kernel that does not contribute to its main functionality might be a problem in the long run. It would have been disastrous, if a future developer chose to use zlib's features to implement critical functionality.

<sup>&</sup>lt;sup>2</sup> Code size measurements were generated using David A. Wheeler's 'SLOCCount'.

<sup>&</sup>lt;sup>3</sup> zlib is a compression library that is used in many open-source projects. Its current version can be obtained from http://www.zlib.net/.

| Medium                | Duration |

|-----------------------|----------|

| RS-232 (9600 Bit/s)   | 18 min   |

| RS-232 (115200 Bit/s) | 91 s     |

| Firewire              | < 0.1  s |

Table 1.2: The theoretical duration of a one megabyte data transfer using the serial port (RS-232) compared to Firewire.

It is unlikely that the Fiasco project is going to remove JDB, which is otherwise a great debugger, but other kernel projects might want to avoid having to maintain a large debugger in the kernel source.

## 1.4 Remote Debugging

An alternative to using an in–kernel debugger is remote debugging using the PC's serial port with the GNU Debugger (GDB). Because of its support for a wide range of platforms and its free availability, GDB is favored by many developers [16].

By using remote debugging, a large debugger inside the kernel becomes superfluous. Instead, only a comparably small stub is needed to handle commands transmitted using the serial connection from the debugging host on which GDB is running. These commands range from simple, like reading and writing of memory and registers, to more complicated ones, like setting breakpoints or—in a multithreaded target—manipulating threads.

Adding rudimentary support for remote debugging to a kernel is simple [17]. Supporting larger parts of the protocol, however, is a quite involved task, because its semantics is poorly documented. Anecdotal evidence suggests that debugging stubs are implemented in an ad-hoc fashion. Their maintenance is largely ignored once they seem to work.

Additionally, the serial connection used for communication between stub and GDB is painfully slow for today's standards (Table 1.2). Remote debugging with GDB using the serial port is clearly not an optimal solution. But how can it be improved?

#### 1.5 Enter: Firewire

During the last years, several operating systems have been adding support for the IEEE 1394 serial bus, commonly known as Firewire, as communication medium for remote debugging. Section 3.2 deals with them in more detail.

Suffice it to say that these implementations use Firewire because of its speed, but ignore its more intriguing features allowing the implementation of a debugger with *less to no support code in the target kernel at all* compared to classical remote debugging with the GNU Debugger. Exploring these features was one of the main incentives for this thesis.

#### 1.6 Goals

The goal of this thesis is to devise and implement a remote system debugger based on the GDB that is able to perform basic debugging operations on the kernel of an operating system. That is, it should be able to:

- control execution of the system;

- inspect and manipulate data structures;

- set break- and watchpoints.

This debugger should require *considerably less changes* to the operating system kernel than remote debugging over a serial connection, thereby reducing the amount of code that has to be maintained inside the kernel. It should improve upon the interactive speed of remote debugging and, at the same time, provide *at least* the same features as remote debugging.

Lacking any kind of proper debugger, the NOVA microhypervisor [34] has been chosen as test case for this architecture.

# 1.7 Terminology

So far, I have relied on the implicit understanding of certain terms, but at this point it is necessary to agree on the concrete meaning of these terms to avoid confusion in later chapters.

The **target system** or simply **target** is the computer running a operating system that is to be debugged. The **target kernel** is the kernel of the operating system running on the target system. The kernel contains a **debugging stub**, which is the part of the kernel that had to be added to support a debugging framework. The **host system** or simply **host** is the computer running the debugger. The debugger will almost exclusively be the GNU Debugger in our case.

## 1.8 Organization of This Thesis

The next chapter gives the required technical background information. Its sections are intended to be self-contained. The impatient or already informed reader may skip it and refer to it as the need arises. Chapter 3 gives an overview about system debugging in general and introduces several debugging frameworks that already utilize Firewire. The generic design of the debugging architecture is presented in Chapter 4. It is complemented with the description of the implementation of the monitor and kernel stub for the NOVA microhypervisor as well as the Linux kernel in Chapter 5. In Chapter 6, I answer the question, how this architecture compares to classical remote debugging and whether the developed architecture performs well enough to be used for other purposes, such as profiling or tracing. Chapter 7 sketches the solutions of several open problems that can form the basis of future projects. The closing chapter, Chapter 8 summarizes this thesis and gives some final remarks.

# 2 Technical Background

This chapter starts with overviews of several technologies that are touched by this thesis. I will address the serial port, PCI, USB, and Firewire. Following that, I continue describing interrupt handling on the PC platform, which is particularly important to the discussion in Chapter 5.

#### 2.1 The Serial Port

The serial port has been a standard external interface of the PC since the original IBM PC design introduced in 1981, but the underlying technology, RS-232, exists far longer.

It was a primary method of connecting external peripheral devices to the PC, but is today classified as 'legacy port' by hardware vendors and thus slowly disappearing. A reason for its obsolescence is its low speed, typically not more than 115,200 bit/s, which makes the serial port unsuitable for data–intensive applications.

The advantage of the serial port is its simplicity and its availability, which still makes it a viable option as communication medium for many applications.

#### 2.2 The PCI Bus

The Peripheral Component Interconnect (PCI) bus, introduced in 1993, is the standard expansion bus system in the PC. Typically, PCI devices come in the form of expansion cards that can be plugged into a free PCI slot on a PC's mother-board.

PCI is used to connect a variety of different internal devices, such as graphics, network, and sound cards. It is also used to connect external buses, such as Firewire and USB, to the PC using adapter cards. Firewire controllers usually come in the form of a PCI device.

The PCI bus provides three address spaces to connected devices. Accesses to any of these address spaces are performed by read and write transactions on the PCI bus.

Figure 2.1: A typical PCI expansion card.<sup>1</sup>

Image provided by Wikimedia Commons: http://commons.wikimedia.org/wiki/File:GB\_Network\_PCI\_Card.jpg

The *configuration space* is used by system software to automatically discover available PCI devices and configure them by assigning each PCI device windows of the *memory* and *input—output* address spaces. Communication with a device is then performed by accessing memory or input—output ports in these windows. Automatic configuration was a major contributor to the success of PCI.

Unless claimed by other devices, the PCI bus controller claims accesses to the memory address space and forwards them to the system's memory controller. This mechanism, which is called Direct Memory Access (DMA), allows PCI devices to access the system's main memory independently of the processor.

To learn more about the PCI bus, I recommend reading the PCI standard itself [25]. It includes an excellent, concise introductory chapter.

#### 2.3 The Universal Serial Bus

The Universal Serial Bus (USB) is a serial bus standard meant to overcome the shortcomings of peripheral handling in early PC designs. Its major advantage is the replacement of a multitude of different connectors (PS/2, RS-232, ...) with one common connector used by a diverse set of peripherals, such as keyboards, mice, or printers.

Because of its single type of connector, automatic device configuration and hot plug support, USB has been very successful.

USB is designed to reduce the cost of peripherals. It implements a star topology with the host computer at its center and follows a strict master-slave philosophy, in which *only the host can initiate transactions* on the bus and every connected device acts as a slave, which needs only a very simple (and cheap) controller. Not only does USB not support DMA, there is also no support for interrupts as well, requiring the host to periodically *poll* devices that are traditionally interrupt-driven, such as keyboards. A consequence of this approach is that direct peer–to–

Figure 2.2: The USB Type A connector.<sup>1</sup>

peer communication between peripherals is not possible.

Communicating with USB devices usually requires a complete USB software stack, which is a large and complicated piece of code. Communication via USB devices has therefore not been a prominent choice for debuggers. To alleviate this problem the USB Debug Port has been introduced.

The debug port is a special USB device that allows to connect two USB-capable PCs, between which it provides a bidirectional communication channel. Support for the USB Debug Port is an optional feature of USB host controllers [4]. If a host controller supports it, system software is able to communicate using the debug port without a complete USB

$\verb|http://commons.wikimedia.org/wiki/File:USB\_Type\_A\_Plug\_BW.svg|$

<sup>&</sup>lt;sup>1</sup> Image provided by Wikimedia Commons:

|                     | RS-232/Serial Port            | USB            | Firewire             |

|---------------------|-------------------------------|----------------|----------------------|

| Introduction        | 1969                          | 1996           | 1995                 |

| Prevalent use       | peripherals, terminal         | peripherals    | multimedia, industry |

| Speed               | 50–115,200 Bit/s <sup>1</sup> | 1.5-480 MBit/s | 400-3200 MBit/s      |

| Connectible devices | 2                             | 128            | 63                   |

| Topology            | point-to-point                | star           | tree                 |

Table 2.1: Comparison of the serial port (RS-232), USB, and Firewire. The USB and Firewire figures are from current revisions of the respective standards, USB 2.0 and IEEE 1394-2008.

stack. The specification limits the data rate in this mode to eight bytes per time slot on the bus, which limits its overall bandwidth to a maximum of 0.5 MBit/s.

#### 2.4 The Firewire Bus

The IEEE 1394 standard describes a serial bus capable of high transfer speeds (up to 3.2 GBit/s in later revisions of the standard [5]) as well as isochronous real-time data transfers common in audio and video processing. Several vendor-specific names for IEEE 1394 have been introduced since its inception, *Firewire* being the most popular one.

It is competing with USB, but has a slightly different scope. IEEE 1394 (Firewire) arose out of the need to replace SCSI for the connection of external devices, such as disks, scanners, and printers. Using SCSI for external devices is largely obsolete today; it has been superseded by IEEE 1394, USB, and eSATA in virtually all but high-end applications.

Owing to the SCSI heritage, the Firewire bus is at its core quite different from USB; it treats connected devices more like a network, in which every participant, called *node*, has equal abilities.

To consider a small example, a single Firewire bus can be used to connect two PCs, a disk, a camera, and a printer. Each device acts as a node in the network and can communicate with every other device. The two PCs can exchange IP packets over the bus, while one of them concurrently accesses the disk, while the camera sends a picture to the printer.

This admittedly synthetic example shows that the Firewire bus represents not only a means for the connection of peripheral devices, but a general networking mechanism that is open to completely unforeseen applications.

#### 2.4.1 Bus Topology and Addressing

The Firewire bus consists of nodes, each with a unique 64-bit identifier, the Globally Unique Identifier (GUID). Nodes are connected in a peer-to-peer fashion to form a tree. Multiple buses may be connected by bus bridges to form larger networks. There is no cycle detection in IEEE 1394; networks have to be noncyclic.

Nodes in the network are addressed by NodeIDs that are constructed during the initial bus enumeration and resemble the position of the node on the bus. NodeIDs can change

<sup>&</sup>lt;sup>1</sup> Higher speeds are possible, but uncommon on the PC.

Figure 2.3: System software sees the Firewire bus as 64-bit address space, which is statically split into address spaces for every node on the bus. The bus and node numbers form the NodeID, which can change when the topology of the bus changes.

on each bus reset. Because bus resets are caused, for example, when the topology changes, applications should use GUIDs to differentiate nodes from each other.

Each node provides an 48-bit address space. Together with the 16-bit NodeID (formed by the combined bus number and node number), all nodes on the network form a 64 bit address space, which is depicted in Figure 2.3.

#### 2.4.2 Transactions

IEEE 1394 defines a protocol stack with three layers:

- The *Physical Layer* arbitrates bus access and translates link layer requests into electrical signals,

- the *Link Layer* provides an acknowledged datagram service and handles isochronous data transfers, and

- the *Transaction Layer* that provides the three primitives to access the bus address space: read, write, and lock.

read and write transactions are used to read and write portions of the bus address space. The lock transaction performs an atomic *Compare-and-swap* operation that can

Figure 2.4: An Open Host Controller logically distinguishes four regions in a node's address space. Transactions touching the Lower Address Space are handled by the controller itself without informing system software. physicalUpperBound is a hardware register of the controller that can be programmed by system software. Transactions touching the Middle and Upper Address Space are passed to system software. Accesses to the CSR Space are special and are handled in part by the controller.

be used to safely update remote data structures in the presence of concurrent access from different nodes on the bus.

read, write, and lock are called *asynchronous* transactions to differentiate them from isochronous streams, which provide time guarantees. Because streams play no role in this work, I always refer to asynchronous transactions, when I use phrases, such as 'Firewire bus transaction' or 'transaction'.

# 2.5 The Open Host Controller Interface

The IEEE 1394 standard only defines the wire protocol necessary for interoperability between Firewire nodes. The Open Host Controller Interface (OHCI) complements IEEE 1394 with a standardized way of accessing the bus from software by specifying an interface of a IEEE 1394 controller (the *Open Host Controller*). Virtually all PCI Firewire controllers on the PC market try to be OHCI compliant, with only a few rare exceptions [31].

The OHCI implements the link layer of the IEEE 1394 bus with additional support for the transaction layer. Because PCI devices are the typical realization of OHCI, the specification also includes a chapter about implementing an Open Host Controller on the PCI bus [2].

#### 2.5.1 Automatic Handling of Incoming Transactions

The OHCI is a complex interface and most details are not interesting in the scope of this work. One feature in particular, however, stands out.

Incoming asynchronous transactions are handled by an Open Host Controller according to the memory region they address (see Figure 2.4). Specifically, transactions touching the Lower Address Space are passed directly to the PCI bus avoiding the need for the system's

Firewire-capable PC

Figure 2.5: Remote memory access using the Firewire bus. A node on the bus can read and write arbitrary parts of the host's memory without its processor being involved, if the Open Host Controller allows physical requests from this node.

processor and operating system to be involved, effectively opening the PCI memory address space to all nodes on the Firewire bus. The intended use of this mode of operation is to implement fast and low-latency communication protocols.

The border between Low and Middle Address Space is configured by setting the physicalUpperBound hardware register of the Open Host Controller. By setting it to its maximum value, the Middle Address Space shrinks to zero and almost the complete bus address space of the node is mapped to physical memory. Accesses to the Lower Address Space are called *physical requests*.

#### 2.5.2 Security Issues

Making a node's physical memory accessible from all other nodes on the bus presents a gaping security hole [7, 9] allowing arbitrary nodes on the bus to obtain and manipulate sensitive information (e.g., cryptographic keys or passwords). The OHCI includes several mechanisms to mitigate that.

The most effective solution is to disable the Lower Address Space by setting the physicalUpperBound register to 0. No transaction (except accesses to the CSR space) is then automatically handled in hardware and the operating system can inspect each transaction. This might incur a considerable performance overhead. Another way is to selectively enable access for trusted nodes via the AsynchronousRequestFilter and Physical-RequestFilter hardware registers. In recent PCs, the Input-Output Memory Mapping Unit (IOMMU) can also be used to effectively constrain the Open Host Controller's capabilities, but IOMMUs are not widely available, yet.

From a security point, a Firewire port that is accessible to attackers should be considered as dangerous as an accessible PCI port. The difference is that custom "attack" PCI cards [11] are expensive, but the dangerous potential of Firewire ports can be exploited by comparably cheap off–the–shelf devices as shown by [14].

## 2.6 An Overview of Interrupt Handling on the PC

Several design decisions in the following chapter are based on the low-level characteristics of the PC platform. This short discourse can by no means even begin to cover the PC platform as a whole, so, on the following pages, I will concentrate on key aspects of the hardware platform that are crucial to the rest of this thesis. These aspects will mainly revolve around interrupt handling on the PC and debugging features of the Intel processor architecture.

For a complete in-depth description of the processor architecture, you are referred to Intel's set of processor manuals [22]. Specifically, the first manual "Intel 64 and IA-32 Architectures Software Developer's Manual Volume 1: Basic Architecture" is a good entry point for learning about the Intel architecture.

#### 2.6.1 PCI Message-Signaled Interrupts

If a device on the PCI bus needs attention by the operating system, it signals an interrupt. The traditional way to do this, is for the device to assert one of the interrupt lines of the PCI bus. Because there are only a small number of interrupt lines (typically four), interrupt lines must be shared, if the number of devices exceeds the number of available interrupt lines.

Having multiple devices assigned a single interrupt line has several disadvantages [3]: If one of these devices signals an interrupt, the corresponding interrupt handler of the operating system has to check *all* devices sharing the interrupt, possibly creating a considerable interrupt latency.

PCI host controllers conforming to newer PCI specifications offer an alternative to interrupt lines, the message-signaled interrupt (MSI). Instead of asserting an interrupt line, a device performs a write transaction into a special part of the PCI memory address space to express its call for attention. PCI Express, the successor to the PCI bus, uses message-signaled interrupts exclusively.

The processor to which the interrupt is to be delivered (if there are more than one) and the type of interrupt to be generated are encoded in the address and data of the write transaction.

#### 2.6.2 Interrupt Handling on the Processor

If an interrupt arrives at the processor, the corresponding handler procedure must be executed. For that purpose, the processor maintains an Interrupt Descriptor Table (IDT) with one descriptor for each possible interrupt. There are three different types of descriptors that each cause the processor to take a different action, when the corresponding interrupt is signaled.

Trap Gate and Interrupt Gate descriptors cause the CPU to execute a handler procedure

specified by a pointer in the descriptor. The handler procedure is executed similar to

a normal function call by preserving the state necessary to return to the interrupted

code on the current stack.<sup>1</sup> The difference between Trap and Interrupt Gates is that the latter disables interrupts upon entering the handler.

• *Task Gate* descriptors cause the CPU to perform a *task switch* to a task that is supposed to handle the interrupt.

Task switching is a seldom used feature of the Intel architecture. When the processor performs a task switch, it stores its current state in the Task State Segment (TSS) of the current task and loads the contents of the new task's TSS. I will refer to this as *hardware* task switching to distinguish it from manual context switching done by the operating system.

Most systems programmers frown upon using hardware task switching, because it is perceived to be slow compared to manual context switching.

#### 2.6.3 Debugging Features

The Intel processor architecture includes support for single-stepping and breakpoints. The core of this functionality is provided by the TF (trap) flag in the eflags register, the breakpoint instruction int 3, and the debug registers dr0-dr7.

Debug events are reported as either debug exception (#DB) or breakpoint exception (#BP), depending on the type of event, and can be handled by the operating system exactly as other exceptions and interrupts.

The TF flag is used to implement single-stepping. When this flag is set, a debug exception (#DB) is generated after each completed instruction. The processor clears the flag before entering the debug exception handler.

To set instruction breakpoints, the int 3 instruction can be inserted by a debugger (or compiler) at the designated place in the application's code. Because this involves changing the code of the application by the debugger, these breakpoints are referred to as *software breakpoints*. When the CPU encounters this instruction, a breakpoint exception (#BP) is triggered and control is transferred to the corresponding handler procedure.

Another way to set breakpoints involves the debug registers. These breakpoints are versatile, but only four can be active at any given time. These breakpoints are referred to as hardware breakpoints. To set a hardware breakpoint, the address must be written into one of the lower four debug registers. Flags in dr7 are then used to enable these breakpoints and to specify their type. There are several different types of hardware breakpoints. The most important are:

- *Instruction breakpoints* cause the processor to generate a debug event when the instruction at the specified address is to be executed.

- Read breakpoints cause a debug event when the address is about to be read as data.

- *Read/Write breakpoints* cause a debug event when the address is used in either a read or write operation.

<sup>&</sup>lt;sup>1</sup> Actually, the stack is switched when the interrupt handler is to execute in another privilege level, but that opens a whole new can of worms that adds little to the point I am trying to make, so I hope the informed reader forgives me this slight inaccuracy.

These debug events are delivered to the operating system as #DB exceptions. What type of event triggered the exception, can be identified by interpreting dr6.

To handle code that itself intents to modify the debug registers, the processor can be instructed to generate a debug event on every access of the debug registers. A debugger may then choose to emulate these accesses.

## 2.7 Summary

This chapter gave a brief overviews of the serial port, USB, PCI and continued with a more in–depth discussion of the Firewire bus. Following that, I described message-signaled interrupts and interrupt handling on the PC. The last part of this chapter focused on hardware support for debugging on the 32-bit Intel Architecture.

The next chapter concentrates on the approaches to remote system debugging and already existing debuggers using Firewire.

# 3 Related Work

"If you're not part of the solution, you're part of the precipitate."

Henry J. Tillman

The previous chapter discussed details of the Firewire bus and gave an overview about handling hardware interrupts on the PC platform.

This chapter discusses existing system debugging approaches. I introduce debuggers that have support for Firewire and argue how this relates to recent security threats that involve the Firewire bus. The ideas presented in this part give rise to the design of a remote kernel debugger that is presented in the next chapter.

# 3.1 Approaches to System Debugging

Traditionally, there have been several approaches to kernel and system debugging. This section presents the most popular ones with the intention to show the gap this work tries to fill.

#### 3.1.1 In-Circuit Emulator

One possibility to perform system debugging is to use an in–circuit emulator (ICE). ICEs come in many different types, such as bond–out processors, which expose additional pins to control execution and to allow access to internal signals and registers.

In any case, the ICE provides a controlling interface to another computer, the debugging host, running the ICE control software. In essence, it is a debugger built into the hardware.

ICEs are used, for example, in debugging embedded systems that lack resources or output devices to support a software debugger. ICEs are also available for commodity hardware, where they provide features that are out–of–reach for software debuggers, such as breakpoints on certain bus events [12].

Intel has a long history of in–circuit emulators that goes back to at least the Intel 80286 [13]. The 80286's ICE is actually quite interesting in the scope of this work. To generate a breakpoint on a specific event, the ICE control software on the host would monitor the 80286's bus, until a matching event occured. At this point, it signals the processor to stop execution and dump its internal state into a predefined memory location that the control software can inspect. The rough idea is similar to the design I propose in the next chapter.

ICEs are in many aspects superior to other choices, but their price is prohibitive for many applications.

#### 3.1.2 In-Kernel Debugger

A less expensive choice is to implement debugging functionality in the operating system kernel itself. An example of this, the Fiasco microkernel's debugger JDB, has already been discussed in the introduction. Another example is FreeBSD's kernel debugger.

The great advantage of this approach is that the debugger has direct access to all kernel data structures. Debugging commands, such as "send a signal to process n", are easily implemented.

One drawback in my eyes is that the line between kernel functionality and debugging functionality can become fuzzy. The debugger becomes an integral part of the kernel and most parts of it cannot be reused. It also adds code to the kernel, such as instruction decoding and parsing of debug information, that does not contribute to the main functionality of the kernel and contributes a maintenance burden.

Lastly, writing an in–kernel debugger is no small accomplishment and costs valuable development time not every project can spare.

#### 3.1.3 Remote Debugging

In addition to debugging applications that run on the same computer, the GNU Debugger can talk across a serial line or TCP connection to a debugging stub on another computer. This mode of operation is most useful when debugging operating system kernels and embedded systems where the stub is integrated in the kernel itself. Its key problems have already been outlined in the introduction:

While remote debugging is a workable alternative to an in–kernel debugger, it still adds considerable code to the kernel, because implementing GDB's remote protocol is not an easy task. Additionally, it relies on RS-232, a slow legacy communication channel that is not available in many recent PCs.

Using a debugger outside the kernel incurs loss of functionality. Certain operations, such as the "send a signal to process n" example above, become difficult, because they have to be expressed in the debugger's command language. If the command language is insufficient to express the desired action, the user is out of luck.

#### 3.1.4 System Emulator with Debugging Extensions

Virtual machines or emulated systems can be used for debugging as well. For example, the system emulator QEMU [8] implements a GDB stub in its emulation layer, which can be used to attach the GNU Debugger to an unmodified operating system. Thus, QEMU acts as a kind of primitive ICE in its emulated system.

This approach adds to the advantages of remote debugging that no kernel stub has to be developed at all, the slow serial connection to the target is replaced with a fast TCP connection from GDB to QEMU, and test machines can be comfortably started as QEMU processes.

Unfortunately, this solution is not applicable, when hardware devices are needed that the system emulator cannot emulate. Additionally, having an operating system work in an emulated system does not imply that it necessarily works on a real system.

The purpose of this work is to mitigate these last two disadvantages by providing a comparable debugging experience on real hardware.

## 3.2 Debuggers Using Firewire

The idea of using Firewire as a kernel debugging aid is not new. There are currently at least three major operating systems that provide support for Firewire as a communication medium for remote system debugging. Except for the FreeBSD implementation, documentation is either sparse or outdated.

#### 3.2.1 Windows' Kernel Debugger

One of the earliest implementations is in the kernel debugger of Microsoft Windows XP. Available documentation about the actual mode of operation is scarce, but indicates that the debugger on the host writes debug commands directly into the target's memory to be processed by the stub [18].

#### 3.2.2 FreeBSD's dcons

The dcons driver [27] is a console driver for the FreeBSD operating system that provides two in–memory communication ports. One is used for normal console in- and output, the other is a communication medium for the GNU Debugger.

These ports are implemented as memory buffers that can be read by either FreeBSD's kernel memory interface on the same machine or from a remote machine using Firewire. This interface is abstracted by the dconschat utility providing a uniform interface two both access modes. dconschat is able to open a TCP/IP server to allow connections from GDB or allow the user to access the remote system's console. The latter option also makes it possible to use FreeBSD's in–kernel debugger over Firewire.

dcons is fully integrated into FreeBSD since FreeBSD 6 and is actively supported.

#### 3.2.3 Linux' firescope and fireproxy

A slightly different approach [1] has been implemented for the Linux kernel. It is split into two tools:

- *Firescope* is a tool that reads arbitrary memory of a target system that runs Linux and is connected via Firewire. It is specially geared towards reading the remote system's kernel printk buffer, which contains the latest part of the kernel log.

- *Fireproxy* implements a GNU Debugger backend, but is very limited in the functionality it provides. It offers only remote memory access to the target, which allows to inspect kernel data structures. Controlling execution, inspecting registers, inserting breakpoints, and all other features of the GNU Debugger are not supported.

Development seems to have ceased in 2006 with both tools being left in a functional, yet experimental development stage.

#### 3.2.4 Limitations of These Approaches

The FreeBSD implementation uses Firewire as a fast communication medium for its GDB stub and its in–kernel debugger. From a pragmatic standpoint, dcons simply removes the need for a serial cable. It does not remove the need for either the in–kernel debugger nor the GDB stub in the FreeBSD kernel.

Firescope and Fireproxy exploit Firewire's remote memory access feature, but do not go beyond that. Firescope provides introspection into a running kernel but no means to manipulate its execution. Although Fireproxy uses the GNU Debugger as a frontend, it does not offer functionality that is commonly associated with debugging.

#### 3.2.5 Going One Step Further

The feature of directly reading and writing a computer's memory via Firewire has sparked a series of creative hacks with the aim of circumventing security features of the operating system [14].

An example is to use remote memory access via Firewire to change the user ID of a running process. After all, it is just a field in a kernel data structure. A normal process started by an unprivileged user can thus be elevated to superuser privileges.

Going one step further, it is possible to inject arbitrary code by overwriting code that is surely executed, such as the operating system's interrupt handlers. Although this offers great possibility for mischief, it is also a intriguing way to monitor and control execution of a computer from a remote system.

# 3.3 The GNU Debugger

GDB, the GNU Debugger, is the de-facto standard application debugger on most Linux-based and BSD-derived operating systems on various hardware platforms. It is a source-level debugger with excellent support for C, C++, Objective C, and to different degrees Fortran, Java, Pascal, Modula-2, and Ada [32]. GDB is free software protected by the GNU Public License.

GDB itself features only a command-line interface, which can be unwieldy for complex debugging tasks. For a more pleasant debugging experience the programmer can choose between a multitude of frontends to GDB.

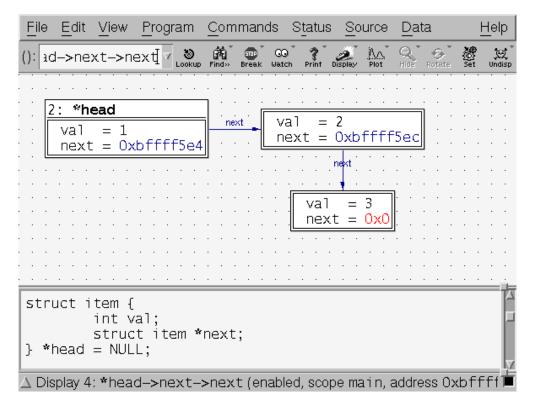

Personally, I appreciate GUD, the Grand Unified Debugger, which is a frontend integrated into Emacs, as well as DDD, the Data Display Debugger. The latter is a highly useful tool to graphically explore the structure of data in a running program [38]. Screenshots of example sessions can be seen in figures 3.1 and 3.2.

Although being written for application development, GDB has made its way into kernel debugging as well. Together with being free software, this makes GDB an obvious choice for this project.

```

ecl_gethash_safe (key=0x806ffd8, hashtable=0≯ ul

cl_object

<value optimized out→

(gdb) next

(gdb) next

cl_object

<value optimized out →

(gdb) next

ecl_fi<u>n</u>d_symbol_nolock (name=0x806ffd8, p=0x→

Bot L31 (Debugger:run -u:%* *locals of ecl* All L3

cl_object

ecl_find_symbol_nolock(cl_object name, cl_object p, int *intern_flaq)

cl_object s, ul;

name = ecl_check_type_string(@'find-symbol', name);

= ecl_gethash_safe(name, p->pack.external, OBJNULL);

(s != OBJNULL) {

*intern_flag = EXTERNAL;

goto OUTPUT;

Disp Enb Address

breakpoint

keep y

0xb7f914bd i≯

breakpoint already hit 1 time

-u:%* *stack frames of ecl* All L1 (Fram-u:%* *breakpoints of ecl* All L4

```

Figure 3.1: A screenshot of a source-level debugging session using GUD, an Emacs-based frontend for GDB.

Figure 3.2: A linked list in DDD. The screenshot demonstrates the advanced data exploration tools of DDD.

# 3.4 Summary

This chapter discussed the common approaches to system debugging. It continued describing uses of Firewire for remote debugging: FreeBSD's dcons driver uses Firewire as a fast communication medium to an existing in–kernel debugger. The Linux tools firescope and fireproxy use Firewire's remote memory access feature to inspect a running Linux kernel, but do not implement a full debugger. Other, more creative approaches that use Firewire to inject code and manipulate control flow are reported from the security community.

The next chapter will outline the design of a system debugger that combines both approaches to yield an uninstrusive remote system debugger that can be quickly retargeted to new systems.

# **4 A Framework in Three Parts**

"If we complicate things, they get less simple."

Professor at Cambridge University

So far I have only described technical details and the few existing related projects. I will now turn to the actual design of an unintrusive remote system debugger.

#### 4.1 Initial Considerations

There are certain ideas raised in the introduction that are worth repeating. I strongly believe that it is detrimental to the health of an operating system kernel to keep code in it that is maintained as a second–class citizen. A in–kernel debugger or debugging stub is usually such code. System programmers usually have better things to do than maintaining their tools.

A way to avoid this situation, at least regarding debuggers, is to move as much of the debugging infrastructure out of the kernel to be maintained separately. In effect, this makes the debugger and the kernel or system it is intended to debug separate projects. Bad quality on the part of the debugger might then frustrate developers, but has no direct implications on the quality of the kernel itself.

The question that immediately follows is: What do we really need inside a kernel to debug it remotely? The answer largely depends on what features the hardware provides. Since the olden days, we have had RS-232, a simple communication mechanism that was present on nearly every PC and is only now slowly disappearing.

RS-232 provides a bidirectional communication medium with minimal effort on the kernel-side. Operations that need to be performed on the target system have to be encoded as data packets and sent across the wire. A debugging stub on the target then decodes them, performs the desired action and returns a result. Basically, this is GDB remote debugging in a nutshell. Even if one replaces RS-232 with another communication medium, such as the USB Debug Port[6], the concept remains the same. Something inside the target kernel has to interpret these packets.

Taking a step back, let us consider what the essentials for remote debugging are. A remote debugger has to:

- *inspect* and *modify* the state of the target, which is divided into its memory and processor–internal state, such as registers, and

- control its execution.

Table 4.1 lists which of these essential operations each of RS-232, the USB Debug Port, Firewire, and PCI can perform *without cooperation* from the target system. RS-232 and the

|                     | RS-232 | <b>USB Debug Port</b> | Firewire   | PCI        |

|---------------------|--------|-----------------------|------------|------------|

| CPU register access | no     | no                    | no         | no         |

| Memory access       | no     | no                    | yes        | yes        |

| Execution control   | no     | no                    | interrupts | interrupts |

Table 4.1: Support, for remote debugging operations without support from the target. Interrupt injection via Firewire is not an obvious feature and is discussed in Section 5.2.1.

USB Debug Port do not provide any of the necessary features and have to completely rely on support code in the target kernel.

An interesting category is formed by Firewire and PCI. Both can:

- cache-coherently access the target's memory and

- signal interrupts.

However, a debugger cannot be built without support from the target, based solely on these capabilities. The target kernel has to be enhanced with a tiny debugging stub. But, given these capabilities, what really needs to be in the target kernel to facilitate remote debugging? Surprisingly, only two things are needed. The first one is a way to safely stop and resume execution of the system upon reception of an interrupt. The second one is a way to expose processor—internal state in memory, where it can be easily read remotely.

It is important to mention that such a kernel stub is completely agnostic about the way the debugging host performs remote memory access and interrupt execution. The stub does not need to drive any hardware devices. Given the fact that the debugging host can remotely access memory, the stub can even be injected into the target system at runtime.

On the following pages, I present a design of a remote system debugger based on these premises.

The implementation presented in the next chapter focuses—for practical purposes—on Firewire, but a custom–built PCI card or enhanced virtual machine monitor would work just as well, as would any device that can inject interrupts and remotely access the target's memory in a cache-coherent way.

# 4.2 The Bird's Perspective

Let me give you a quick overview of the design I propose, before I discuss the individual parts. At the top of the debugging architecture is the GNU Debugger. Reusing the GNU Debugger frees us from the daunting task of disassembling object code, parsing debug information, writing an user interface and generally from reinventing the wheel.

The GNU Debugger can be used unchanged in this framework. Any recent version is sufficient when it proves stable enough<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup> The GNU Debugger has been found to be quite instable in certain situations. Most notably when debugging functions written in Assembler and assembled using gas with debugging symbols enabled.

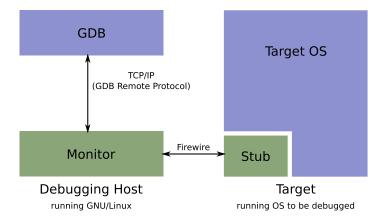

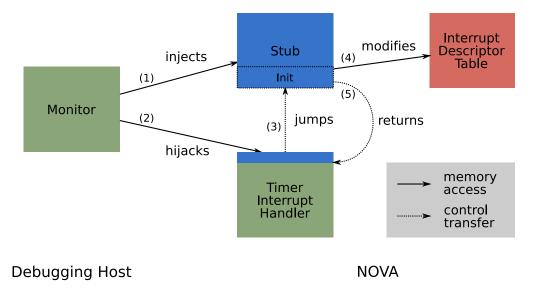

Figure 4.1: The three parts of the debugger framework: The GNU Debugger, the monitor, and a kernel stub in the target kernel. Firewire is used for communication.

Normally, the GNU Debugger uses a serial connection directly to the target machine. In our case, it connects to the *monitor*, another application running on the host, via a TCP/IP connection. The monitor's purpose is to interpret requests coming from the GNU Debugger and execute them using one of its backends, such as the Firewire backend, which I describe in more detail below. On the target system, a tiny kernel stub is needed to expose processor—internal state.

#### 4.3 The Monitor

The monitor acts as a server for the GDB remote protocol. It translates requests coming from the GNU Debugger via the TCP/IP connection into operations on its target.

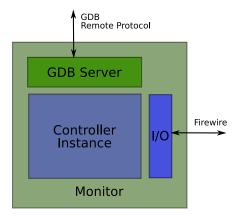

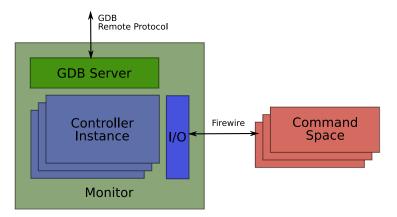

The design of the monitor focuses on reusability. It is implemented in three parts, which are shown in Figure 4.2.

### 4.3.1 The GDB Server

The first major part of the monitor is the GDB server, which implements a large part of the GNU Debugger's remote protocol. Details of the protocol implementation are addressed in Section 5.3.1 on page 34. Each request from GDB is executed by operations on the controller.

### 4.3.2 The Controller

The controller is the heart of the monitor. It abstracts the services provided by the target kernel stub into an easily usable interface. The major tasks that the controller abstracts are:

- Starting and stopping of the target using interrupts,

- · translating virtual into physical addresses,

Figure 4.2: The monitor consists of three parts: The GDB server implements the GDB remote protocol and manages communication with the GNU Debugger. The controller abstracts the capabilities of the target kernel stub. Lastly, an input—output layer hides the intricacies of the underlying communication medium, such as Firewire.

• accessing the target's register set.

The controller is intended to serve as a middleware between GDB requests and the kernel stub, but its interface is completely agnostic about the GNU Debugger and can be used not only as backend for other debuggers, but also for other types of applications as well. In Section 6.2, I describe a primitive statistical profiler, which is implemented using the controller interface, to assess the cost of monitor interrupts.

### 4.3.3 The Input-Output Abstraction

The low-level communication with the target is encapsulated to allow for different kinds of communication.

While the intended medium is a Firewire bus connected to a physical target system, it is also possible to implement this interface for a virtualized target running in a process emulator or a virtual machine. As most virtualization systems already facilitate debugging, the latter is mostly meant as a debugging vehicle for the debugging architecture itself.

By abstracting from the concrete type of communication to the target system, the controller and the GDB server can be agnostic about the communication medium and are presented with a clear interface that mirrors closely what is possible using Firewire, as it is the most restrictive medium.

An implementation of an input–output backend for the controller has to support only three methods:

- The read and write methods are used to read arbitrary chunks of physical memory on the target;

- the nmi method is used to interrupt the target with an non-maskable interrupt (NMI).

The Firewire implementation of these input-output methods is obviously the most straight-forward one, as the read and write operations map directly to Firewire primitives and nmi is implemented as a special write operation, as explained in Section 5.2.1.

Support for targets running in virtual machines is a bit more complicated, because at the time of writing no widely–used virtual machine emulates a Firewire device.<sup>2</sup> Fortunately, the same operations that are possible via Firewire can be directly implemented in the virtual machine monitor. An implementation for QEMU exists and is described in Section 5.3.3.

### 4.4 The Target Kernel Stub

Although much of the debugging functionality is moved outside the target kernel, a small kernel stub is still needed, but its complexity is extremely low. This kernel stub consists of an interrupt handler to handle interrupts from the monitor and is responsible for exposing processor-internal state and safely stopping and resuming the target kernel.

For the sake of simplicity, only uniprocessor systems are supported. Section 7.2 shows how this design can be extended towards multiprocessor systems.

### 4.4.1 Contexts in the Target Kernel

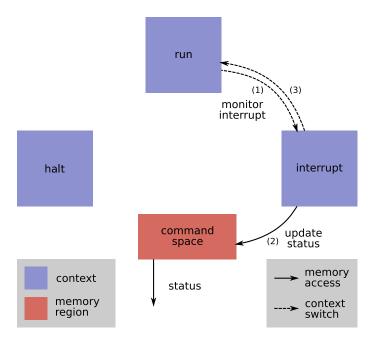

The functionality provided by the kernel stub is implemented using transitions between contexts. Contexts are execution states that are switched upon receiving an interrupt from the monitor or upon debug events. These contexts are completely orthogonal to what the underlying operating system may call context, process, or thread. The implementation of contexts is machine–specific. An implementation for the 32-bit Intel architecture is described in the next chapter.

The target kernel executes at any one time in one of three contexts.

- The run context is the one in which the kernel and user-mode applications are executed. The target system spends most of its time in it.

- The interrupt context is entered whenever the target receives an interrupt from the monitor.

- The halt context is entered either when a debug event occurs on the target system or directly when the interrupt context is told to stop execution.

The run context is special, because, whenever it is left, the current state of the processor must be stored in the command space, which I will discuss to below. When control returns to the run context, its state is restored from the command space.

### 4.4.2 Communicating with the Stub

As the monitor can only communicate using interrupts and memory accesses, a certain area of the target's memory, the *command space*, is used for communication. The command space serves two purposes.

<sup>&</sup>lt;sup>2</sup> Incidentally, shortly before finishing this work, an effort to implement a virtual Open Host Controller for QEMU has been started. At the time you are reading this, QEMU might be worth a second look.

Figure 4.3: The command space is logically divided into two parts: Processor state and status reported by the target and commands sent by the host.

First, it holds a status field and the processor state of the run context, which the monitor can modify via remote memory accesses. This state is updated synchronously on every interruption by the stub. Its second purpose is to communicate the desired action that the monitor wants to perform to the target. There are only two different types of actions required.

- The stop command is used to force execution from the interrupt context into the halt context.

- The resume command is used to resume normal execution in the run context.

On each interrupt, the stub updates the status field in the command space to indicate whether:

- the target was interrupted executing normally, that is in the run context,

- the target was sleeping in the halt context, or

- the target is halted due to an unrecoverable exception. This state is not recoverable and the target can most likely not be resumed.

The stub, as presented so far, suffices to implement a fully functional debugger, but the monitor would have to periodically send interrupts to recognize when the target has entered the halt context due to a debug event. Polling with interrupts is undesirable, because it wastes processor time on the target even when no interaction with the debugger is needed.

By adding a field to the command space that is asynchronously updated by the stub whenever the target system enters the halt state, the monitor can learn this information by a simple memory access and defer interrupting the target, until it is certain that it is stopped.

#### 4.4.3 Not Using a Ring Buffer

A major goal for the target kernel stub has been its utter simplicity. The current design uses an approach that reminds of a state machine with clear transitional events and states. The core logic can easily be expressed in one page of code and is robust even in the face of a crashing monitor. A new monitor can be started and can reattach to the running target without problems.

Using a ring buffer for communication was consciously avoided, because it would have required a producer–consumer approach, which is deemed unnecessary. A ring buffer requires careful synchronization and would have increased the complexity of the stub considerably.

The current design rests on the assumption that communication with the stub via interrupts is done infrequently. Operations, such as repeatedly stepping one instruction, violate this assumption and as consequence perform badly compared to other operations that require less interruptions (see Section 6.1.2).

For applications of the framework that suffer from this design decision it might be worthwhile to reconsider the decision not to use ring buffers.

#### 4.4.4 Halting and resuming the target

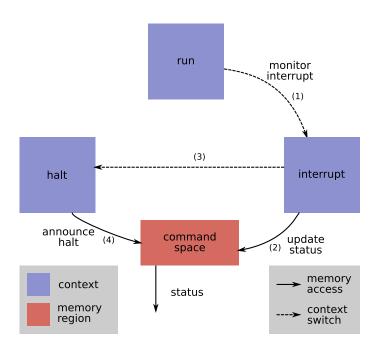

Figure 4.4: Halting the target is accomplished by forcing execution into the halt context.

To safely inspect the state of the target, it must be stopped. Figure 4.4 depicts the sequence of events that are initiated by the monitor to stop the target and obtain its state.

The monitor first issues the command to force the target into the halt context by writing it into the command space and then triggering an interrupt in the target. This causes the interrupt context to become active. The handler then updates the processor state in the command space and switches to the halt context where execution is caught in an idle loop.

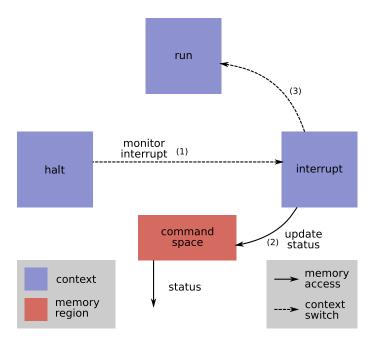

When the monitor is instructed to resume execution, a similar chain of events is started that is illustrated in Figure 4.5:

The monitor tells the stub to return to the run context in an analogous way: It includes the command in the command space and signals an interrupt. The stub then updates the command space and carries out the command, which is returning control to the run context.

Figure 4.5: Resuming execution in the target after being halted is done by forcing execution into the run context.

### 4.4.5 Handling Debug Events

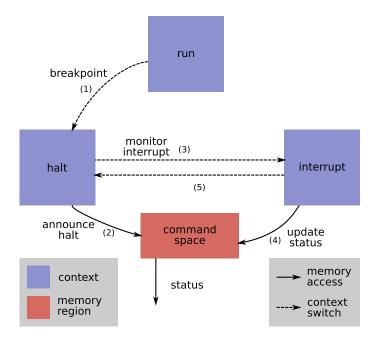

So far we have seen how to manually halt and resume execution of the target system. More interesting and useful are debug events such as breakpoints, watchpoints or processor exceptions.

If the processor architecture supports hardware-assisted debugging, the necessary interface is exposed via the command space. If the processor architecture lacks support for it, the monitor can inject code to achieve the same without involvement of the stub. How breakpoint injection is handled on the Intel architecture is explained in Section 5.2.4.

Debug events are handled quite different from manually halting the target. Upon encountering a debug event, the target switches to the halt context. Inside that context, it announces the occurrence of a debug event in the command space.

While the target system is running in the run context, the monitor polls the status field in the command space. When the command space indicates that the target has entered halt, the monitor signals an interrupt.

The interrupt causes a switch to the interrupt context, where the complete status information in the command space is updated. When the update is done, the target switches back to halt and sleeps again. The monitor can now pass control to the GNU Debugger, which figures out what caused the debug event on its own. Resuming the execution works exactly as explained in the previous section.

Figure 4.6: When a debug event occurs, the target switches to the halt context. The monitor detects this and extracts information via a roundtrip to the interrupt context.

# 4.5 Summary

This chapter presented an argument for a different approach to remote system debugging that relies on features provided by the Firewire bus. Building upon the GNU Debugger, a design was outlined that separates the debugger and the corresponding kernel stub from the system that is to be debugged. The next chapter will deal with implementation issues on the 32-bit Intel architecture.

# 5 Implementation

"What I cannot create, I do not understand."

Richard Feynman

In the preceding chapter, the generic design of a minimally intrusive system debugger was outlined. This chapter starts with a discussion of how the design maps onto real hardware and then go on to deal with the concrete implementation for two different kernels on the 32-bit Intel architecture.

# 5.1 The NOVA Microhypervisor

The main implementation and experimentation was done with the NOVA microhypervisor [33]. Its development has been started as part of the ROBIN project, whose goal was to develop a small, robust, and *open* operating system architecture for security–sensitive applications. The original project homepage can be found at http://robin.tudos.org/.

NOVA is an experimental hypervisor that allows running legacy guest operating systems alongside a multi–server user environment. A major design goal is to provide isolation for legacy systems and applications in order to limit the impact of a compromised component.

For the purposes of this thesis, NOVA makes an excellent testbed, because it is *small* and therefore easy to understand and modify. Furthermore, it currently implements neither a GDB stub nor an in–kernel debugger.

# 5.2 Mapping the Design onto the 32-bit Intel Architecture

There are several challenges with mapping the design, outlined in the previous chapter, onto commodity PC hardware, most of which deal with the kernel stub. The monitor itself arrives mostly as a consequence of design choices in the kernel stub and the perceived weirdness of the GNU Debugger's remote protocol. I will return to the protocol in Section 5.3 on page 34.

#### 5.2.1 Remotely Injecting Interrupts Using Firewire

I have been vague so far on how it is possible to remotely signal interrupts via Firewire. The key is creative use of features of the PCI bus and the OHCI.

Let me recapitulate some facts from Chapter 2. Section 2.5.1 mentioned that it is possible to program the OHCI in a way that allows it to pass Firewire bus requests directly to the PCI

<sup>&</sup>lt;sup>1</sup> I give full credit for this discovery to my thesis mentor, Bernhard Kauer. Without it, this work would not have been possible in this form.

bus. Section 2.6.1 explained that modern PCI devices can use special write transactions on the PCI bus to signal interrupts, so called message-signaled interrupts. The type of interrupt is encoded in this transaction.

Even if it seems almost ludicrous on first sight, it is possible to send a write request to a particular Firewire node, which is handed to the PCI bus by the node's OHCI, where it is interpreted as a message-signaled interrupt. All that is needed on the target, is a chipset that supports message-signaled interrupts and an enabled Advanced Programmable Interrupt Controller (APIC).

The format of message-signaled interrupts is quite elaborate [21], but for our limited purposes it suffices to interrupt the first physical processor with an NMI, which is done by simply writing the value 0x40 at the address 0xFEEE0000 in a node's Firewire bus address space. There is nothing more to it.

### 5.2.2 Handling Interrupts in the Kernel Stub

The design rests on the assumptions that the debugging host can signal interrupts and read arbitrary physical memory of the target. The implementation uses NMIs, because they cannot (easily) be masked by the operating system.

NMIs have traditionally been used for unrecoverable error conditions, such as failing hardware components, that have to be detected regardless in which state the operating system is. Nonetheless, safely handling NMIs on the 32-bit Intel architecture proves to be a challenge. There are basically two choices:

By using an *interrupt gate*—see Section 2.6.2 on page 11 for a brief discussion of interrupt handling—the operating system's current kernel stack is used to handle the interrupt. If the kernel has code paths without a valid stack, a delicate recovery in the handler is needed to avoid memory corruption.

The Linux kernel uses interrupt gates for NMI handling and has to recover, for example, when being interrupted directly after a system call. The recovery process employed by Linux to fix the smashed stack is intimately tied to code that might have been executing, when the interrupt was triggered, and is likely to frighten even experienced system programmers.

The second choice is to use a *task gate* to handle the NMI handler. On first sight, this solves all the aforementioned problems, because the CPU saves its state prior to the interrupt to memory and loads a new state including a new stack pointer for the handler procedure. Curiously, the task switch does not save two critical system registers (cr3, ldtr) whose contents get destroyed during the process.<sup>2</sup>

To safely resume execution, the interrupt handler must recover both registers prior to returning control. Fortunately, there are usually few places in a kernel that modify these registers. It is straight-forward either to deduce their contents from kernel data structures, when they are lost, or to keep shadow copies in memory.

The latter choice, using a task gate, is the one currently taken by the NOVA microhypervisor. However, NOVA goes only half the way and makes no attempt to restore the destroyed state, because it interprets NMIs as unrecoverable failure and deliberately panics.

<sup>&</sup>lt;sup>2</sup> These registers are termed 'static fields' in the TSS by Intel's system programming guide [21]. Static fields are restored when the processor switches to the corresponding task, but never written by the processor.

I favored the task gate approach to NMI handling for the debugging stub, because it has two pleasant properties. Using hardware task switching reduces kernel–specific fix-up code to restoring the content of the two destroyed registers, instead of a complicated restoration procedure, as employed by Linux. The second property is that the processor frees the kernel stub from the job of storing the processor state, because it is already written to the TSS.

### **5.2.3 Representing Contexts**

Because of the decision to handle NMIs with a separate hardware task, I decided to map contexts to hardware tasks. Each context—run, interrupt, and halt—is represented by its own hardware task.

Architectures that do not provide hardware-assisted task switching obviously need a different approach. The AMD64 architecture in its native 64-bit mode is one example of such an architecture. A possible implementation for AMD64 is outlined in Section 7.1.

## **5.2.4 Processor-Specific Parts of The Command Space**

The command space is divided into processor state reported by the target and commands sent by the debugging host.

#### **5.2.4.1** Commands

Three commands have been implemented. These are stop and resume, which were already explained in Section 4.4.2.

To implement hardware breakpoints, the processor debug register's need to be written by the monitor. These registers are currently not contained in the generic processor–state in the command space, because reading and writing them is slow compared to accessing the processor's general–purpose registers. A special command write\_dr was implemented for the purpose of updating the debug registers, which is only used when the user sets hardware breakpoints in the GNU Debugger.

During development, the stub had support for other commands, such as reading the debug registers. In theory, the contents of the debug registers indicate the type of debug event that took place. However, there seems to be no way to communicate that information to GDB, so support for this functionality has been dropped.

#### 5.2.4.2 Synchronization and Robustness

When the monitor sends an interrupt to the target, it has to wait until the interrupt handler on the target system has finished updating the command space.