L4.sec Implementation Kernel Memory Management

Bernhard Kauer

kauer@os.inf.tu-dresden.de

May 19, 2005

## Contents

| 1 | Introduction |                                 |    |  |  |  |

|---|--------------|---------------------------------|----|--|--|--|

| 2 | Fun          | damentals                       | 6  |  |  |  |

|   |              | 2.1.1 What is L4?               | 6  |  |  |  |

|   |              | 2.1.2 Minimal Basic Concepts    | 7  |  |  |  |

|   | 2.2          | L4.sec - New Concepts           | 7  |  |  |  |

|   |              | 2.2.1 Capabilities              | 7  |  |  |  |

|   |              | 2.2.2 Endpoints                 | 9  |  |  |  |

|   |              | 2.2.3 Kernel-Memory Objects     | 11 |  |  |  |

|   |              | 2.2.4 Summary                   | 13 |  |  |  |

| 3 | Des          | ign                             | 14 |  |  |  |

| • | 3.1          | Dependencies                    | 14 |  |  |  |

|   |              | 3.1.1 Examples                  | 14 |  |  |  |

|   |              | 3.1.2 Avoiding Cycles           | 16 |  |  |  |

|   |              | 3.1.3 Tree Walk                 | 17 |  |  |  |

|   | 3.2          | Locking                         | 18 |  |  |  |

|   |              | 3.2.1 Lock-Free Synchronization | 18 |  |  |  |

|   |              | 3.2.2 Atomic Lookup and Locking | 19 |  |  |  |

|   |              | 3.2.3 New Locking Scheme        | 19 |  |  |  |

|   |              | 3.2.4 Summary                   | 21 |  |  |  |

|   | 3.3          | Resource Dependencies           | 21 |  |  |  |

|   |              | 3.3.1 Map                       | 21 |  |  |  |

|   |              | 3.3.2 Copy vs. Grant            | 22 |  |  |  |

|   |              | 3.3.3 Copy Obsolete?            | 23 |  |  |  |

|   |              | 3.3.4 Summary                   | 25 |  |  |  |

|   | 3.4          | Unpinned UTCB Memory            | 25 |  |  |  |

|   |              | 3.4.1 What are UTCB's?          | 26 |  |  |  |

|   |              | 3.4.2 Implement UTCB's          | 26 |  |  |  |

|   |              | 3.4.3 Do we Need UTCB's?        | 26 |  |  |  |

|   |              | 3.4.4 Conclusion                | 28 |  |  |  |

|   | 3.5          | Summary                         | 28 |  |  |  |

| 4 | Imp          | plementation                    | 29 |  |  |  |

|   | 4.1          | Implementation State            | 29 |  |  |  |

|   |              | 4.1.1 Changes                   | 29 |  |  |  |

|   |              | 4.1.2 MDB: The Mapping Database | 30 |  |  |  |

|   |              | 4.1.3 Kernel-Memory Objects     | 31 |  |  |  |

|   |              | 4.1.4 IPC                       | 32 |  |  |  |

|   |              | 4.1.5 Testing                   | 32 |  |  |  |

|   |              | 4.1.6 Summary                   | 33 |  |  |  |

CONTENTS 2

|   | 4.2 | Simplify L4.sec                              |

|---|-----|----------------------------------------------|

|   |     | 4.2.1 The Initial Task $\sigma_0$            |

|   |     | 4.2.2 The Kernel-Interface Page              |

|   |     | 4.2.3 Double-faults                          |

|   |     | 4.2.4 A Unified Flexpage                     |

|   |     | 4.2.5 Summary                                |

|   | 4.3 | W5 - A Binding for L4.sec                    |

|   |     | 4.3.1 Motivation                             |

|   |     | 4.3.2 Requirements                           |

|   |     | 4.3.3 Virtual Registers                      |

|   |     | 4.3.4 Example: Short-IPC                     |

|   |     | 4.3.5 Conclusion                             |

|   | 4.4 | Summary                                      |

|   |     |                                              |

| 5 |     | luation 41                                   |

|   | 5.1 | IPC Performance                              |

|   |     | 5.1.1 Introduction                           |

|   |     | 5.1.2 Previous Work                          |

|   |     | 5.1.3 L4.sec Short-IPC                       |

|   |     | 5.1.4 Summary                                |

|   | 5.2 | Code Complexity                              |

|   |     | 5.2.1 Motivation                             |

|   |     | 5.2.2 Measurement                            |

|   |     | 5.2.3 Results                                |

|   | 5.3 | User-level                                   |

|   |     | 5.3.1 A Session Based Communication Protocol |

|   |     | 5.3.2 Kernel-Memory Management               |

| 6 | Sun | nmary 50                                     |

| U | 6.1 | Further Work                                 |

|   | 0.1 | 6.1.1 Design                                 |

|   |     | 6.1.2 Implementation                         |

|   |     | 0.1.2 implementation                         |

| A | App | pendix 52                                    |

|   | A.1 | Glossary                                     |

|   | A.2 | W5 binding                                   |

|   |     | A.2.1 Short-IPC                              |

|   |     | A.2.2 Virtual Register Mapping               |

|   |     | A.2.3 Numbers                                |

# List of Figures

| 2.1  | Capability example                                          |

|------|-------------------------------------------------------------|

| 2.2  | Capability permissions of different objects                 |

| 2.3  | An endpoint example                                         |

| 2.4  | Badge example                                               |

| 2.5  | Clans & Chiefs                                              |

| 3.1  | Dependencies for a task                                     |

| 3.2  | Dependencies for a first-level memory table (MT1)           |

| 3.3  | A directed dependency graph                                 |

| 3.4  | Old thread locking                                          |

| 3.5  | Named object locking                                        |

| 3.6  | Get a Locked Object                                         |

| 3.7  | Grant an object                                             |

| 3.8  | Copy an object                                              |

| 3.9  | One-way channels using a monitor                            |

| 3.10 | Mapping trees for high bandwidth one-way channels           |

| 3.11 | Change the root                                             |

| 4.1  | Kpage_allocable interface                                   |

| 4.2  | The new unified flexpage format                             |

| 5.1  | IPC partner lookup in L4.sec                                |

| 5.2  | Overhead for finding a receiver by a sender                 |

| 5.3  | Number of SLOC in FIASCOUX for the L4.V2 and L4.sec version |

| A.1  | Input parameters for Short-IPC                              |

| A.2  | Output parameters for Short-IPC                             |

## Chapter 1

## Introduction

L4 does not have a security model and hence needs one.

Hermann Härtig

Microkernels aim to build flexible, small and modular systems. The first generation of microkernels, like Mach [ABB+86], with its feature richness and size, did not achieve this goal. Mainly the poor performance of Mach's IPC was the reason for this. This performance gap was closed by a radically new design [Lie93]. The microkernel provides now only the minimal functionality, needed to build a whole system on top of it. This approach increases the IPC performance by an order of magnitude. L4 was the firs, of the so called second generation of microkernels, which use these design techniques.

DROPS, the Dresden Real-Time Operating System<sup>1</sup>, needs a real-time capable microkernel. The first L4 implementation was not suitable for real-time issues, therefore the L4 interface was reimplemented in FIASCO. FIASCO shows that real-time and performance can be combined. It closes the real-time gap by using better synchronization techniques [Hoh02].

Microkernel based systems are particularly suitable for security critical applications. They promise a small trusted computing base, due to modularity and small code size. Current L4 implementations have different security problems. Neither the kernel-resource management nor IPC control are implemented in a fast and reliable way. L4.sec tries to close this security gap.

This thesis is the first that evaluates, refines and implements the L4.sec ideas [PV05]. It is focused on the new kernel-memory management. The L4.sec ideas influence the whole kernel implementation and system design. Therefore they must be seen in the context of the overall system.

It is obvious that the result cannot be a complete implementation of L4.sec, due to the time-frame of this work. But this work could give an insight into the implementation problems and it should show, whether there are fundamental issues in the L4.sec ideas, which cannot be solved.

## **Document Layout**

This thesis is organized as follows. In the next chapter I provide the fundamentals of this work. This includes an introduction into the new concepts L4.sec adds to L4. In Chapter 3 I evaluate the consequences of the new kernel-memory management to the implementation of the microkernel. Chapter 4 shows a new system-call binding, parts of L4.sec that must not be implemented and other implementation details. In Chapter 5 I give an estimation of the Short-IPC performance overhead, which is introduced with L4.sec and the code complexity of the current implementation.

$<sup>^{1}</sup>$ A research project at the TU Dresden with the aim to support applications with Quality of Service requirements. See also the Glossary A.1.

Additionally I propose a user-level communication protocol and describe scenarios how the new kernel-memory management could be used. The last Chapter 6 closes the thesis with a summary and a suggestion of further work areas.

### Acknowledgement

First, I would like to thank Prof. Hermann Härtig for the opportunity to work on this project in the Operating Systems Group at the TU Dresden and for the time to discuss problems with him. My special thanks go to my supervisor Marcus Völp for the long clarifying design discussion and the time he sacrifices to teach me how to write a theses. Dietrich Clauss deserves many thanks to introducing me into FIASCO coding. I would also like to thank to everyone in the group who discuss ideas or give hints, which helps me to enhance this work. Thanks goes to Johannes Kauer, Franziska Gräbe, Marcus Völp and Dietrich Clauss for there valuable feedback while proofreading the thesis.

Finally, many thanks goes to my family for the possibility to study in Dresden and for their constant support all the time as well as to my friends for their encouragement. I cannot enumerate them all and give therefore only an abbreviation here:

$JFMJBFAM^{+}WHFJLKSG.$

## Chapter 2

## **Fundamentals**

In this chapter I briefly describe the L4 model and the new concepts introduced with L4.sec. This description of L4 could not give a complete view. Please take a look for a deeper insight into L4 at the reference manuals [DLSU04, PV05] and the websites [TUD, HQL]. If you are familiar with L4 you can skip the next section and continue with section 2.2.

#### 2.1 L4

The determining criterion used is functionality, not performance.

Jochen Liedtke

#### 2.1.1 What is L4?

L4 is a microkernel interface of the second generation initially developed by Jochen Liedtke [Lie95]. He also wrote the first implementation for x86 in assembler. Since that time the L4 interface is implemented several times [TUD] in high level languages like C or C++ and ported to different architectures (e.g., Alpha, ARM, MIPS).

The philosophy of L4, to provide only minimal concepts and that functionality, not performance should be the criterion to decide what is implemented in the kernel [Lie95], is one of the reasons of the success of L4.

The interface was enhanced from the original L4.V2 [Lie96], to the L4.X0 [Lie99] and finally to the L4.X2 [DLSU04] API. L4.sec is the latest L4 interface.

#### **Fiasco**

FIASCO [Hoh98] is an implementation of L4 in C++ and assembler written at the TU Dresden by Michael Hohmuth and others. It is fully preemptible and it has therefore excellent realtime properties. Until now FIASCO supports the L4.V2, L4.X0 and L4.X2 API's and it runs on native x86, ARM [War03] and as user-mode program on Linux, which is called FIASCOUX [Ste02].

Only parts of the Fiasco code could be reused (see Section 5.2.3), but even so it was the base for implementation of this work.

#### FIASCO Portings

The former portings of FIASCO to other architectures, like IA64 [War02], FIASCOUX [Ste02], ARM [War03], or to other API's like L4.X2 [Cla04] are not directly comparable to this work for the following reasons. First, they used a fixed L4 specification, for which other implementations existed. Second, they did not change the kernel memory management in such an extensive way

and could therefore reuse much more code. However, they modularize most parts of FIASCO, which helps this work to reuse basic functionality of FIASCO.

#### 2.1.2 Minimal Basic Concepts

L4 provides only a minimal set of abstractions or basic concepts. These concepts are:

#### Virtual Address Spaces

The microkernel protects virtual address spaces from each other with the help of the *hardware* paging mechanism. Pages can be map'ed from one address space to another. This mapping can be recursively revoked by unmap. A task is an entity that consists of an address space and of threads running in them. Initially all available physical memory is available to the first task, which is called  $\sigma_0$ .

#### Threads

Threads are the activities in the L4 system running in tasks. They execute user-level code and can communicate with each other through IPC.

#### Inter-Process-Communication (IPC).

IPC in L4 is synchronous and unbuffered. It is used for message transfer, mapping pages and synchronization of different threads. IPC can be used within and across tasks.

In previous papers unique identifier for threads are also mentioned as a basic concept for L4. This is not important anymore, because in L4.sec threads and other objects have only local names (2.2.1).

### 2.2 L4.sec - New Concepts

Any problem in computer science can be solved with another layer of indirection.

David Wheeler

The main reason for further development of L4, like the name of L4.sec suggest, was the lack of security. There was no fast way to implement information flow control and no way to manage the kernel memory a task consumes.

To solve the problems of previous versions L4.sec introduces some new concepts to be able to implement efficiently fine-grained access control (capabilities), multi-threaded servers (endpoints) and kernel-memory usage control (kernel-memory objects).

#### 2.2.1 Capabilities

The most important improvements to L4 are the introduction of capabilities. In short, capabilities are references to kernel objects with permissions attached to them. Local names in a task local capability space translate to capabilities.

#### Kernel Objects

There are two types of kernel objects: named first class objects and unnamed second class objects. Named objects are threads, tasks, endpoints<sup>1</sup>, kernel-memory objects <sup>2</sup> and CPU reservations<sup>3</sup>. Unnamed objects are mapping-nodes, page and capability tables and a couple of static kernel objects, which are only created initially at startup<sup>4</sup>.

$<sup>^{1}</sup>$ See section 2.2.2.

$<sup>^2</sup>$ See section 2.2.3

<sup>&</sup>lt;sup>3</sup>The scheduling model based on reservations is preliminary and not part of this work.

$<sup>^4</sup>$ e.g. the idle thread, IRQ threads, boot time allocators, . . .

Capabilities point only to named objects. Unnamed objects are created indirectly and have no user-visible name.

#### **Local Names**

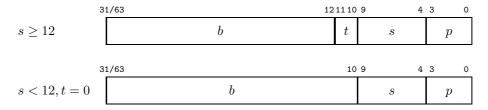

Capability ID's are task local and build an own namespace, the capability namespace, which provides a mapping between numbers and capabilities. Capability namespaces can be populated by

- creating new named objects through the create system-call, or by

- mapping the capabilities from one capability space to another.

Extending the recursive construction of namespaces through map from the memory space to the capability space also means that the corresponding unmap system-call can be used in the same way. This means the object is destroyed after the removal of the last capability<sup>5</sup>.

A task in L4.sec has beside the memory namespace (virtual address space) and IO namespace [Stö02], also a capability namespace. Since every thread can create new objects in its task<sup>6</sup>, there is no global view over all kernel objects. This is different to the memory namespaces where  $\sigma_0$  knows all physical pages. However  $\sigma_0$  in L4.sec knows the resources for all kernel objects.

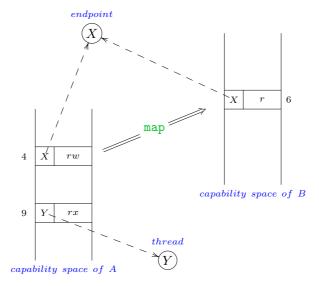

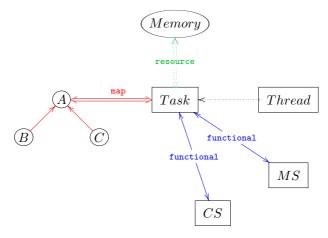

Figure 2.1: Capability example

In Figure 2.1 a task A has two capabilities in its capability space, located at the capability ID "4" and "9". The first points to the endpoint X and the second to the thread Y. The task A has mapped the endpoint capability without the write permission to the capability space of B. The task B can refer to X with its own capability ID "6".

#### Permissions

A capability contains 4 bits used as permissions. This allows to implement a simple rights scheme adopted from virtual page permissions. The semantics of the 4 bits depends on the type of object the capability points to. For example, write permission on a thread allows to modify thread state through ex\_regs or thread\_ctrl. Write permissions on an endpoint allows to send to them. See table 2.2 for details<sup>7</sup>.

<sup>&</sup>lt;sup>5</sup>This is the root capability in the capability space of the creating task, because capabilities can only be map'ed.

<sup>&</sup>lt;sup>6</sup>Provided that the task has enough kernel memory.

<sup>&</sup>lt;sup>7</sup>Note that it includes the changes of this work.

| Object       | Name        | Description                         |

|--------------|-------------|-------------------------------------|

| Thread       |             |                                     |

|              | read        | thread state is readable            |

|              | write       | thread state is writeable           |

|              | schedulable | reservation could be attached       |

| Endpoint     |             |                                     |

|              | recv        | messages could be received          |

|              | send        | messages could be send              |

|              | map         | mappings could be transfered        |

| Task         |             |                                     |

|              | bind        | threads could be bound to this task |

| Reservation  |             |                                     |

|              | read        | reservation state is readable       |

|              | write       | reservation state is writeable      |

| KernelMemory |             |                                     |

|              |             | to be defined                       |

Figure 2.2: Capability permissions of different objects

#### 2.2.2 Endpoints

To be able to send to one thread in a group of threads endpoints are introduced in L4.sec. Beside this L4.sec replaces the Clans & Chiefs model with a faster one.

#### What are Endpoints?

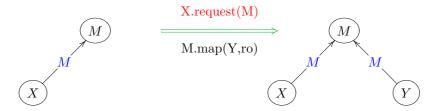

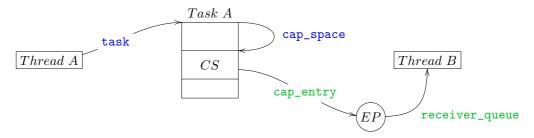

Endpoints could be seen as an abstraction for communication channels and they are used as rendezvous points for IPC. Instead of sending directly to a given thread or receiving directly from a thread, the IPC is performed over an endpoint.

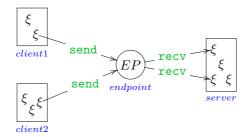

An endpoint is a named kernel object which could be created and mapped into a capability namespace. It could be used from many threads across task boundaries and therefore it is used as unidirectional channel. For example in Fig. 2.3 a group of client threads are sent to an endpoint where a group of server threads are wait for the requests of clients. If a sender arrives at the endpoint the kernel selects one of the waiting receivers and performs the IPC between them. If no receiver is found the sender waits at the endpoint for them.

Figure 2.3: An endpoint example

An endpoint hides the thread structure of the server. It allows to dispatch incoming messages to worker threads without the need of a dispatcher thread.

The send permission of the endpoint capability is checked when sending and the receive permission when receiving from the endpoint. The map permission is used to restrict the propagation of capabilities and pages. If it is missing mapping is not allowed over the endpoint.

#### Sender Identification

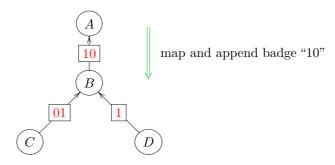

Since many clients could send messages through an endpoint to a single server, a mechanism to distinguish different senders is needed. Therefore L4.sec introduces the sender ID. The sender ID is a bit string returned by a receive. The prefix of it, known as the badge, is part of the capability of the sending endpoint. The suffix can be specified by the sender at every IPC.

The badge cannot directly be modified. Instead, an additional bit string can be appended. This addition can be done during the mapping of an endpoint capability. This restriction allows to protect the first bits of the sender ID.

Figure 2.4: Badge example. A could send with every sender ID, B could send only with sender ID's starting with the bits "10", C could send only with "1001", and D could send only with "101".

The kernel does not associate any semantics with the sender ID. It is up to the user-level servers to define their usage. For example, parts of the sender ID could be used as session identification and other parts could be used to distinguish different server functions.

#### Replacement for Clans & Chiefs

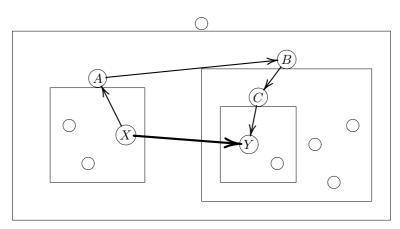

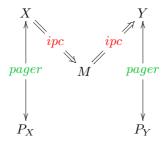

Clans & Chiefs [Lie96, Lie92] are a security concept initially developed by Jochen Liedtke for L3, the predecessor of L4. A clan (denoted as an rectangle in figure 2.5) is a set of tasks (denoted as circles) headed by a chief task. If a message tries to cross a clan boundary, the message is redirected to the chief of the clan. The chief could use any security policy to decide whether the message should be forwarded to the destination or not.

Figure 2.5: Clans & Chiefs are not fast enough. Every message between X and Y must be sent through A,B and C in this scenario.

In most L4 implementations Clans & Chiefs are not implemented because they are simply not fast enough. Crossing a single clan boundary for example doubles the time for the whole message transfer, since 2 IPC's<sup>8</sup> are needed instead of one direct IPC. This overhead must be payed for every message crossing a clan boundary, thus Clans & Chiefs are in practice unusable<sup>9</sup>.

Beside the performance limitation the Clans & Chiefs concept has also a fundamental problem: it changes the IPC semantic [JTG<sup>+</sup>00]. If IPC at the sender site returns with no error, it does not mean that the intended receiver got the message. This only mean that a chief received it, which in fact makes IPC asynchronous.

IPC between tasks could be controlled in L4.sec by the presence or absence of a local name for an endpoint. If two tasks do not have capabilities (with the appropriate permissions) pointing to the same endpoint they cannot communicate which each other. Since initially only the creator of a task has a endpoint to the task, it can control which other endpoints are mapped into and out of this task. This role of the task creator is similar to that of the chief of a clan.

Capabilities introduce an initial overhead because establishing an endpoint between two tasks is expensive, but it must be paid only once. There is also an overhead for every message due to the indirection of the local names and the check for permissions. These costs of capabilities should be much smaller then the forwarding costs of Clans & Chiefs.

#### **IPC** Redirection

The idea of IPC redirection is presented in [JEL<sup>+</sup>99]. The kernel maintains a redirection function that decides for every (*src*, *dest*) pair of thread ID's, the new destination of the IPC. The IPC is redirected to this new destination. Because global thread ID's build a sparse namespace, they use an inverted page table (hash table) for the lookup.

In contrast to capabilities they use global thread identifiers instead of local names. Capabilities avoid the problems of hash collisions. The capability space is dense, so a simple array lookup can be used, which should decrease the average lookup time.

#### 2.2.3 Kernel-Memory Objects

Kernel-memory objects are a solution to manage and limit kernel memory from the user-level.

#### What is Kernel Memory?

Kernel memory is the memory the microkernel needs itself to provide its service. Its integrity and availability is protected by the kernel and it is limited at least by the available physical memory. Kernel memory could be for example memory for kernel code, for pagetables of a task, for thread control blocks (TCBs), or mapping nodes, which store map dependencies.

There is no way to recover from situations where not enough kernel memory exists. Blindly destroying tasks, like Linux it does, is not a choice. Thats why the *consumption* of kernel memory must be controlled to build a secure system, where not all tasks have to be trust each other.

In summary kernel memory is a limited resource and it must be possible to restrict its usage.

#### **Current Handling**

In previous L4 versions a fixed quantum<sup>10</sup> of physical memory was reserved at startup for kernel memory. If it is exhausted the system is stopped<sup>11</sup>.

In L4.X2 only a a privileged task can create threads and tasks. Thus the main focus of kernel memory management in L4 is on mapping nodes and the corresponding pagetables. The reason

<sup>&</sup>lt;sup>8</sup>From the source to the chief and from the chief to the destination.

$<sup>^9</sup>$ Jochen Liedtke's argument "crossing clan boundaries occurs seldom enough in practice" does not hold, because many clans must be crossed - in the extreme case one per involved task - to implement fine-grained access control.  $^{10}$ usually 10 percent

Asking a privileged task, like  $\sigma_0$  or  $\sigma_1$ , for more kernel memory was never used, at least not in FIASCO

for this is, that mapping is bound to IPC, an unprivileged system-call, which every thread could execute.

By mapping a single page multiple times in its own memory space every task could occupy<sup>12</sup> kernel memory. Therefore mapping into the own address space is forbidden in L4.X2, but this attack could be easily launched with another cooperating address space if they could communicate with each other.

Bounding the restriction of kernel memory for mapping nodes to IPC control is inflexible, since every message which could contain a mapping must be monitored. Also it is hard to monitor the destruction of mapping nodes resulting from unmap calls. Additionally the current approach forbids combining different untrusted servers in one address space and the implementation of multi address-space servers.

#### User-level Management of Kernel Memory

In [HE03] parts of the kernel memory could be exported to user-level. If an operation in the kernel needs kernel memory, a fault is send to a *kpager*. The *kpager* maps a page to the kernel and could later unmap the page. On unmapping a kernel page, the kernel memory on this page is converted to a secure external representation and given back to the *kpager*. The external representation could be used later to reestablish kernel objects that were previously allocated in this page. This is contrary to our model where the objects are simply destroyed, if a kernel-memory object is unmapped.

This model could be seen as a memory mapped interface, where a *kpager* could call many system-calls in one step on behalf of another thread. It allows to page kernel internal data, but it has the disadvantage that dynamic data like running- or sender-queues and security critical information like scheduling parameters could not be exported.

I have to conclude that the kernel memory problem was never really solved in L4.

#### **Quota Systems**

A simple quota system ("Task X could use 4 pages of kernel memory") could restrict the kernel memory usage. Initially  $\sigma_0$  or another privileged task has all kernel memory and can give parts of it away to other tasks.

The main disadvantage of quotas is that they only allow to restrict but not to manage kernel memory at user-level. The placement of new objects in kernel memory of a task cannot be controlled. Therefore the kernel cannot determine which objects should be destroyed if the quota of a thread is reduced below the used amount. Beside this, implementing cache coloring of kernel memory on top of the microkernel is not possible. Also a simple quota system does not allow to distinguish between different kernel memory pools with different priorities or replacement strategies. A server for example does not want to lose the main thread but could perhaps tolerate that worker threads or client mappings get destroyed if there is not enough kernel memory available.

In summary a quota based solution cannot handle overload situations and the controlled reduction of the used kernel memory.

#### The Idea

The idea behind kernel memory management in L4.sec is that ordinary user memory can be given to the kernel and can be reclaimed at anytime. L4.sec introduces therefore a new named object: the Kernel-memory object that represents memory to be used by the kernel as backing store for all dynamically created kernel objects.

Kernel-memory objects are created by converting a flexpage  $^{13}$  from a user memory-space into a kernel page in the kernel memory-space. Afterwards the flexpage cannot be read or written from user-level anymore. The permissions are preempted. Threads that perform an system-call,

$<sup>^{12}</sup>$ In Fiasco up to 4 MB for  $3*2^{18}$  mapping nodes and up to 3 MB for corresponding page-tables

<sup>&</sup>lt;sup>13</sup>See the glossary A.1 for a description.

which needs kernel memory, can provide it by a capability pointing to a kernel-memory object. For example to create new objects (threads, endpoints, ...) or to map from one namespace into another (mapping nodes and pagetables) a thread specifies a kernel-memory object in which the kernel allocates the TCB, an endpoint structure, the mapping nodes, or the page tables respectively.

A kernel-memory object is destroyed if the last capability pointing to it is unmap'ed or if the flexpage in the memory space of the creating task, is unmapped. Destroying a kernel-memory object reconverts the flexpage and deletes all objects allocated within it. The preempted permissions of the flexpage in the user memory-space are restored.

#### **2.2.4** Summary

L4.sec promises to solve the security problems of previous L4 versions. It introduces some simple but powerful new concepts. Instead of passing the security critical functions to some privileged servers, it extends the hierarchic model of user memory management to kernel memory. In the same way IPC control is not bound to a single entity but can be distributed over the whole system. This work shows the feasibility and the consequences of the new concepts.

## Chapter 3

## Design

Kernel resources are handled in L4.sec quite different than in prior L4 versions. Mainly the *convert* of user memory into kernel memory and back, which is done by creating and destructing kernel-memory objects, has a deep impact on kernel design and implementation. In the following chapter I discuss the consequences of this fundamental change.

### 3.1 Dependencies

New kernel-memory handling is needed when creating new objects, when mapping from one space into another and when deleting kernel objects during an unmap system-call. The first two operations affect only a single object. The last operation - the deletion - affects a whole tree of objects, because deleting an object requires deleting all dependent objects. This requirement is obvious, since it assures that every object can be deleted and that no non-functional object remains.

There are 3 types of dependencies an object can have in L4.sec:

- 1. resource dependency Who provides the resources with which the object is built?

- 2. functional dependency What needs this object to work?

- **3.** map dependency Where is it mapped?

#### 3.1.1 Examples

In the following, I give two examples for a better understanding of these dependencies.

#### Task Dependencies

Figure 3.1 shows the dependencies of a task object. A kernel-memory object provides the memory for the task-control block (resource dependency). The capability space (CS) and memory space (MS) are examples for functional dependencies. Without them, a task cannot exist and vice versa. These two-way dependencies are cycles in the graph.

Because a task is a named object and is therefore always mapped into a capability space, there exist also a map dependency. Here is also a cycle between the root mapping-node and the task object, because they can both only live together. This is not the case for child mapping nodes, because the dependency between them and the named object is divided into a dependency to the root mapping node and the dependency from the root to the object.

The dependency between a task and the threads, which run in them, can be called as a weak functional dependency. A thread needs a task in L4.sec to be runnable. But it is only stopped and not destroyed if the task gets deleted.

Figure 3.1: Dependencies for a task

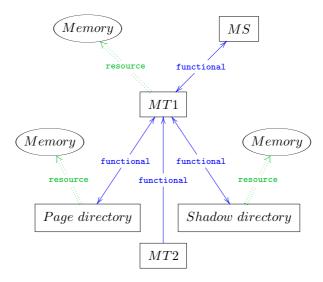

Figure 3.2: Dependencies for a first-level memory table (MT1)

#### Memory Table Dependency

Figure 3.2 is another example for the three mentioned dependencies. It shows the dependencies for a first-level memory table (MT1). This is an object which manages a page directory and a shadow directory.

The memory table is an unnamed object. Therefore, there is no map dependency since no mapping nodes point to it. MT1 is part of a memory space and can itself point to many second-level memory tables<sup>1</sup> (MT2). The former is a two-way functional dependency. The later is not, because memory spaces always have a first-level memory table but a MT1 needs not to have a MT2. Other functional dependencies point to the page directory and shadow directory. These are two-way dependencies, because both cannot exist without the memory table and the MT1 needs them too.

The resource dependencies are the kernel-memory objects in this example, which provide the memory for the MT1 itself and for the page and shadow directory.

<sup>&</sup>lt;sup>1</sup>assuming at least a two-level page table here

#### 3.1.2 Avoiding Cycles

The dependencies of all objects build a graph. Because a deletion needs to traverse the graph, it should be cycle-free. Cycles in these graph could lead to deadlocks if locking is used and additional resources of time and memory are needed to break them. Therefore I conclude:

#### • The graph has to be cycle free.

As shown in the examples, the resource dependencies have no cycles. This is because to create an object, the object resources must already be available. The functional and the map dependency can be two-way dependencies, which are in fact small cycles. How can these cycles be avoided?

#### Binding

There is only a weak functional dependency between a task and a thread running in them, as the task example shows. These dependencies come from the fact that L4.sec allows binding threads to a task. If this is not the case and the task is destroyed when the last thread dies, like in L4.X2, this would be a two-way functional dependency. Therefore I conclude:

#### • Explicit binding avoids cycles.

#### Collocation

Explicit binding is only possible with first-class objects, which have a name so that they can be individually addressed. Since an object get its name from a root mapping node, binding is not suitable to solve the cycle in a map dependency.

This map dependency has the problem that someone could do an unmap of the root-mapping node and another one could unmap the kernel-memory object in which the named object is stored. Both operations have to delete two objects: the root-mapping and the named object itself.

The cycle between the two objects can be avoided if they are only a single object. If the named object contains the root mapping-node the cycle is gone. This collocation could be implemented using class inheritance<sup>2</sup>. In summary I conclude:

#### • Collocation avoids cycles.

#### Redirection

There are cases where collocation is not possible. For example a page directory, like it is shown in the memory table example, cannot be collocated with the first-level memory table, since it needs a whole page itself.

That a MT1 needs a page directory and vice versa is a problem if the first is deleted coming from the memory space and the later coming from the kernel-memory object, which holds the page-table. Another problem with page tables is, that there is not enough space to store the pointer to the memory table.

This leads to the idea that the kernel-memory object could store the pointer to the memory table. If the kernel-memory object is deleted, it can now redirect the delete sequence directly to the memory-table. The page directory is now only deleted from the MT1. The kernel-memory object never destroys them anymore. Therefore I conclude:

#### • Redirecting a dependency avoids cycles.

<sup>&</sup>lt;sup>2</sup>The named object could be a derived class of the root mapping-node.

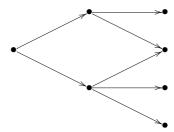

Figure 3.3: A directed dependency graph

#### **Summary**

In summary, cycles in the dependencies can be avoided by:

- explicit binding,

- collocation through class inheritance or

- redirecting dependencies.

Which of them can be chosen for a single case, depends on the involved objects. The current implementation shows that these three ways are sufficient to avoid all dependency cycles.

#### 3.1.3 Tree Walk

The dependency graph is directed if there are no cycles. Figure 3.3 shows such a directed graph. Unmapping a single object means to start at a particular node in the graph and delete all objects which can be reached through it. If a depth-first deletion is used, this walk is the same as walking through a tree. It does not matter that an object can be reached through many parents. It is visited only once, since it is deleted and all dependencies are removed after that<sup>3</sup>. Therefore I conclude:

#### • The delete sequence is a tree walk.

Iterating or walking through a tree is a commonly known problem in computer science. But what are the requirements this operation must have?

#### Fixed Memory Usage

The kernel gets additional memory only from applications. If a task wants to unmap kernel objects, because it is out of kernel memory, it cannot provide additional memory for this operation. Therefore the deletion of objects must occupy only a fixed amount of kernel memory, independently of how many objects have to be deleted. In summary:

• Only a fixed amount of kernel memory can be used.

#### Recursive vs. Iterative

The simplest way to walk through trees is recursive. To implement a recursive walk, only the next children have to be provided, the return path is stored on the stack. Since the depth of the object trees only depends on the available memory, recursive deletion is not applicable, without the waste of having a very big stack. Therefore an iterative solution have to be used.

For the iterative tree walk a back pointer for every node is needed, like for a recursive one, otherwise the return path cannot be found. Because the back pointers cannot be stored on the stack, they have to be stored in every node itself. I conclude:

#### • It must be an iterative tree walk.

$<sup>^3</sup>$ Removing all dependencies is a locking problem, since the dependency tree has to be consistent at any time. Therefore this must be done atomically with respect to other graph traversing operations.

#### Abort and Preemptible

Unmapping a kernel-object tree is a long-running operation, since the number of objects that are deleted is only limited by the available kernel memory. For application programming it is a plus, if long running operations can be aborted. Beside this, there are cases where the kernel has to abort an unmap. For example, the deletion of the own thread is not allowed and it results in an abort of the operation<sup>4</sup>.

A long-running operation can be a problem for the interrupt latency, which is a key factor for good real-time properties of a system. The unmap operation can therefore not be done in an atomic step. Instead, it must be possible to interrupt the operation and continue the work later. So I conclude that beside the possibility to abort an unmap, the operation must be preemptible.

The consequence of an abortable and preemptible unmap is that the object tree must be consistent at every time the operation is interrupted. Therefore the deletion cannot be executed in preorder, but it has to be done in postorder, as shown in [Voe02]. In summary:

• The unmap operation must be abortable and preemptible.

#### **Summary**

The deletion sequence has to

- use a fixed amount of kernel memory,

- must be an iterative tree walk, which is

- abortable and preemptible.

## 3.2 Locking

One consequence of user manageable kernel memory is, that kernel memory is no longer typestable. The user can for example create a thread and reuse the same memory after destroying the thread to create a task or an endpoint. The kernel cannot assume with L4.sec that a particular virtual or physical page holds the same type of object anytime.

This consequence changes the way locking has to be implemented. There is no proof that fine granular locking, which is a base for good realtime properties as FIASCO shows, can be implemented in L4.sec.

First I describe why lock-free synchronization cannot be used anymore and that lookup and locking must be done atomically. After that I outline a locking scheme for L4.sec. Since this scheme is not implemented until now, this can only be a rough design.

#### 3.2.1 Lock-Free Synchronization

In [Hoh02] Michael Hohmuth writes:

Preconditions for using lock-free synchronization are that primitives for atomic memory modifications are available and data is stored in type-stable memory.

The first precondition is a hardware property and is therefore independent from L4.sec.

The second precondition does not hold with the new kernel memory management. Therefore we have to conclude that lock-free synchronization cannot be used anymore to synchronize object usage and destruction.

However if another lock assures that the object is not deleted and therefore does not change its type, lock-free synchronization could be used on top of it.

$<sup>^4\</sup>mathrm{See}$  section 4.2.3

CHAPTER 3. DESIGN 19

```

Thread *dst = lookup (regs->dst());

// do something

Lock_guard <Thread_lock> guard (dst->thread_lock());

// do more

```

Figure 3.4: Previous code does thread lookup and locking not atomically.

#### 3.2.2 Atomic Lookup and Locking

Since the type of memory a pointer references can change, the usage of an object has to be locked against deletion. This means *lookup and locking must be atomically*, a property which previous FIASCO code is missing. I show this in the following for locking threads.

#### Thread Lookup

The lookup of a thread in previous L4 versions was simply calculating a thread pointer from the thread ID. Since thread ID's are specially designed for this case only arithmetic operations have to be executed<sup>5</sup>.

#### Old Thread Locking

Figure 3.4 shows a typical usage of thread lookup and locking in FIASCO. In L4.sec the thread pointer could be invalidated until the lock is grabbed, since both operations are not done in an atomic step. Even the thread pointer is sometimes used between lookup and locking. This is only correct with the assumption that the type of the memory never changes. Because the assumption does not hold with L4.sec, this code cannot be reused.

#### 3.2.3 New Locking Scheme

A locking scheme for L4.sec have to protect in-kernel data structures mainly named objects, mapping nodes and perhaps other unnamed objects.

#### Generation Numbers?

One idea to detect type changes in type-unstable memory was the usage of generation numbers. They could be used to track the creation and deletion of objects at page-table, page and object level. Due to its complexity and overhead (they have to be checked at every object usage), it seems that they are not practicable and therefore they are not on further focus. Instead the concurrent usage and deletion should be serialized through locks.

#### Locking of Named Objects

Named objects, like threads, tasks, kernel-memory objects or endpoints, are referenced by the user through capability ID's. These capability ID's are used to lookup the corresponding object in the capability space of its task. Fig. 3.5 shows how object lookup and locking, provided by a get\_obj function, can be used.

Every named object has a helping lock, which is set during the lookup. Because these lookup must be protected with a global lock<sup>6</sup> from concurrent deletions, the lookup and locking is done atomically. This operation can be implemented as a lookup and a try-lock. If the lookup failed or

<sup>&</sup>lt;sup>5</sup>Mainly anding a mask, shifting it and adding the offset of the TCB area.

$<sup>^6\</sup>mathrm{For}$  example with the cpu-lock on uniprocessor or with a spin-lock on multiprocessor machines.

CHAPTER 3. DESIGN 20

the locking was successful, the operation returns. Otherwise the thread helps the lock owner by switching to it. The lookup-lock operation is restarted if the thread is activated again.

The pseudo code in Figure 3.6 shows how get\_obj can be implemented. A lock-guard is given into the lookup function and initialized if the lookup was successful. Only a *try\_set*-function, which tries to get the lock and allows to set a guard in a called function and not only in the constructor of the guard, have to be added to the lock-guard implementation.

Figure 3.5: Named Object Locking

#### Locking of Unnamed Objects

Most operations on unnamed objects, like page- or capability table lookups are so fast, that a fine granular locking seems unnecessary. One exception of this is the deletion of objects. Unmapping<sup>7</sup> is a long running operation, which have to be synchronized with the usage of the objects.

For example the deletion of a mapping node has to wait until a map working on it has finished and vice versa. Locking the single mapping node and not a whole mapping tree, allows to give independent subtrees to tasks which do not trust each other<sup>8</sup>.

The deletion of child objects like name-spaces in a task or capability tables can be synchronized either with the parent lock, if they are collocated or with an object lock to avoid that a concurrent unmap can happen from the kernel-memory object.

Helping locks should be used for named and unnamed objects locks. Global accessed data like the running queue or the timeout list should be protected with global locks like kernel or processor locks.

```

bool

get_obj (Address id, Object *obj, Lock_guard *obj_guard)

{

for (;;) {

Cpu_lock_guard guard;

*obj = lookup(id);

if (!obj)

return false;

else

if (obj_guard->try_set(obj->lock()))

return true;

else

obj->lock()->owner->switch_to();

}

}

```

Figure 3.6: Get a Locked Object

<sup>&</sup>lt;sup>7</sup>unmap is the system-call to delete objects.

<sup>&</sup>lt;sup>8</sup>This is the base for changing the root in a monitor scenario mentioned in section 3.3.3.

#### **Deletion vs. Running Operations**

As said before, running operations on objects have to be finished before the objects can be deleted. This is easy if these operations hold a lock on the objects they use. This is mostly the case, but not for a running Long-IPC, where a lock to the partner is not hold while copying a message<sup>9</sup>.

This case can be handled by introducing a less privileged usage-lock, that shows that an object is used<sup>10</sup>. A deleting thread, which holds the object lock, signals the abort to all "users" and use helping to ensure that all running operations are canceled before deleting. To avoid that new threads grab the usage-lock while deleting is in progress, the object lock has to be held to get them. Using these two locks is deadlock-free if the object lock is not requested while holding a less privileged usage-lock.

#### 3.2.4 Summary

In this section I presented a rough design for a locking scheme for L4.sec. Since locking and realtime is not on the main focus of this work, these ideas are not implemented until now. Therefore a proof, whether the scheme works in any cases and has the needed properties, cannot be given.

But this approach supports the thesis that an L4.sec implementation can have the same real-time properties as FIASCO. Or in other words, that security, which comes with L4.sec, does not necessarily influence real-time.

### 3.3 Resource Dependencies

In previous L4 versions there exist only a map-dependency if a page was mapped from one task to another. The kernel stores the information, which map-dependencies exist, in mapping nodes. Since in L4.sec these mapping nodes are allocated in kernel-memory-objects, exists an additional dependency: the resource dependency. If the kernel-memory-object, that was used to allocate the mapping node, is deleted, the mapping node and with it the mapping is also deleted. This has the effect that not only the mapper (the source) and the mappee (the destination) can destroy a mapping but also a third party that gives the resources needed for this mapping.

Three-way dependencies need more design and implementation effort as dependencies between two parties. Thus I claim:

• Three-way dependencies should be avoided.

#### 3.3.1 Map

A map can be seen as an operation between two tasks: the mapper and the mappee. But who has to pay for the resources needed to establish a mapping between them? To answer this question we have to distinguish the memory needed for the name-spaces (page- and capability-tables) and for the mapping nodes.

The resources of the name-space have to be allocated by the mappee, because a page-table can be used for many mappings, which can come from different mappers. Nobody wants that a untrusted server can remove trusted mappings, by revoking the kernel memory for the corresponding pagetables.

The mapping nodes are allocated by the mapper, to avoid a special case for the initial mappings into a task. The initial mappings cannot be received, if memory is needed for the mapping nodes to get them.

For the following I assume that the mapper allocates the mapping nodes, like it is defined in the L4.sec specification. If someone shows that a copy is really needed, this assumption have to be reconsidered.

<sup>&</sup>lt;sup>9</sup>Because the copy could trigger page faults, which put the thread into a sleeping state until the page fault is resolved. To avoid dead locks, sleeping threads must not hold any lock.

<sup>&</sup>lt;sup>10</sup>This model is similar to a reader-writer lock scheme. The writer lock is the object lock, which can be hold only by a single thread. The usage-lock is a less privileged reader lock and can be used by many threads.

#### 3.3.2 Copy vs. Grant

The copy of space entries was introduced in L4.sec as replacement for grant to allow flat mapping hierarchies and for the building of high-bandwidth one-way channels.

In the following I describe why grant is not used any longer and that copy has problems with the resource dependency.

#### Why not Using Grant?

The usage of grant was a fast way in L4.V2 to change the owner of a mapping. In fact, grant was rarely used.

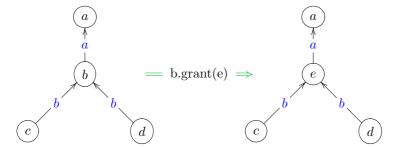

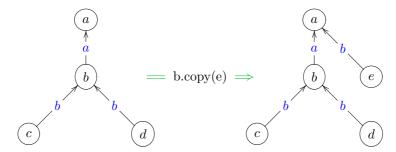

Figure 3.7: Grant an object

Granting is replaced by copy to avoid some problems using grant. For example granting a hole in a super-page is not possible since it needs resources for the page-table and mapping nodes. Another problem with grant is that it changes map dependencies<sup>11</sup> but not resource dependencies<sup>12</sup> like it is shown in figure 3.7. Granting a page from "b" to "e" changes the mapping from "b" to "e" but the resources of the child mappings are remain by "b".

#### Copy an Object

A copy duplicates the mapping-node for a given object (page, super-page, capability). For the mapping hierarchy it is the same as if the parent of the mapping-node calls a map. But copy has the same problem with resource dependencies like grant. The resources for the needed mapping nodes are given by the caller of the system-call. Figure 3.8 shows that for a mapping from "a" to "e" the caller of the copy "b" has given the resources.

Figure 3.8: Copy an object

The copy of a root node has to be forbidden because it can lead to cycles in the dependency-tree<sup>13</sup>. This happens for example if the creating task moves, through a copy and unmap, the root node of a child task into the child.

$<sup>^{11}{</sup>m Who}$  has mapped the page?

<sup>&</sup>lt;sup>12</sup>Who gives the resources for the mapping-nodes?

<sup>&</sup>lt;sup>13</sup>In fact the tree degenerate to a directed graph.

#### Summary

The new introduced copy has problems with resource dependencies. Either the decision that the mapper has to allocate the mapping nodes has to be changed, or copy has to be discarded. In the following I look at the second option.

#### 3.3.3 Copy Obsolete?

Is copy really needed or is it obsolete and should be marked as deprecated? To answer this question we have to consider the use cases of copy:

- flat mapping hierarchies

- limited memory space

- high bandwidth one-way channels

#### Flat Mapping Hierarchies

The copy-function can be used to build flat mapping hierarchies. A pager<sup>14</sup>, that does not want to unmap the mappings later, copies the mapping to the destination and unmap them only in the own address space.

The advantages of flat mapping hierarchies are obvious. The copy needs less resources than a full map and the corresponding unmap is faster because of a smaller mapping tree.

The whole copy functionality can be build in user-level if the pager of the thread does the map for them. The pager is trustworthy and can easily provide an interface to map to another space. So a copy is not really needed for flat mapping hierarchies.

#### **Limited Memory Space**

The size of the memory space is limited by the hardware. If a pager does not want to unmap the pages from a client it can **copy** them to the client and unmap them in the own address space. This avoids the pollution of the memory space of the pager.

Instead of copy the pager can use another memory space of a cooperating task to extend the number of map-able pages. Furthermore it is possible to build bridges between capability space and memory space. If pages can be mapped into a capability space and after that mapped back into another memory space, the limitation of the memory space is gone.

#### One-way Channels

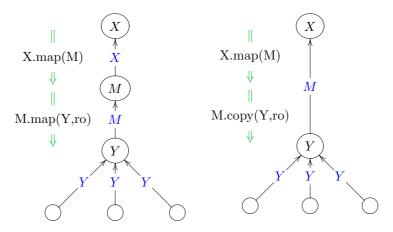

To build security systems, one-way communication channels<sup>15</sup> are needed.

Suppose the following scenario: A one-way channel should be established between two tasks: from X to Y. Simply using an Endpoint between X and Y is not possible, because Endpoints allow synchronous IPC. The information whether Y is ready to receive can be used to back-channel information to X. To decouple the send and receive phase of the message transfer, a monitor M is inserted between the two partners. So M intercepts every message sent from X to Y (see figure 3.9).

The monitor provides asynchronous communication between X and Y. To handle overload situations, the message transfer is unreliable: messages could be lost.

$<sup>^{14}\</sup>mathrm{A}$  task that provides the memory for another one.

<sup>15</sup> The information flow is unidirectional. The Bell-LaPadula model uses therefor the \*-Property rule (also known as the Confinement Property.), which forces that information cannot flow from higher security levels to lower one.

Figure 3.9: One-way channels using a monitor

#### High Bandwidth

To provide a high bandwidth one-way channel, a shared memory page between X and Y can be used. To establish this channel, X maps a page to M which maps the page read-only to Y. After this, X can write to the page and Y can only read from it.

If the monitor does not want to unmap the page, for example on policy changes, the second map is not needed. Instead, a copy can be used. The copy avoids the pollution of the memory space of M because M can unmap the first mapping. It cannot avoid the problem that M needs kernel-memory for the mapping nodes, to do the map or copy to Y. The requests and the used kernel-memory provide a back-channel, how many pages Y is receiving. Therefore, the kernel-memory cannot be requested from X or the Pager of X  $(P_X)$  and has to come from Y or the Pager of Y  $(P_Y)$ .

Figure 3.10: Mapping trees for high bandwidth one-way channels

#### Timing of unmap

The main problem of using shared memory as one-way channel is the timing of the unmap system-call. The time unmap needs depends on the number of child mappings in the mapping tree. If Y can influence this number, it could back-channel information to X. Y can influence the number in 4 ways:

- map the received page

- unmap the page

- accept a smaller flexpage that leads to a split of a super-page

- accept or not accept the page at receiving

To use a shared page anyway the monitor have to forbid the map and unmap of the page through Y and the mapping of super-pages through X. It is unclear how the accept-problem could be avoided.

#### Change the Root

The timing problem of unmap results from the map-dependency between X and Y. If the root of the mapping is not X but M the two X and Y can get independent branches of the mapping tree.

Figure 3.11: Change the root

Like shown in Fig. 3.11 X asks the monitor M to map a page from X read-only to Y. If X want to revoke the shared page from Y it asks M to do a unmap of it. With the changed root of the mapping tree a copy is unnecessary.

#### Conclusion

A copy is not needed for flat mapping hierarchies. The limited memory space, which copy improves, is not really a problem. High bandwidth one-way channels can be build without copy. Due to timing problems it is advised not to building them with copy anyway. Instead it can be build solely with map if the root of the mapping is changed.

The copy system-call can be discarded, because there is no scenario known that could only be build with it.

#### 3.3.4 Summary

Resource dependencies are uncritical with map, independent whether the mapper or the mappee gives the resources for the mapping nodes. With the decision that the mapper must give the memory, resource dependencies are a problem with copy, since a third party is involved. A closer look at copy showed that it is not needed and could be removed from the specification. Without it the problem of resource dependencies is resolved.

### 3.4 Unpinned UTCB Memory

UTCB's are for some strange reasons API objects in X.2.

Uwe Dannowski

Up to now the kernel can pin pages of kernel-memory also if they are visible in user memory-spaces. Because user-level can revoke kernel-memory in L4.sec, a simple pinning is not possible anymore.

#### 3.4.1 What are UTCB's?

UTCB's<sup>16</sup> are pinned kernel memory in the memory-space of a task. They are used for parameter transfer between kernel and user-level and have the advantage that no pagefault can happen by accessing them.

A fundamental disadvantage of UTCB's is that they restrict the memory layout of a task. Since UTCB's are a must for every thread in L4.X2, it is impossible that a user could use the whole address-space.

There are two possibilities to go with unpinned UTCB's. Either all operations using them have to be aborted or UTCB's are not used at all.

#### 3.4.2 Implement UTCB's

How can UTCB's be integrated into L4.sec? Now I mention some additional disadvantages of UTCB's L4.X2. After that I present a rough design for UTCB's in L4.sec.

#### Disadvantages of UTCB's in L4.X2

UTCB's in L4.X2 have some other disadvantages:

- cannot be moved or unmapped

- limit the number of threads in the task

- resources must be given at task creation

These things are specific to L4.X2 and not inherent to UTCB's.

#### UTCB's in L4.sec

A new named kernel object, called UTCB object, could be implemented. Such an object manages a page of kernel-memory which is writable to the user. A thread could be bound to an UTCB object and not to a task anymore<sup>17</sup>. Threads are only runnable if they have a valid UTCB object, which must be attached to a task. If a UTCB object is destroyed, unbound from a thread or detached from a task, all threads using them are stopped and all running operations are aborted.

It seems that these rough design could be build in L4.sec. It avoids the disadvantages of the L4.X2 implementation, since UTCB's could be attached to and detached from a task and threads could be freely bound to them.

Due to the fact that the implementation of UTCB's still needs a lot of code, the second option, to waiving of UTCB's at all, is considered in the following.

#### 3.4.3 Do we Need UTCB's?

#### Motivation

Using UTCB's needs a lot of kernel code and has the inherent problem that it pollutes the memory address-space of the tasks. So what is lost in a system without them? To answer this question have a look at the three reason why UTCB's are used:

- LIPC

- simpler kernel code

- optimizations

The abstraction of virtual registers and the possibility to map them to hardware registers are not bound to UTCB's. As W5 (see section 4.3) show, they can be used with other virtual registers as well.

$<sup>^{16}\</sup>mathrm{The}$  user-level part of a thread control block.

<sup>&</sup>lt;sup>17</sup>To prevent that a thread is bound to a UTCB object that is not in its task.

#### LIPC - Local IPC

UTCB's were introduced to build fast intra-task IPC in L4, known as LIPC, which is based on the idea of lazy process switching [LW01]. Due to different reasons, LIPC is not allowed for several cases. For example finite timeouts, receive- and send-only LIPC are not possible and normal IPC must be used instead.

The two available LIPC implementations for L4 show that LIPC decrease normal IPC performance by introducing an overhead of 14-30% [Wen02]. It is only faster if more than 5 LIPC are done between two normal IPC calls [Reu04]. This overhead results mainly from the design of LIPC. Since the kernel state is synchronized lazily, it must be checked at *every* Kernel entry whether this must be done or not. Additionally the synchronization is not as cheap as it was expected.

Endpoints can be used in L4.sec to send messages directly to worker threads, so LIPC will not be used for simple local message dispatching. Furthermore migrate-able user-level threads [Cla05] cannot use LIPC, but need another local communication mechanism.

In summary, the further development of L4.sec will not focus on LIPC.

#### Simpler Kernel Code

In principle there are two ways to handle pagefaults which could occur if the kernel accesses usermemory. First, they can be avoided by using pinned kernel memory, like UTCB's. And second, a transparent pagefault IPC can be send to the pager. Normally sending a pagefault IPC does not increase the kernel code complexity. But there are 2 exceptions: pagefaults in a Long-IPC<sup>18</sup> and delayed preemption's.

The implementation of delayed preemption's [DLSU04, Hoh02] is easy with UTCB's. Delayed preemption's requires two shared bits which are read and written in the timer-interrupt handler from the kernel and at start and end of a critical section from user-level. Since no pagefaults are triggered by using UTCB's the interrupt handler has not to take care of them. Without the possibility to store the two shared bits in pinned memory, the timer-interrupt handler need to know if a pagefault happened, which requires a special case in the pagefault handler. If such a pagefault occurred, the timer interrupt could handle this as a fault of the task and send a time-slice overrun message. In summary it seems to be that delayed preemption and likely other cases could be build without pinned kernel memory, but with an increase of the kernel code complexity.

UTCB's itself require a lot of code, that could be saved if they are not used. The implementation of a special case in the pagefault handler<sup>19</sup> seems to be less complicated than the introduction of a UTCB-object and of system-calls to manage them.

So kernel code seems to be simpler if UTCB's are omitted and the special cases are implemented.

#### **Optimizations**

UTCB's are also used as an optimization. For example system-call parameters are transfered through UTCB's, without the normally needed copy-in/out of the parameters.

Removing UTCB's could result in a performance bottleneck of the now needed copy-in/out of system-call parameters. To avoid this a kernel shared-memory object can be introduced. This is a kernel-memory object that can be mapped into the memory-space of many tasks. In contrast to UTCB's these objects could be optional, independent of threads, mappable and an unlimited number could be used in a task. In summary they are solely used as optimization.

#### Summary

As shown above LIPC is not part of L4.sec. The kernel code complexity decrease without UTCB's. For optimization purposes they could be replaced by a kernel shared-memory object. In summary a system without UTCB's can be build.

<sup>&</sup>lt;sup>18</sup>A IPC that transfers strings between two address spaces. This is independent from UTCB's.

$<sup>^{19}\</sup>mathrm{Sending}$  a time-slice overrun message must be implemented independently of UTCB's.

#### 3.4.4 Conclusion

Since UTCB's give no benefit anymore and the kernel should not depend on optimizations, I propose that *UTCB's should be considered experimental in the L4.sec specification*. If this results in a performance bottleneck, the above described *kernel shared-memory objects should be introduced*.

### 3.5 Summary

In this chapter I discussed the consequences of the new kernel-memory management in L4.sec to the implementation of the kernel. At the beginning I discussed the effects of dependencies to the deletion process of kernel objects. After that I presented a first rough design for a locking scheme for L4.sec. By taking a closer look at the resource dependencies I found that copy is unneeded. At the end I described why UTCB's are not a must anymore.

## Chapter 4

## **Implementation**

Defining the design of the new implementation was not done in a whole at the beginning, since nobody had a full survey of the consequences resulting from the changes of L4.sec. Instead many small cycles of design, implementation and test were used.

First I describe some implementation details. After that I close some holes of the specification. At the end I present a new system-call binding for L4.sec.

### 4.1 Implementation State

#### 4.1.1 Changes

The new concepts of L4.sec cause that new code has to be implemented. Additionally different changes of L4.sec prevent to reuse large parts of old FIASCO code. The main changes are:

#### The memory layout is modified.

A TCB area, where the thread control blocks can be easily found by their global name, is not useful anymore. A one-to-one mapping of physical pages is not used any longer. Since this limits physical memory that can be used for kernel memory<sup>1</sup>. Instead a region is needed, where converted pages can be made visible to the kernel.

#### A task is more than a page directory.

Previous L4 implementations use only the page directory as task object. Task local values are stored in invalid pagetable entries. Since a task object in L4.sec is a derived class where the storage of values cannot be controlled, this optimization can not be used anymore.

#### Thread locking and the system-calls differ.

As written in section 3.2, threads in L4.sec cannot be locked by writing to a memory location. Additional system-calls have to be rewritten, as the creation of threads and tasks, or IPC is handled in a different way than before.

#### Mapping database requirements changed.

Beside the fact that the current mapping database does not support the capability and IO space, single mapping nodes have to be allocated in task local memory. Storing a mapping tree in an array is no longer possible. Thus the mapping database has to be rewritten.

In the following I look at the mapping database implementation. After that I describe the kernel-memory object and other implementation details.

<sup>&</sup>lt;sup>1</sup>The whole physical memory cannot be mapped within such a region.

#### 4.1.2 MDB: The Mapping Database

#### What is a MDB?

The mapping database records map-dependencies to be able to execute the recursive unmap. The dependency, from where an object was mapped to another space, is stored in so-called mapping nodes.

The MDB was used before only for memory pages and IO-ports. Its usage is extended in L4.sec to capabilities as well.

While implementing the MDB and the map and unmap operations the following questions had to be answered:

- 1. Can we reuse the current implementation?

- 2. How to support different spaces and object types?

- 3. Can we handle that a thread want to unmap itself?

#### Current Implementation: Inapplicable

The current FIASCO mapping database [Gru98] is optimized for a minimal cache and TLB footprint. Only 5 bytes (or 8 bytes for the L4.X2 implementation [Cla04]) are needed for one mapping node. The mapping nodes of a single mapping-tree are stored in an dynamically allocated array of kernel memory. Because mapping nodes are unnamed objects in L4.sec and cannot be allocated in an array but must be allocated separately in different kernel memory objects<sup>2</sup>, the current implementation cannot be used.

#### Different Spaces and Object Types

The map and unmap operations work on the MDB and on different name-spaces. To simplify the implementation a common interface was introduced into L4.sec. This  $Space\_Xe$  interface hides the internal structure of the space, for example the page-table in a memory space. It promise an easier porting of the space implementation to other architectures.

The current space implementation uses class inheritance and virtual functions to implement the *Space\_Xe* interface. As an optimization a template could be used. The template avoid the indirect calls of the space interface at the cost of increasing the code size.

Unmap operates, beside on the name-spaces, on different object types. It has to delete for example threads, mapping nodes, page-tables and kernel-memory objects. A large switch to distinguish all cases in the unmap code is large and not easy to manage. Instead of this error prune and bad style of type dependent code, all objects could share a common interface called Kpage\_allocable. This interface is given in Fig. 4.1.

Using virtual functions for this interface simplifies the implementation. Compared to this should the overhead for storing the VMT (virtual method table) in every object and the overhead of the indirect call be negligible.

Using these two interfaces distributes the code for the map and unmap operation where the special knowledge is: at the spaces, objects and the mapping database.

#### Corner Case: Self-Unmap

One corner case was to handle the self-unmap of a thread. As defined in Section 4.2.3 the unmap has to be aborted and the thread has to be stopped in this case.

The deletion of the current thread is detected in the *predelete*-method of the thread. This information is propagated to the calling unmap-loop through the return value of the method, the loop is aborted and the locked nodes are unlocked. If the unmap returns such an error, the thread is stopped.

<sup>&</sup>lt;sup>2</sup>to be able to destroy them if a kernel page is reconverted

```

class Kpage_allocable

{

public:

virtual size_t size();

virtual Kpage_allocable * next_subobject (Kpage_allocable *);

virtual void delete_subobject (Kpage_allocable *);

virtual bool predelete();

}

```

Figure 4.1: The Kpage\_allocable interface is implemented by every object in L4.sec.

#### Summary

The old mapping database implementation could not be reused. The new implementation use clean interfaces for the different objects and name-spaces, which decreases the implementation effort a lot. The self-unmap problem is solved. As discussed in Section 5.2.3, the new implementation is of similar complexity then the old implementation.

### 4.1.3 Kernel-Memory Objects

A kernel-memory object is created in the memory space when converting a page. The destruction of them reconverts this page. Because both operations heavily depend on the memory space, they are implemented in the context of the memory space class. In the following I mention three issues according to this implementation.

#### Convert

At the first view it seems to be that only the system-bit in the page-table entry has to be set for converted pages to preempt the permissions. If it is set, the page is only accessible from kernel-mode and user-mode access results in a pagefault. A closer look shows that this leads to a security problem<sup>3</sup> if memory transfers are done in the kernel, like it happens on string messages. Memory references given to the kernel from user-level are usually, for performance reasons, only checked against the memory layout, but not on a single page level. Therefore page-table entries for converted pages have to be marked as *invalid*.

This invalidating of page-table entries, which are converted, have to be done for the whole mapping tree. Every superpage that contains the converted page and every splitting with the same physical address as the converted page, has to be made inaccessible. To track, which page is converted, a bit-field for every physical page is used. Splittings out of an inaccessible superpage use this bit-field to decide, whether they could be accessible or not.

#### Reconvert

A reconvert restores the preempted permissions. Therefore it has also to iterate over the whole mapping tree. To decide whether a superpage contains no converted page anymore and can therefore be made accessible, the number of converted pages is counted for every superpage. This optimization avoids to check 1024 bits in the bit-field.

#### Convertible Superpages

Superpages need not to be convertible because someone could split them by mapping smaller parts to another location. This is not true for sigma0. There is no place in the memory space where it could map smaller pages. Giving initial some smaller pages to sigma0 is not an option here, since

<sup>&</sup>lt;sup>3</sup>The kernel memory can be read and written through user-level.

it limits the memory layout of the whole system<sup>4</sup> and the design of sigma0<sup>5</sup>. Thus superpages have to be convertible.

In contrast to a converted page, superpages can have more than one kernel-memory object using them. It must be ensured that all these objects can be reached while unmapping the superpage. Using a doubly linked list<sup>6</sup> should be sufficient. The list of the kmem mapping nodes can be reused for this, if we take care to update the object pointer of the superpage mapping node at removal.

#### Summary

The implementation of the kernel-memory object was straight forward. The only surprise was that a time intensive iteration over the whole mapping tree is needed. Creating a kernel-memory object is therefore not as fast as the creation of other objects or the mapping of pages and capabilities.

#### 4.1.4 IPC

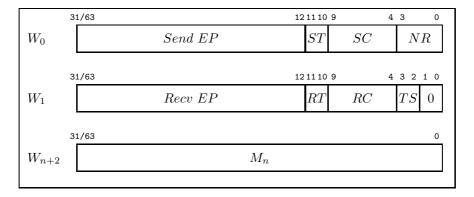

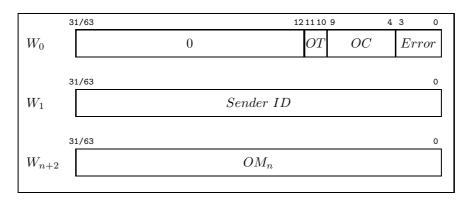

Implementing a full featured L4 IPC is a complex part of an L4 system, because it integrates synchronization, message transfer and mapping into a single system-call. To provide basic functionality to user-level and to check the mapping database implementation, I implemented only Short-IPC.

This Short-IPC implementation for L4.sec allows to transfer single words and map items. It is possible to abort a waiting sender or receiver before a rendezvous happens through ex\_regs. The IPC timeout is currently ignored. Short-IPC's can be stacked, which is used to send the kernel generated pagefault IPC's in a system-call.

Splitting a thread into a sender and receiver part, like in FIASCO, is not implemented. This splitting was used to send preemption and activation IPC independent from a normal IPC, but it is not needed until now.

#### 4.1.5 Testing