---

Technische Universität Dresden

Fakultät Informatik

Institut für Systemarchitektur

Prof. Dr. Hermann Härtig

# Diplomarbeit

zum Thema

## Migration Sweetspots

Konstantin Tabere

Geboren am 12.08.1985 in Leningrad

Matrikel-Nr. 3206798

Betreuer: Dipl.-Inf. Benjamin Engel

Dipl.-Inf. Michael Roitzsch

betreuender Hochschullehrer: Prof. Dr. Hermann Härtig

Eingereicht bei der Professur für Betriebssysteme am 30. Oktober 2013.

## **Erklärung**

Ich erkläre, dass ich die vorliegende Arbeit selbstständig, unter Angabe aller Zitate und nur unter Verwendung der angegebenen Literatur und Hilfsmittel angefertigt habe.

Dresden, den 30. Oktober 2013

# Inhaltsverzeichnis

|           |                                                                                 |            |

|-----------|---------------------------------------------------------------------------------|------------|

| <b>I</b>  | <b>Abbildungsverzeichnis .....</b>                                              | <b>III</b> |

| <b>II</b> | <b>Tabellenverzeichnis .....</b>                                                | <b>V</b>   |

| <b>1</b>  | <b>Einleitung .....</b>                                                         | <b>1</b>   |

| <b>2</b>  | <b>Grundlagen .....</b>                                                         | <b>3</b>   |

| 2.1       | Prozesse und Threads.....                                                       | 3          |

| 2.2       | Systemaufrufe .....                                                             | 5          |

| 2.3       | Linux-Scheduler.....                                                            | 6          |

| 2.3.1     | Kontextwechsel .....                                                            | 8          |

| 2.4       | Architektur moderner x86-64-Mehrkernprozessoren .....                           | 9          |

| 2.4.1     | Paging und MMU.....                                                             | 11         |

| 2.5       | Performance-Counter .....                                                       | 12         |

| 2.5.1     | MSRs in x86-Intel-Prozessoren.....                                              | 13         |

| 2.6       | Performance-Counter in Linux .....                                              | 14         |

| 2.6.1     | Die perf_event-Schnittstelle im Linux-Kern .....                                | 14         |

| 2.7       | Linux Kernel-Entwicklung und Kernel-Module.....                                 | 15         |

| 2.8       | Verwandte Arbeiten .....                                                        | 16         |

| 2.8.1     | Vergleich Inter-Core Prefetching mit Migration Sweetspots .....                 | 18         |

| <b>3</b>  | <b>Entwurf.....</b>                                                             | <b>21</b>  |

| 3.1       | Theoretische Betrachtung .....                                                  | 21         |

| 3.2       | Vorteile von Migration Sweetspots.....                                          | 24         |

| 3.2.1     | Beispiel mit einer Matrixmultiplikation .....                                   | 24         |

| 3.3       | Anforderungen an die Suche nach Migration Sweetspots mit dem<br>Linux-Kern..... | 28         |

| 3.4       | Auswahl der Suchstrategie und geeigneter Performance-Counter .....              | 29         |

| 3.5       | Suche nach Migration Sweetspots durch Benutzer-Prozesse .....                   | 32         |

| 3.6       | Folgen der Migrationsverzögerung.....                                           | 33         |

| <b>4</b>  | <b>Implementierung .....</b>                                                    | <b>37</b>  |

| 4.1       | Profiling und Mikro-Benchmarks .....                                            | 38         |

|            |                                                                                                               |           |

|------------|---------------------------------------------------------------------------------------------------------------|-----------|

| 4.1.1      | Erkennen von Prozess-Start und Prozess-Ende ausgewählter Programme .....                                      | 39        |

| 4.2        | Konfiguration der Performance-Counter mit der perf_event-Schnittstelle.....                                   | 41        |

| 4.3        | Änderungen am Scheduler .....                                                                                 | 44        |

| 4.3.1      | Änderungen an der task_struct-Struktur.....                                                                   | 45        |

| 4.3.2      | Neu implementierte Funktionen.....                                                                            | 47        |

| 4.4        | Wahl des Intervalls T .....                                                                                   | 48        |

| 4.5        | Kernel-Modul zur Erzeugung des Intervalls T .....                                                             | 49        |

| 4.6        | Probleme während der Implementierung.....                                                                     | 50        |

| <b>5</b>   | <b>Evaluierung.....</b>                                                                                       | <b>53</b> |

| 5.1        | Testsystem.....                                                                                               | 53        |

| 5.2        | Überprüfung des Profilings mit Hilfe von Ftrace .....                                                         | 54        |

| 5.2.1      | Grafische Auswertung.....                                                                                     | 56        |

| 5.3        | Messungen mit den Mikro-Benchmarks .....                                                                      | 58        |

| 5.3.1      | Auftreten von Migration Sweetspots am Beispiel von matrixmult in Abhängigkeit der Größe der Arbeitsmenge..... | 59        |

| 5.3.2      | Parallele Ausführung matrixmult und memeater .....                                                            | 63        |

| 5.3.3      | Migration zu einem Migration Sweetspot Typ 1 .....                                                            | 65        |

| 5.3.4      | Migration zu einem Migration Sweetspot Typ 2.....                                                             | 67        |

| <b>6</b>   | <b>Zusammenfassung.....</b>                                                                                   | <b>71</b> |

| <b>III</b> | <b>Literaturverzeichnis .....</b>                                                                             | <b>75</b> |

| <b>A</b>   | <b>Anlagen vom Typ1.....</b>                                                                                  | <b>79</b> |

|            | A 1. Anlagenbeispiel 1 .....                                                                                  | 79        |

# I    Abbildungsverzeichnis

|                                                                                                                                                            |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

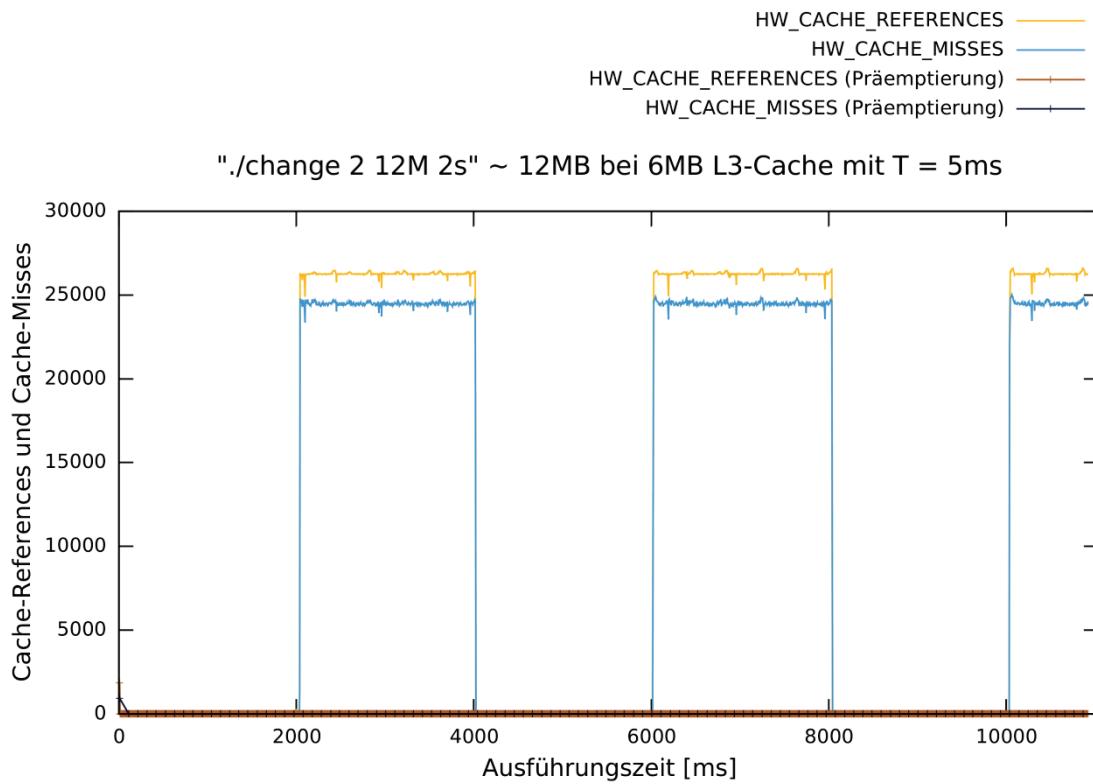

| Abbildung 1: Cache-Zugriffs-Diagramm bei Ausführung des Programms<br>change aus dem Mikro-Benchmark .....                                                  | 57 |

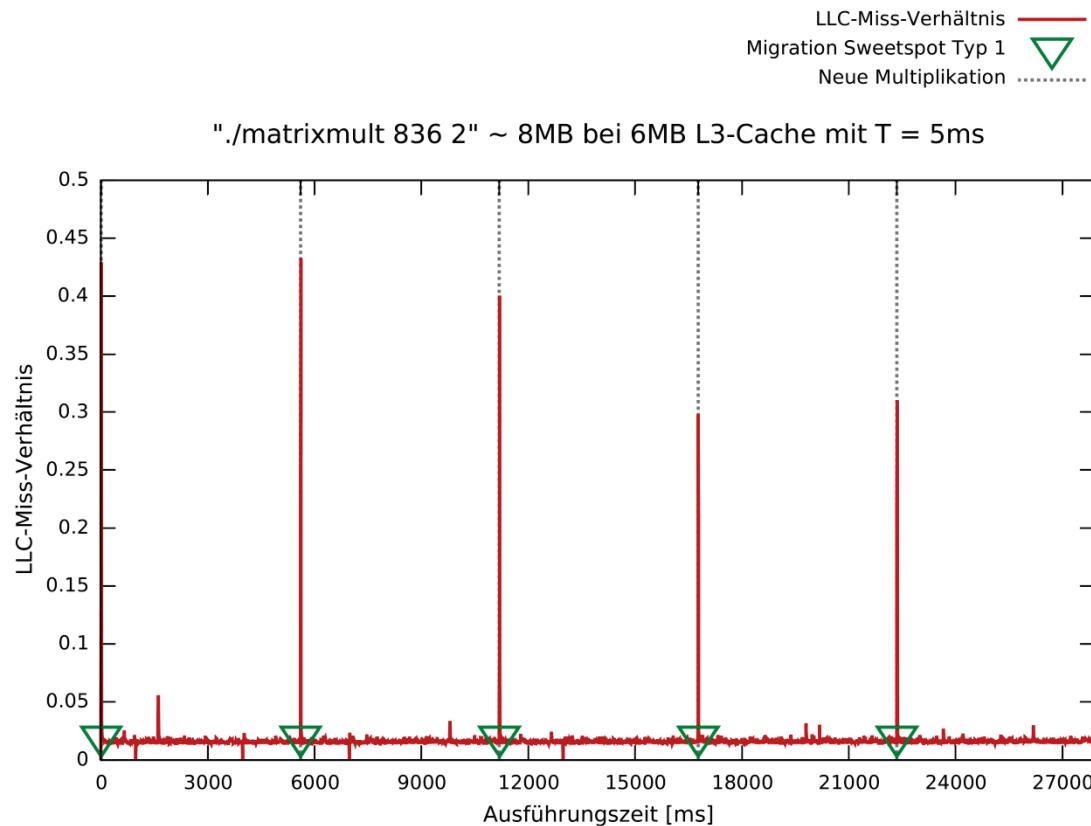

| Abbildung 2: Diagramm des LLC-Miss-Verhältnis für eine Messung mit<br>matrixmult mit Markierung der gefunden<br>Migration Sweetspots Typ 1 .....           | 62 |

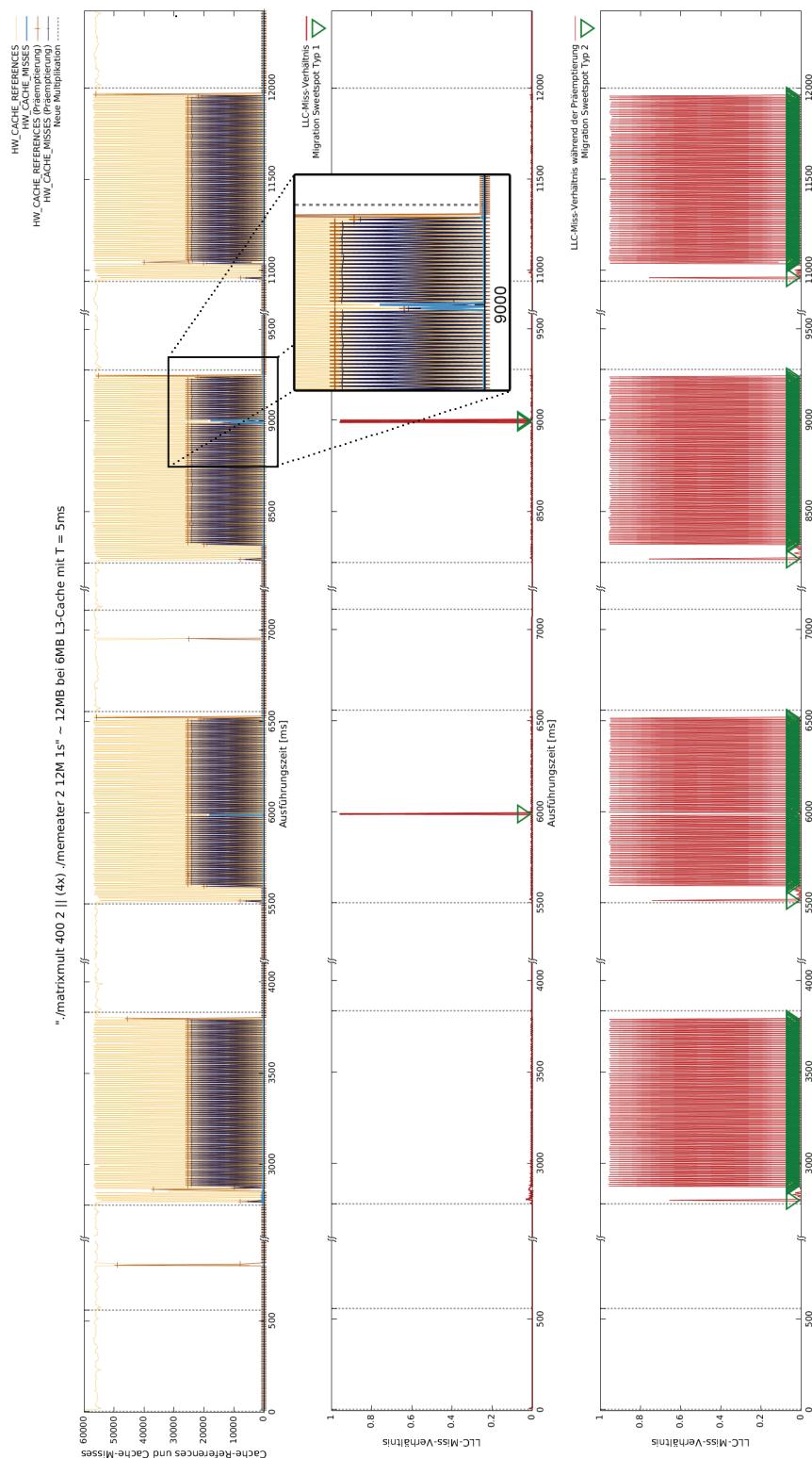

| Abbildung 3: Cache-Miss-Diagramm und Migration-Sweetspot-Diagramme für<br>eine Messung mit paralleler Ausführung von matrixmult und<br>memeater.....       | 64 |

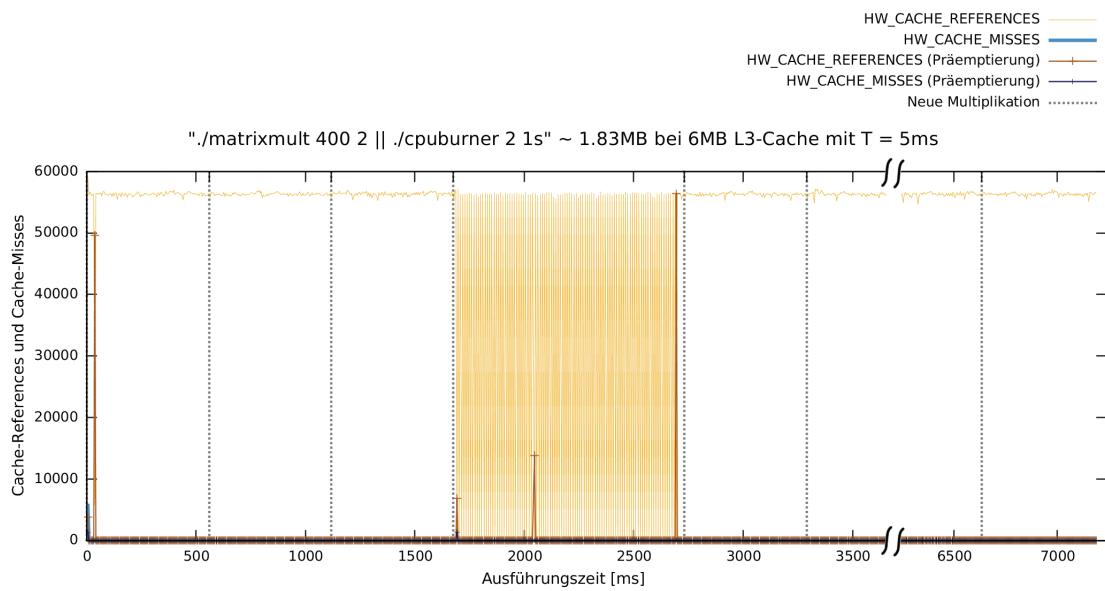

| Abbildung 4: Cache-Zugriffs-Diagramm für eine Ausführung der Messung zur<br>Migrationen zu einem Migration Sweetspot Typ 2 ohne<br>Migration (Fall A)..... | 69 |

## II Tabellenverzeichnis

|             |                                                                                                                                 |    |

|-------------|---------------------------------------------------------------------------------------------------------------------------------|----|

| Tabelle 1:  | Ablaufplan einer Matrixmultiplikation ohne Migration .....                                                                      | 25 |

| Tabelle 2:  | Ablaufplan einer Matrixmultiplikation mit Migration ohne Berücksichtigung von Migration Sweetspots .....                        | 27 |

| Tabelle 3:  | Anforderungen an die Suche nach Migration Sweetspots .....                                                                      | 28 |

| Tabelle 4:  | Zugriffszeiten bei Cache-Hit bei Intel Core-i7-Prozessoren, aufgeschlüsselt nach Cache-Ebene .....                              | 35 |

| Tabelle 5:  | Beispiel für Werte des config-Attributs bei ausgewähltem<br>PERF_TYPE_HARDWARE type-Attribut.....                               | 42 |

| Tabelle 6:  | Ausgewählte Werte für die Konfiguration des config-Attributs bei ausgewähltem PERF_TYPE_HW_CACHE type-Attribut.....             | 43 |

| Tabelle 7:  | Übersicht aller neu implementierten Funktionen im Linux-Kern .....                                                              | 45 |

| Tabelle 8:  | Messergebnisse der Messung mit dem Programm matrixmult in Abhängigkeit der Matrizengröße .....                                  | 61 |

| Tabelle 9:  | Messergebnisse der Messung zur Migration zu einem Migration Sweetspot Typ 1 im Vergleich zu einer willkürlichen Migration ..... | 66 |

| Tabelle 10: | Messergebnisse zur Messung für die Migration zu einem Migration Sweetspot Typ 2 .....                                           | 68 |

# 1 Einleitung

Jedem Informatiker ist das Moor'sche Gesetz ein Begriff. Die Anzahl der Transistoren auf einem Chip verdoppelt sich alle zwei Jahre. Diese wegweisende Behauptung hatte Gordon Moore im Jahre 1965 aufgestellt und wenn man sich die Entwicklung der Prozessoren der letzten Jahrzehnte anschaut, so gilt das Gesetz noch bis heute [Col13]. Für die Einhaltung der Gesetzmäßigkeit sind vor allem zwei wesentliche Entwicklungen verantwortlich. Zum einen ermöglicht der Fortschritt bei der Reduzierung der Strukturgrößen in integrierten Schaltkreisen immer mehr Transistoren auf einen Chip unterzubringen. Zum anderen gibt es mit der Vermehrung der auf einem Prozessor vorhandenen CPUs eine sinnvolle Möglichkeit mit mehr verbauten Kernen immer leistungsstärkere Prozessorarchitekturen zu schaffen.

Diese Entwicklung stellt nicht nur Softwareentwickler in der ganzen Welt vor neue Herausforderungen. Wie kann man das große Rechenpotential eines modernen Prozessors mit mehreren CPUs intelligent nutzen? Auch aktuelle Betriebssysteme müssen für den Umgang mit Mehrkernprozessoren angepasst und weiterentwickelt werden. Besonders der Scheduler, der für die Verteilung der auf einem System vorhanden Rechenzeit an Anwendungen, die ausgeführt werden, zuständig ist, muss optimal arbeiten. Um den maximalen Durchsatz zu gewährleisten ist es wichtig, dass Anwendungen auf allen zur Verfügung stehenden CPUs verteilt ausgeführt werden. Für diesen Zweck führt der Linux-Scheduler in regelmäßigen Abständen einen Lastausgleich durch. Dabei werden ein Teil der Anwendungen, die auf einer CPU mit hoher Last ausgeführt werden auf andere CPUs mit weniger Last migriert. So wird die Last verteilt und fortan erhalten alle Anwendungen mehr Rechenzeit und werden schneller abgearbeitet.

Eine Migration einer Anwendung zu einer anderen CPU kann sich allerdings auch negativ auswirken. Dies ist der Fall, wenn die Daten mit denen die Anwendung arbeitet vorrangig in CPU-nahen Zwischenspeichern – den Caches – stehen, auf die nach der Migration nicht mehr oder nur deutlich langsamer als vor der Migration zugegriffen werden kann. Alle modernen Prozessoren besitzen mehrere Cache-Ebenen, die über unterschiedliche Kapazitäten und Zugriffszeiten verfügen. Bei vielen aktuellen Prozessoren sind die untersten beiden Cache-Ebenen (L1- und L2-Cache) exklusiv für die CPU eines Kerns nutzbar. Möchte die CPU eines anderen Kerns nach der Migration

einer Anwendung auf Daten zugreifen, die im L1- oder L2-Cache des zuletzt benutzten Kerns stehen, kommt es zu Verzögerungen.

An dieser Stelle soll diese Arbeit eine Methode zur Minimierung dieser ungewollten Verzögerungen vorstellen. Mit Hilfe von Performance-Countern sollen unter dem Betriebssystem Linux zur Laufzeit von Anwendungen Zeitpunkte gefunden werden, an denen eine Migration zu einer anderen CPU so gewählt wird, dass es zu weniger Verzögerungen beim Zugriff auf Daten kommt.

Diese Zeitpunkte werden unter dem Begriff Migration Sweetspots zusammengefasst und sind das zentrale Thema dieser Arbeit. Die Analyse, Implementierung und eine Evaluierung eines Linux-Kerns, der Migration Sweetspots erkennen kann, werden beschrieben.

Die weitere Arbeit gliedert sich in die folgenden fünf Kapitel: Im Kapitel 2 werden die Grundlagen für das allgemeine Verständnis der Arbeit gelegt. Da das Themengebiet ein umfassendes Wissen über Rechenarchitektur und den Aufbau von Betriebssystemen erfordert, werden die wesentlichen Aspekte des Schedulings, Begrifflichkeiten und Funktionsweisen von Betriebssystemfunktionen in Linux beschrieben.

Mit Hilfe von Performance-Countern wird in Kapitel 3 der Entwurf einer Technik beschrieben, wie durch ein spezielles Profiling von Prozessen Migration Sweetspots gefunden werden können. Die Implementierung dieser Technik im Linux-Kern und die Probleme, die während der Programmierung der neu implementierten Funktionen gelöst werden mussten, werden im Kapitel 4 vorgestellt.

Eine Evaluierung und Überprüfung der Funktionalität mit Hilfe ausgewählter Programme eines Mikro Benchmarks wird in dem Kapitel 5 durchgeführt. Kapitel 6 fasst die gesammelten Ergebnisse zusammen und gibt einen Ausblick über weiterführende Arbeiten.

## 2 Grundlagen

Als Einleitung für die weitere Arbeit werden in diesem Kapitel die Grundlagen, die zum besseren Verständnis der folgenden Kapitel dienen, erläutert.

Zunächst werden im Abschnitt 2.1 die Begriffe Prozess und Thread, im Sinne eines Betriebssystems eingeführt. Abschnitt 2.2 erklärt aufbauend für die nachfolgenden Abschnitte die Funktion von Systemaufrufen. Der Abschnitt 2.3 befasst sich mit dem Scheduler und dazugehörige Systemkomponenten im Linux-Kern. Im Abschnitt 2.4 wird die Architektur moderner x86-Mehrkernprozessoren und die Speicherhierarchie erklärt. Der Aufbau und die Nutzung von Hardware Performance-Countern wird im Abschnitt 2.5 betrachtet.

Abschnitt 2.6 beschreibt anschließend, wie Performance-Counter im Linux-Kern unterstützt werden und welche Schnittstellen Kernelentwicklern zur Verfügung stehen. Im Abschnitt 2.7 werden einige generelle Hinweise zur Linux Kernelentwicklung zusammengefasst. Ein Blick auf verwandte Arbeiten wird im Abschnitt 2.8 geworfen.

### 2.1 Prozesse und Threads

Zu den Aufgaben eines Betriebssystems gehört es geteilte Ressourcen eines Computersystems auf Anwendungsprogramme (kurz Anwendungen) aufzuteilen. Jede Anwendung wird dabei auf Betriebssystemebene als ein Prozess repräsentiert. Alle Prozesse besitzen einen eigenen Adressraum, mindestens einen Thread und eine Menge an zugewiesenen Ressourcen. Es ist dabei unerheblich, ob der Prozessstart durch eine vom Benutzer getätigte Aktion ausgelöst (Benutzer-Prozesse) wird, oder das Betriebssystem selber (Kernel-Prozesse) den Prozessstart veranlasst hat.

Threads sind die Ausführungseinheiten einer Anwendung. Jeder Prozess besitzt nach dem Start einen Hauptthread, welcher den Start mehrerer weiterer Threads veranlassen kann. Unter dem Ausführungskontext eines Threads versteht man die Attribute und Eigenschaften eines Threads, die einen Thread einem Prozess zuordnen. Die Threads eines Prozesses haben einen gemeinsamen Ausführungskontext, einen eigenen Stack, einen Befehlszähler, eigene Register für lokale Variablen und laufen zunächst unabhängig voneinander auf einer zur Verfügung stehenden CPU (central processing unit). Bei

einem System mit einem Einkernprozessor teilen sich alle Threads eine CPU. Bei einem Mehrkernprozessorsystem gehört es zur Aufgabe des Betriebssystems alle Threads entsprechend einer Scheduling-Policy auf die Anzahl des vorhandenen CPUs zu verteilen.

Allgemein gibt es zunächst nur drei Zustände in denen sich ein Thread befinden kann: bereit, blockiert oder laufend. Ein neu erzeugter Thread beginnt seinen Lebenszyklus immer im bereit-Zustand. Alle Zustandsübergänge eines Threads werden durch den Scheduler geregelt. Dieser implementiert einen Algorithmus, der aus der Menge der bereiten Threads einen auswählt und einer CPU zuweist. Dann befindet sich der Thread im laufend-Zustand und die Befehlsinstruktionen des Threads werden von der CPU abgearbeitet. Der Zustand bleibt erhalten, bis der Thread einen Systemaufruf (siehe Abschnitt 2.2) tätigt, der das Abarbeiten weiterer Befehlsinstruktionen zunächst verhindert. Dies passiert typischerweise beim Lese- oder Schreibzugriff von Daten der externen Festplatte. Dann muss der Thread auf ein bestimmtes Ereignis warten – in dem Fall eines Lesezugriffs auf das Eintreffen der Daten, bis er weiterlaufen kann. Dieser Thread-Zustand heißt blockiert-Zustand oder anders ausgedrückt: Der Thread ist blockiert. Sobald das Ereignis auf das gewartet wird eingetreten ist, wechselt der Scheduler den Zustand des Threads wieder in den bereit-Zustand.

Zusätzlich ist ein Übergang vom laufend-Zustand zum blockiert-Zustand möglich, wenn Interrupts, d.h. Systemunterbrechungen auftreten, die das Ausführen des gerade laufenden Threads verhindern. Ein Interrupt kann auch auftreten, wenn ein Thread schon längere Zeit auf einer CPU gelaufen ist und der Scheduler einen anderen bereiten Thread höher priorisiert einstuft, als den zur Zeit laufenden Thread.

Der Linux-Kern implementiert Threads als leichtgewichtige Prozesse. Diese können sich einige Ressourcen teilen, beispielsweise den Adressraum und offene Dateien. Jedoch besitzt jeder leichtgewichtige Prozess einen eigenen Ausführungskontext und wird als ein unabhängiger Prozess ausgeführt. Der Vorteil liegt auf der Hand. Bei „normalen“ Threads blockiert der gesamte Prozess und damit alle Threads des Prozesses, sobald ein Thread in den blockiert-Zustand wechselt. Dies passiert bei leichtgewichtigen Prozessen nicht. Hier können mehrere leichtgewichtige Prozesse mit gemeinsamen Ressourcen (im weitesten Sinne Threads einer Anwendung) blockieren oder schlafen, ohne dass andere Prozesse davon betroffen werden. Mit dem Systemaufruf `fork()` wird im Linux-Kern ein neuer (leichtgewichtiger) Prozess (Kinderprozess) erstellt, der zunächst eine fast vollständige Kopie des Prozesses darstellt, der `fork()` aufgerufen hat (Elternprozess). Alle Ressourcen werden zunächst gemeinsam genutzt, doch sobald während der Ausführung beispielsweise Änderungen an Daten im Speicher festgeschrieben werden müssen, wird per `Copy-on-write` der Speicher tatsächlich

aufgeteilt und der Kindprozess bekommt einen eigenen neuen Speicherbereich. Führt ein Kindprozess mit `exec()` ein neues Programm aus, wird die Aufteilung aller Ressourcen herbeigeführt. Der Kindprozess ist dann komplett vom Elternprozess getrennt. Der Systemaufruf `clone()` erzeugt einen neuen Prozess unter Angabe der von Kind- und Elternprozess fortan gemeinsam genutzten Ressourcen. Die Begriffe Thread, Prozess oder gelegentlich auch Task werden bei Linux als Synonyme verwendet und beschreiben alle leichtgewichtige Prozesse. Weitere Details zu leichtgewichtigen Prozessen und deren Implementierung im Linux-Kern folgen im Kapitel 4.

## 2.2 Systemaufrufe

Grundsätzlich unterscheiden moderne Prozessoren und Betriebssysteme verschiedene Betriebsmodi der CPU unter denen Prozesse ausgeführt werden. Es wird zwischen dem Kernel-Modus (Ring 0) und den Benutzer-Modi (Ring 1–3) unterschieden. Nur wenn Prozesse im Kernel-Modus ausgeführt werden, haben sie Zugriff auf den kompletten Befehlssatz der CPU. Laufen sie stattdessen im weniger privilegierten Benutzer-Modus, so steht nur ein reduzierter Befehlssatz aus Sicherheitsgründen zur Verfügung.

Diese Einteilung ist notwendig, damit die Sicherheit eines Systems gewährleistet werden kann. Wenn Benutzer-Prozesse einige für die Systemstabilität kritische Aufgaben versuchen selbst zu erledigen, ohne Rücksicht auf andere Prozesse zu nehmen, so droht Datenverlust oder Fehlfunktionen sind die Folge.

Ein Beispiel wäre hier ebenfalls der Zugriff auf Daten der Festplatte. Sobald ein Benutzer-Prozess Daten von der Festplatte lesen möchte, so teilt er dies durch einen Systemaufruf mit und es erfolgt ein Wechsel in den Kernel-Modus (Kerneintritt). Dann wird die Ausführung der Befehlsinstruktionen des Prozesses auf der CPU unterbrochen und der Befehlszähler wird gespeichert. Anschließend liest eine Kernel-Routine die Daten von der Festplatte aus und kopiert diese in den Adressbereich des Prozesses. Danach erfolgt wieder ein Wechsel des Betriebsmodus der CPU und diese schaltet in den Benutzer-Modus und der Prozess wird dort weiter ausgeführt, wo er unterbrochen wurde (Kernaustritt). Bei jedem Systemaufruf erfolgen demzufolge ein Kernein- und ein Kernaustritt.

## 2.3 Linux-Scheduler

Die Aufgabe des Scheduler ist es die auf einem System vorhandene Rechenzeit an Prozesse zu verteilen. Dabei sind mehrere Anforderungen zu berücksichtigen:

- Fairness – jeder Prozess bekommt einen fairen Anteil der Rechenzeit

- Policy Enforcement – vorgegebene Scheduling-Strategien werden durchgesetzt

- Balance – alle CPUs des Systems sind ausgelastet

Neben diesen drei Hauptanforderungen werden ja nach Einsatz des Betriebssystems weitere Ziele wichtig. Bei Stapelverarbeitungssystemen möchte man den Durchsatz (Anzahl der erledigten Jobs pro Zeiteinheit) maximieren und die Durchlaufzeit (Zeit vom Start bis zur Beendigung) minimieren. Bei interaktiven Systemen rückt die Antwortzeit (schnelle Antwort auf Anfragen) und die Proportionalität, also die Erfüllung der Erwartungen des Benutzers, in den Vordergrund. Eine weitere Umgebung sind Echtzeitsysteme, das heißt Systeme deren Prozesse bestimmte Deadlines einhalten müssen, um Datenverlust oder weitere kritische Systemfehler zu verhindern. Gleichzeitig muss der Scheduler in der Lage sein, Aussagen zur Vorhersagbarkeit zu treffen, um Qualitätseinbußen im System zu vermeiden. Aufgrund des breiten Einsatzes von Linux in fast allen dieser Umgebungen berücksichtigt der Linux-Scheduler viele der möglichen Szenarien. Es werden drei Klassen von Prozessen unterschieden.

### Echtzeit-FIFO

Die höchste Priorität haben Echtzeit-FIFO-Prozesse (fifo = first in first out). Diese können von keinem anderen rechenbereiten Prozess unterbrochen werden, außer von einem anderen Echtzeit-FIFO-Prozess mit einer höheren Priorität. Linux-intern werden für Echtzeit-Prozesse die Prioritätsebenen von 0 bis 99 vergeben. Dabei hat 0 die höchste und 99 die niedrigste Priorität.

### Echtzeit-Round-Robin

Ähnlich, wie bei Echtzeit-FIFO, verhält es sich mit den Echtzeit-Round-Robin-Prozessen. Der Unterschied ist der, dass diese nur für ein zugewiesenes Quantum an Rechenzeit ausgeführt werden und dann vom Scheduler unterbrochen werden. Anschließend werden sie an das Ende einer Liste aller Echtzeit-Round-Robin-Prozesse

gesetzt, aus der der nächste rechenbereite -Prozess ausgewählt wird. Hier werden auch die Prioritätsebenen von 0 bis 99 vergeben.

## **Timesharing**

Alle „normalen“ Nicht-Echtzeit-Prozesse besitzen die Prioritätsebenen 100 bis 139. Insgesamt gibt es in Linux damit 140 verschiedene Prioritäten für Prozesse. Die Standardpriorität von neu gestarteten Benutzer-Prozessen liegt bei 120. Diese kann jedoch mit dem Systemaufruf `nice()` durch den Prozess selber, beispielsweise ausgelöst durch eine Benutzeraktion verändert werden. Erlaubte Werte für den `nice`-Wert reichen von -20 bis +19, womit die Priorität entsprechend der Grenzen für Nicht-Echtzeit-Prozesse verändert werden kann. Timesharing-Prozesse laufen ebenso, wie die Echtzeit-Round-Robin-Prozesse für ein vorgegebenes Quantum an Zeitintervallen. Diese Zeitintervalle sind festgelegt auf die Dauer von einer Millisekunde und werden im Linux-Kern `Jiffies` genannt. Für die Einhaltung ist im Scheduler ein Timer mit 1.000 Hz implementiert.

Für jede logische CPU wird im Linux-Scheduler eine Runqueue angelegt. Dies ist eine Datenstruktur, die unter anderem die Arrays `active` und `expired` der Länge 140 enthält, deren Elemente auf eine Liste mit Prozessen (Tasks) mit entsprechender Priorität zeigen. Alle bereiten oder laufenden Prozesse befinden sich zunächst im `active`-Array. Läuft die Zeitscheibe (Quantum) eines Tasks ab, so wird er in das `expired`-Array verschoben. Blockiert ein Task, so wird er aus dem `active`-Array entfernt und erst wieder hinein gesetzt, wenn er deblockiert wurde. In der Zwischenzeit befindet sich der Task in der `wait`-Queue. Sobald das `active`-Array leer ist werden die Zeiger auf das `active`- und `expired`-Array einfach getauscht und ein neuer Zyklus beginnt.

Jede Prioritätsebene erhält eine eigene Zeitscheibenlänge (die Länge der Zeitscheibe ist immer ein Vielfaches eines `Jiffy`) und Tasks mit höheren Prioritäten dürfen länger laufen als solche mit niedrigeren Prioritäten. Beispielsweise besitzt die Prioritätsebene 100 eine Zeitscheibe mit einer Gesamtlänge von 800 ms und ein Task mit Prioritätsebene 139 eine Zeitscheibenlänge von nur fünf ms. Je nach Verhalten der Prozesse und deren Zustand werden deren Prioritäten vom Scheduler dynamisch angepasst. So bekommen beispielsweise blockierte Prozesse, die auf das Lesen von Daten von der Festplatte warten, dynamisch eine höhere Priorität zugewiesen, um möglichst schnell weiterlaufen zu können, wenn die Daten angekommen sind.

Bei Mehrkernprozessoren findet neben der dynamischen Prioritätsanpassung in regelmäßigen Abständen noch ein Lastausgleich zwischen den CPUs statt. Dabei wird versucht die Menge an Tasks pro Runqueue möglichst gleichmäßig aufzuteilen, um sicherzustellen, dass die Systemlast ausgeglichen ist. Ein neuer Task wird bei Einplanung durch den Scheduler in die Runqueue der CPU mit der kleinsten momentanen Last platziert.

Lokale Affinitätsanforderungen der Tasks müssen vom Scheduler ebenfalls berücksichtigt werden. Einige Prozesse wollen selber festlegen, auf welchen CPUs sie ausgeführt werden möchten. Um die positiven Wirkungen eines „heißen“ Caches zu maximieren bleiben Tasks in der Regel auf einer CPU und wechseln nur in dem Fall, wenn eine andere CPU keine weiteren bereiten Tasks in der eigenen Runqueue besitzt. Solche Wechsel sind sehr teuer. Neben den üblichen Kosten für einen Kontextwechsel müssen noch alle Registerinhalte, Speichertabellen usw. auf die neue CPU kopiert werden. Zusätzlich müssen einige Daten für die neue CPU aus den CPU-nahen Caches (L1- und L2-Cache) der alten CPU heraus kopiert werden, was sich in einer verschlechterten Task-Laufzeit, auswirkt.

### **2.3.1 Kontextwechsel**

Kontextwechsel treten auf, wenn der Scheduler die Ausführung eines Prozesses auf einer CPU beendet und anschließend einen anderen Prozess startet. Dabei wird der komplette Zustand des gerade noch laufenden Prozesses (Daten in Registern, Befehlszähler, Prozesscounter, Seitentabelle ...) im Hauptspeicher zwischengespeichert.

Anschließend wird der Zustand des neuen Prozesses geladen und die CPU beginnt mit dessen Ausführung. Bei einem Kontextwechsel können Daten im TLB (translation lookaside buffer) ungültig werden und dieser muss unter Umständen geleert werden. In Abschnitt 2.4.1 wird näher auf den TLB eingegangen. Die Dauer eines Kontextwechsels schwankt je nach verwendeter Prozessor-Architektur und Betriebssystem zwischen 1300 ns und 1900 ns [Sig10].

## 2.4 Architektur moderner x86-64-Mehrkernprozessoren

Früher hatten Prozessoren nur einen Kern mit einer CPU verbaut. Seit 2005 gibt es bereits x86-Architekturen mit zwei Kernen in einem Prozessor auf dem Markt [amd04]. Heutige Prozessoren besitzen häufig mehr als nur zwei Kerne und jedes Jahr erscheinen neue Prozessoren mit immer mehr Kernen. Aktuelle Serverprozessoren der Ivy Bridge-EP Prozessorfamilie besitzen bis zu zwölf physische Kerne und mit aktiviertem Hyper-Threading entspricht das 24 logischen CPUs [int13b].

Hyper-Threading ist die Intel-Bezeichnung für Simultaneous Multithreading (SMT) – einer Vorstufe zu echten Mehrkernprozessoren. Dabei besitzt ein Kern zwar nur eine Recheneinheit (ALU und FPU), legt aber einige CPU-Ressourcen, wie Registersätze für beispielsweise Stackpointer und Programmcounter mehrfach aus. Dadurch können pro Kern mehrere Prozesse echt parallel ausgeführt werden, wenn sie auf Ressourcen zugreifen, die im gleichen Kern gerade nicht durch einen anderen Prozess auf einer anderen CPU belegt sind. Dazu werden die Instruktionsfolgen der Prozesse in kleinere Teile (Micro-Ops) zerlegt, die eine bessere Aufteilung auf mehrere logische CPUs ermöglichen. Im Multitasking-Betrieb kann diese Technik bis zu 20 Prozent mehr Performance bringen.

Heutige Prozessoren sind in der Regel alle 64 Bit-Architekturen. Zu den bekanntesten Vertretern gehören beispielsweise die Firmen Intel (IA-64 Architektur und Intel 64 Architektur), AMD (x86-64/AMD64 Architektur) und IBM (POWER). AMD64 ist vollständig kompatibel zu der 32-Bit-Architektur x86 und enthält einige zusätzliche Modifikationen, um mehr als vier GB Speicher adressieren zu können:

- 64-Bit physischer Adressraum

- Erweiterung der vorhandenen General-Purpose Register (GPR) auf 64 Bit

- weitere acht GPRs (R8 - R15)

- Erweiterung um acht SSE-Register (XMM8 - XMM15)

- 64 Bit-Befehlszeiger (RIP) mit relativer Adressierung

Mit Hilfe eines Kontroll-Bits LMA (long mode active) lässt sich die Betriebsart des Prozessors von 32 Bit auf 64 Bit zur Laufzeit ändern, was dem Prozessor ermöglicht auch unter einem 64-Bit-Betriebssystem 32-Bit-Anwendungen zu starten.

Neben den durch die Anwendungen selbst verwalteten Registern, die sehr klein sind und eine typische Kapazität von <1 KB besitzen, gibt es in heutigen Prozessorarchitek-

turen noch größere Speicher – die Caches. Diese werden hauptsächlich von der Hardware selber gesteuert und angesprochen. Die Größe der Caches kann auf aktuellen Chips mehr als zehn MB überschreiten (beispielsweise 30 MB L3-Cache beim Intel E5-2697 v2 Prozessor [int13b]). Diese Speicher werden als Zwischenspeicher für häufiger verwendete Daten aus dem Hauptspeicher genutzt, da ein Zugriff auf den Cache deutlich schneller ist, als ein Zugriff auf den Hauptspeicher selbst. In der Regel reichen für den Zugriff auf den L1-Cache 2-3 CPU-Takte aus.

Bei Prozessor-Architekturen mit Caches wird der Hauptspeicher in Blöcke von typischerweise 64 Byte Größe eingeteilt. Diese Größe entspricht der Breite einer Cache-Line. Die am häufigsten gebrauchten Speicherblöcke, auf die ein Prozess zugreift, werden in den L1-Cache kopiert. Reicht der Platz im L1-Cache nicht aus, wird eine Cache-Line in den L2-Cache verdrängt. Diese beiden Caches liegen sehr nahe an der CPU und sind meistens pro physischen Kern mehrfach auf einem Prozessor vorhanden. Eine Hierarchieebene höher liegt der L3-Cache und häufig wird dieser bei den heutigen Architekturen (Intel Core i7 und AMD Phenom II) von allen Prozessorkernen gemeinsam benutzt. Dies muss aber nicht immer der Fall sein. Der L3-Cache ist als Puffer für die aus dem L2-Cache verdrängten Cache-Lines aktiv und bildet die letzte Stufe der Cache-Hierarchie. Den letzten Cache vor dem Hauptspeicher nennt man auch Last Level Cache (LLC).

Wird ein Speicherwort von einem Programm gelesen, so überprüft die Puffer-Hardware, ob der entsprechende Block bereits in einem der Caches vorhanden ist. Wenn das der Fall ist, so spricht man von einem Cache-Hit. Befindet sich der Block nicht in dem Cache (Cache-Miss), so muss dieser aus dem Hauptspeicher geladen werden. Dabei erfolgen die Zugriffe auf den Cache und den Hauptspeicher gleichzeitig, um bei einen Cache-Miss die Verzögerungen des Speicherzugriffs minimal zu halten. Ein Zugriff auf einen Cache wird mit Cache-Reference bezeichnet. Cache-References können nur auftreten, wenn ein Cache-Miss in der darunter liegenden Hierarchie-Ebene stattgefunden hat. Ein Cache-Reference führt immer zu einem Cache-Hit oder zu einen Cache-Miss in der entsprechenden Hierarchie-Ebene. Das Verhältnis aus Cache-Hits zu Cache-References heißt Hit-Verhältnis und das Verhältnis aus Cache-Misses zu Cache-References analog dazu Miss-Verhältnis.

Man spricht von einem „kalten“ Cache, wenn Daten eines Prozess noch nicht im Cache stehen. Läuft ein Prozess längere Zeit auf einer CPU, so füllt sich der Cache nach und nach mit den Daten auf die der Prozess häufiger zugreift und der Cache wird „heiß“.

### 2.4.1 Paging und MMU

Um dem großen Speicherbedarf von einigen Programmen zu begegnen, unterstützen heutige x86-Prozessoren alle Paging. Das ist eine Technik um den virtuellen Adressraum für Prozesse zu erhöhen. Wenn in einem System für die Ausführung eines Prozesses nicht genügend physischer Hauptspeicher zur Verfügung steht, so kann mit Paging ein Teil der gerade nicht benutzten Daten im Hauptspeicher zeitweise auf die Festplatte ausgelagert werden. Virtuell stehen dem Programm somit mehr Speicheradressen und damit ein größerer Adressraum zur Verfügung.

Beim Paging wird der vorhandene physische Speicher in Einheiten fester Größe (typischerweise 512 Byte bis 64 KB) eingeteilt. Diese werden Seitenrahmen genannt. Seitenrahmen werden mit Seiten gefüllt. Seiten sind genauso groß, wie Seitenrahmen und bilden den virtuellen Adressraum ab. Bei knappem physischem Speicher werden Seiten aus ihrem Seitenrahmen verdrängt und auf die Festplatte ausgelagert.

Der Teil eines Computersystems, welcher virtuelle Adressen auf physische Adressen abbildet, nennt sich MMU (memory management unit). Dieser befindet sich in der Regel innerhalb der CPU. Um die Aufgabe der Adressübersetzung durchführen zu können, verwaltet die MMU eine Seitentabelle. Diese speichert zu jeder virtuellen Seite ab in welchem Seitenrahmen sie sich befindet oder ob die Seite ausgelagert wurde. Bei einem Speicherzugriff auf eine ausgelagerte Seite spricht man von einem Seitenfehler (page fault). Bei einem Seitenfehler ist es die Aufgabe des Betriebssystems einen wenig benutzten Seitenrahmen auszuwählen und dessen Seite auf der Festplatte zu sichern. Danach muss die angeforderte Seite in den frei gewordenen Seitenrahmen geladen werden und der Zugriff auf die Seite wird wiederholt. Um die Suche in der Seitentabelle zu beschleunigen wird je nach CPU-Architektur ein TLB verwendet. Der TLB ist ein kleiner mehrstufiger Assoziativspeicher, der häufig benutzte virtuelle Speicheradressen auf physische Speicheradressen abbildet. Damit lassen sich wiederholende Zugriffe auf die Seitentabelle einsparen.

Die meisten Cache-Architekturen nutzen virtuell adressierten Cache, da diese einfacher schneller Cache-Hits liefern. Für physisch adressierten Cache muss die MMU zwingend zwischen CPU und Cache liegen. Da diese aber für die Adressübersetzung mehrere Speicherzugriffe benötigt, verlangsamt das die Suche im Cache erheblich.

## 2.5 Performance-Counter

Eine wiederkehrende Frage in der Softwareentwicklung ist: Welche Leistung erreicht ein Programm oder Algorithmus auf einer vorgegebenen Hardware? Besonders bei sehr teuren Supercomputern, wo jeder unnötige CPU-Takt eingespart werden muss und Forscherteams sehr viel Zeit in die Optimierung ihres Codes stecken, um das Maximum an Performance (performance = Leistung) aus einem System herauszuholen, ist dieses zentrale Thema von großer Bedeutung.

Moderne x86-Prozessen besitzen schon seit mehreren Generationen Performance-Counter. Das sind zusätzliche Logikeinheiten, die direkt als Schaltkreise in der Hardware integriert sind, um hardwarenahe Operationen oder Ereignisse (events) verfolgen zu können. Solche CPU-Einheiten werden performance monitoring units (PMU) genannt und sind bei Intel seit Einführung der ersten Pentium-Prozessoren auf allen x86-Prozessoren vorhanden. Die Register zur Steuerung und zum Auslesen der Performance-Counter sind bei x86-Prozessoren im MSR (model-specific register) untergebracht. Nicht alle Prozessoren besitzen die gleiche Menge an Performance-Countern. Deshalb spricht man im Allgemeinen von modellspezifischen Performance-Countern.

Es gibt zwei Arten von messbaren Größen für Performance-Counter. Entweder man zählt die Anzahl des Auftretens von Ereignissen oder es wird die Dauer eines fest definierten Zustands in Prozessortakten gezählt.

Performance-Counter können genutzt werden, um zum Beispiel die Gesamtanzahl der ausgeführten CPU-Operationen, die Anzahl der durchgeföhrten Fließkommaoperation oder die Anzahl an Operationen aus dem erweiterten Befehlssatz SSE oder MMX zu zählen. Auf Prozessoren mit integrierten Caches gibt es weitere Anwendungsfälle. So lassen sich beispielsweise auch die absolute Anzahl der Cache-Misses bzw. Cache-References zur Laufzeit eines Programms verfolgen. Je kleiner das Miss-Verhältnis ausfällt, desto „besser“ läuft ein Programm und man kann Rückschlüsse auf die Performance ziehen. Es gibt jedoch auch Anwendungsfälle, wo genau das Gegenteil gewünscht ist. Dann werden Daten gezielt am Cache vorbeigeschrieben, um dessen Inhalt nicht zu gefährden und dadurch die Performance zu steigern.

Der Zugriff auf die MSRs (Register im MSR) ist nur im Kernel-Modus erlaubt, was zur Folge hat, dass normale Benutzer-Prozesse auf Systemaufrufe oder andere Schnittstellen des Betriebssystems angewiesen sind, um auf die entsprechenden Register zugreifen zu können.

### 2.5.1 MSRs in x86-Intel-Prozessoren

Intel-Prozessoren verfügen über eine Reihe von Performance-Countern, die in unterschiedliche Versionen eingeteilt sind. Ob und wie viele Versionen ein bestimmter Prozessor besitzt, lässt sich über die Instruktion cpuid auslesen [int11]. In der Version der ersten Generation „architectural performance monitoring version 1“ stehen je nach Modell mindestens zwei programmierbare Performance-Counter zur Verfügung. Um einen Performance-Counter zu starten, muss vorher über ein spezielles Auswahlregister (performance event select register IA32\_PERFEVTSELx MSR) die Auswahl der zu messenden Kenngröße (performance event) festgelegt werden. Zu jedem Performance-Counter gehören genau ein Auswahlregister und ein Zählregister (IA32\_PMCx MSR). Die Bitbreite der Zählregister ist Architektur- und Modell-pezifisch. Die Register-Adressen sind jedoch über alle Prozessor-Modellreihen konstant. Bei der Programmierung der MSRs kann man angeben, ob der Counter nur im Kernel- und/oder auch im Benutzer-Modus mitzählen soll. Je nach ausgewählten performance event zählen die Counter Ereignisse, die nur einen Kern betreffen, oder aber es werden Ereignisse außerhalb eines Kerns gezählt (offcore).

Die zweite Version der Performance-Counter „architectural performance monitoring version 2“ besitzt ferner ein globales Kontrollregister (IA32\_PERF\_GLOBAL\_CTR), das Steuersignale für alle Performance-Counter bereithält, um ein einfacheres Ansteuern der Performance-Counter zu ermöglichen. Zusätzlich stehen drei nicht programmierbare Performance-Counter (IA32\_FIXED\_CTR0 – IA32\_FIXED\_CTR2) mit einer fixen Funktion zur Verfügung, die ebenfalls über das globale Kontrollregister gesteuert werden können. Für das Verfolgen von Überläufen in den Zählregistern steht ein globales Statusregister (IA32\_PERF\_GLOBAL\_STATUS) zur Verfügung.

Ab der dritten Version der Performance-Counter „architectural performance monitoring version 3“ werden logische CPUs und Hyper-Threading in Prozessor-Kernen unterstützt. Prozessoren der aktuellen Core-i7-Generation verfügen über acht programmierbare MSRs pro Kern, die gleichmäßig auf die vorhandenen CPU-Threads aufgeteilt werden. Das ergibt bei aktiviertem Hyper-Threading vier programmierbare Performance-Counter pro logische CPU. Wird Hyper-Threading im Prozessor deaktiviert oder generell nicht unterstützt (beispielsweise bei der Intel Core 2 Modell-Reihe), so stehen bis zu acht programmierbare Performance-Counter pro logische CPU zur Verfügung. Die Bitbreite der Zählregister der Performance-Counter beträgt bei Prozessoren der Intel Core-i-Baureihe 48 Bit. Daraus ergibt sich für einen Zähler, der bei null

anfängt zu zählen das Erreichen des Überlaufs nach  $2^{48}$  Taktzyklen, wenn jeder Takt den Zähler inkrementiert. Bei einer Taktfrequenz von beispielsweise drei GHz wäre die Überlausfsituation damit nach  $2^{48}/(3 \times 10^{12}) \sim 93$  Sekunden erreicht. Ein Überlauf wird im Status-Register des Performance-Counters durch ein Bit angezeigt.

## 2.6 Performance-Counter in Linux

Die Unterstützung für Performance-Counter im Linux-Kern für die x86-Architektur wurde erstmals mit dem `perfctr`-Patch durch Mikael Pettersson von der Uppsala Universität im Jahre 1999 eingeführt. Damals musste man den Linux-Kern noch selber patchen und eine allgemeine Verfügbarkeit gab es nicht [Wea13].

Erst im Jahr 2009, nach der Einführung von `perfmon2` – einem generischen Interface für die IA64-Itanium-Architektur, wurden Anstrengungen unternommen Performance-Counter Unterstützung direkt in den x86-Kernel einzupflügen. Ab dem Linux-Kern v2.6.31 wurde die durch Ingo Molnar und Thomas Gleixner entwickelte `perf_event`-Schnittstelle in den Linux-Kern aufgenommen. Die Schnittstelle bietet einige wichtige Funktionen und Vorteile:

- `sys_perf_event_open()`-Systemaufruf für das Konfigurieren von Performance-Countern durch Benutzer-Prozesse

- über die `perf_event_attr`-Struktur wird angegeben, welche Ereignisse von dem Performance-Counter erfasst und gezählt werden

- mit Hilfe von `ioctl()`-Aufrufen können Performance-Counter gestartet und gestoppt

- das Auslesen der Zähler der Performance-Counter erfolgt mit `read()`

Die meisten Linux-Distributionen bieten mit dem Programm `perf` ein vollständiges Performance-Analyse-Tool an, das mit der `perf_event`-Schnittstelle arbeitet.

### 2.6.1 Die `perf_event`-Schnittstelle im Linux-Kern

Der große Vorteil von `perf_event` ist die einheitliche Form beim Umgang mit Performance-Countern. Es wird von der konkreten Prozessor-Architektur abstrahiert

und damit eine generalisierte und standardisierte Form für die Konfiguration und das Auslesen der Zählerstände der Performance-Counter präsentiert. Mit `perf_event` übernimmt der Linux-Kern die Kontrolle über das Zuordnen von Ereignissen zu passenden Zählern. Damit ergeben sich auch Möglichkeiten für Zeit-Multiplexing. Das bedeutet, wenn gleichzeitig mehr Ereignisse verfolgt werden sollen, als Performance-Counter zur Verfügung stehen, so kann mit Hilfe von verkürzten Zeitfenstern Ereignis-Zähler nur teilweise aufgenommen werden und dann auf die Werte der Gesamtzeit extrapoliert werden. Je nach Ereignis und Prozess ist dies ein gewünschter Ansatz, kann natürlich aber auch hinderlich sein.

Da Performance-Counter nur Ereignisse pro Kern zählen gibt es bei einem System mit mehreren parallel laufenden Prozessen keine Garantie, dass die Zählerstände nur von einem Prozess verursacht wurden. Deshalb speichert `perf_event` die Zählerstände eines Prozesses bei jedem Kontextwechsel, um die tatsächliche Werte nur eines Prozesses zu ermitteln. Daraus ergibt sich ein gewisser Overhead in Form von bis zu 20% längeren Kontextwechselzeiten [Wea13]. Bei Prozessen mit vielen Kontextwechseln sollte das beim Auswerten der Messwerte immer berücksichtigt werden.

Neben den tatsächlich durch die Hardware verursachten Ereignissen bietet `perf_event` ebenso die Möglichkeit softwareseitig durch den Linux-Kern verursachte Ereignisse mitzuzählen. Dazu zählen zum Beispiel das Verfolgen der aufgetretenen Kontextwechsel oder die Anzahl der Seitenfehler beim Referenzieren des virtuellen Speichers. Diese Kenngrößen sind ebenfalls interessant, wenn man beispielsweise die Performance des Betriebssystems messen möchte.

## 2.7 Linux Kernel-Entwicklung und Kernel-Module

Linux ist eine freie Software und aufgrund der GPL (GNU Public License) ist der Quellcode des Kernels frei zugänglich [Fre07]. Es ist gänzlich unmöglich für einen einzelnen Menschen den kompletten Code eines solch komplexen Betriebssystems alleine zu schreiben und zu pflegen. Und obwohl der Quellcode der ersten Version von Linux 0.0.1 im Jahr 1991 noch komplett durch Linus Torvalds allein geschrieben wurde, arbeitet heute eine ganze Community aus mehreren hunderten Programmierern am Linux-Kern [Tor01].

Jeder Interessierte kann den vollständigen Quellcode aus dem Git-Repository herunterladen und Änderungen in Form von Patches einreichen. Jedoch entscheidet eine Handvoll von langjährig an der Entwicklung beteiligten Programmierern um Torvalds

herum, welche Änderungen letztendlich in den offiziellen stabilen Linux-Kern aufgenommen werden [lif13]. Das hindert aber Niemanden daran eigene Funktionen und Erweiterungen in den Linux-Kern für Testzwecke oder den eigenen Gebrauch einzubauen, denn der Kernel ist sehr gut dokumentiert und modular aufgebaut.

Der Quellcode des Kernels ist aufgeteilt auf mehrere tausend Dateien und kann mit dem gcc-Compiler kompiliert werden. Zu allen Bereichen gibt es Textdateien mit Anleitungen und Erklärungen zum Verständnis.

Obwohl der Linux-Kern ein monolithischer Kernel ist, kann dieser dynamisch Kernel-Binaries in Form von Kernel-Modulen laden und ausführen. Viele Teile des Kernels lassen sich in Kernel-Module auslagern, wenn diese nicht dauerhaft für Funktionen des Betriebssystems genutzt werden. Durch eine Konfigurationsdatei lässt sich festlegen, welche Teile des Kerns als Kernel-Modul zur Verfügung stehen sollen.

Es gibt einige Einschränkungen, die man als C-Entwickler beim Arbeiten mit dem Linux-Kern beachten muss und die für die Implementierung von neuen Kernel-Funktionen nicht außer Acht gelassen werden dürfen [Lov05]:

- Der Kernel bindet keine Standard-C-Bibliothek ein, womit viele übliche C-Funktionen nicht zur Verfügung stehen.

- Es gibt keinen Speicherzugriffsschutz, wie bei Benutzer-Prozessen. Bei einem illegalen Speicherzugriff im Kernel kann ein kritischer Kernelfehler Oops auftreten.

- Es werden keine Fließkommazahlen im Kernel unterstützt, da die Umschaltung von Integer- zu Floating-Point-Befehlssatz auf unterschiedlicher Hardware individuell geregelt ist.

- Der Kernel-Stack ist relativ klein und statisch und deshalb sollten größere Mengen an statischer Speicherallokation vermieden werden.

- Im Kernel gibt es viele Ressourcen, die aufgrund von Präemptierung, asynchronen Unterbrechungen und mehrfachen Zugriff besonders geschützt sein müssen. Wettsituations (race condition) treten sehr häufig auf und müssen durch Maßnahmen, wie Semaphore, Locks oder Mutex strikt vermieden werden.

## **2.8 Verwandte Arbeiten**

Um die Fähigkeiten zur Parallelität von Mehrkernprozessorsystemen besser auszunutzen, werden mehrere Ansätze verfolgt. Die meisten Arbeiten konzentrieren sich auf

Techniken und Methoden, um die Abarbeitung von Single-Thread Anwendungen zu beschleunigen (Speedup) [VIA05]. Da solche Anwendungen nicht darauf ausgelegt sind, mehrere CPUs eines Prozessors parallel zu benutzen, gibt es zwei Möglichkeiten. Ein trivialer Ansatz ist es die Anwendungen direkt anzupassen. Dazu muss der Quellcode allerdings vorliegen und eine Neukompilierung ist notwendig. Eine weitere besonders gut geeignete Technik, um speicherintensive Anwendungen zu beschleunigen, ist das Prefetching durch Hilfs-Threads [CSR99] [ZS01] [KLW04].

Für Prefetching mittels Hilfs-Threads werden spezielle Threads gestartet, die zukünftige Speicherzugriffe vorausberechnen und die demnächst benötigten Daten näher an die CPU - d.h. in einen CPU-nahen Cache - bringen, um potentielle Cache-Misses bei der Ausführung des Haupt-Threads der (Single-Thread) Anwendung zu verhindern. Für Prozessorarchitekturen mit SMT ist es sinnvoll Hilfs-Threads auf einer weiteren logischen CPU im gleichen Kern zu starten, auf dem in einer anderen logischen CPU der Haupt-Thread ausgeführt wird. Der Grund ist, dass alle logischen CPUs eines Kerns den Cache aller Cache-Ebenen teilen und damit die Daten bis in den L1-Cache vorgeladen werden können. Diese Methode setzt SMT voraus und ist damit nur bedingt anwendbar. Bei Mehrkernprozessorsystemen ohne SMT müssen Hilfs-Threads daher auf einem anderen Kern des Prozessors, als der Kern auf dem der Haupt-Thread ausgeführt wird, gestartet werden. Steht in einem solchen Fall ein geteilter inklusiver L3-Cache zur Verfügung, so sind die Daten immerhin in dem L3-Cache vorhanden und müssen nicht teuer aus dem Speicher geholt werden.

Gibt es keinen geteilten Cache, so kann man, wie in der Arbeit [KST11] vorgeschlagen wird, mittels Inter-core Prefetching mit einer Migration des Haupt-Threads zu dem Kern, auf dem der Hilfs-Threads ausgeführt wurde, trotzdem einen Speedup erzielen. Ausschlaggebend für die Performancesteigerung ist die Größe der durch den Hilfs-Thread vorgeladen Daten und die Zeit für einen Kontextwechsel bei einer Migration des Haupt-Threads. Es sollten nur so viele Daten vorgeladen werden, wie einem Kern an exklusiven Cache zur Verfügung steht. Ansonsten werden die vorgeladenen Cache-Lines noch vor der Migration des Haupt-Threads schon wieder verdrängt und stehen dem Haupt-Thread anschließend nicht zur Verfügung. Die direkten Migrationskosten sollten möglichst gering sein, damit das Migrieren des Haupt-Threads nicht zur kritischen Komponente bei der Ausführung wird.

Idealerweise sollte der Hilfs-Threads nur solche Daten vorladen, die nicht gleichzeitig vom Haupt-Thread benötigt werden, um Cache-Synchronisations-Problemen aus dem Weg zu gehen und den Datenverkehr zwischen den Caches so gering wie möglich zu halten. Lässt sich eine Anwendung in Ausführungsabschnitte, bei der für einen festen Zeitraum nur eine begrenzte Arbeitsmenge zu erwarten ist, die der exklusiven Cache-

Größe eines Kerns entspricht, so kann mittels Inter-Core Prefetching signifikante Performance-Gewinne erzielt werden [KST11]. Der Main-Thread kann auf den Daten der ersten Arbeitsmenge arbeiten, während der Hilfs-Thread die Daten der nächsten Arbeitsmenge in den Cache des anderen Kerns vorlädt. Sobald beide mit ihrer Arbeit fertig sind, migrieren beide Threads zum jeweils anderen Kern und setzen dort ihre Arbeit fort. In diesem Fall findet der Haupt-Thread einen komplett „heißen“ Cache vor und kann ohne Verzögerungen arbeiten. Der Hilfs-Thread lädt wieder die nächste Arbeitsmenge vor.

Die Herausforderung liegt in der Generierung der Hilfs-Threads. Diese müssen entweder von Hand erstellt, oder mit speziellen Compilern-Techniken dynamisch oder mit Unterstützung von Profilingwerkzeugen generiert werden. Eine andere Möglichkeit ist die Generierung von Hilfs-Threads komplett in Hardware. Auf heutigen x86-Prozessoren ist dies bisher nicht möglich.

### **2.8.1 Vergleich Inter-Core Prefetching mit Migration Sweetspots**

Inter-core Prefetching ermöglicht einen Speedup von Single-Thread Anwendungen, durch Ausnutzung von freien Rechenkapazitäten in Kernen, die sonst ungenutzt bleiben würden. In Überlastsituationen, wenn mehrere Anwendungen parallel laufen, wird allerdings durch die zusätzliche Rechenlast für die Ausführung der Hilfs-Threads die Gesamtparformance des Systems beeinträchtigt. Auch kann die Ausführung von weiteren speicherintensiven Anwendungen, die den Großteil des Caches eines Kerns ebenfalls für sich beanspruchen dazu führen, dass der Haupt-Thread auf einem Kern keinen Nutzen durch die Arbeit des Hilfs-Threads erfährt. Der „heisse“ Cache wird sofort durch die speicherintensive Anwendung wieder zerstört.

Migration Sweetspots bieten den Vorteil, dass sie besonders in Überlastsituationen eine bessere Verteilung der Rechenkapazität ermöglichen. Anwendungen werden so lange auf einer CPU ausgeführt, bis eine Überlastsituation auf eben dieser entsteht. Bei voller Auslastung der CPU, kann ein speicherintensiver Prozess unter Minimierung der indirekten Migrationskosten an einem Migration Sweetspot auf eine weniger belastete CPU migrieren. Dadurch wird die Anwendung durch die Migration nicht sonderlich ausgebremst und kann auf der anderen CPU ungehindert schneller ausgeführt werden, als dies auf der alten CPU der Fall wäre.

Beide Verfahren können in jeweils unterschiedlichen Situationen angewendet werden. So lange keine Überlastsituation auf einer der für das Inter-core Prefetching genutzten CPUs durch das Scheduling von weiteren Prozessen eintritt, ist eine zusätzli-

che Suche nach Migration Sweetspots nicht nötig. Ist dies nicht mehr der Fall, sollte Inter-core Prefetching deaktiviert werden und der Scheduler könnte mittels Migration Sweetspots Anwendungen auf unterschiedliche CPUs verteilen und so die Überlast lösen und gleichzeitig für optimale Ausführungsbedingungen für alle beteiligten Prozesse sorgen.

## 3 Entwurf

In diesem Kapitel werden die Einzelheiten und Designentscheidungen zum Vorgehen zur Suche von Migration Sweetspots in Linux vorgestellt. Dazu erfolgt im ersten Abschnitt 3.1 die Definition und theoretische Betrachtung der Migrationskosten, die bei einer Migration eines Prozesses entstehen. Am Beispiel einer Matrixmultiplikation wird im Abschnitt 3.2 die positive Wirkung von Migration Sweetspots für die Miss-Rate nach der Migration eines Prozesses gezeigt.

Im Abschnitt 3.3 werden dann die Anforderungen für eine erfolgreiche Suche nach Migration Sweetspots zusammengetragen. Eine Strategie zur Implementierung der Suche nach Migration Sweetspots wird in Abschnitt 3.4 gewählt. Auf die Unterschiede zwischen einer Suche im Kernel- und Benutzer-Modus wird in Abschnitt 3.5 eingegangen. Der letzte Abschnitt 3.6 befasst sich mit den zeitlichen Schranken und Folgen für die Durchlaufzeit eines Prozesses bei einer Verzögerung der Migration, wegen einem Migration Sweetspot.

### 3.1 Theoretische Betrachtung

Zur Veranschaulichung des Sachverhalts der Migrationen von Prozessen, erfolgt zunächst eine Analyse in einem abstrahierten Computer-System mit nur zwei physischen Kernen mit jeweils einer CPU – CPU1 und CPU2.

Der in Linux implementierte Scheduler ab der Kernel-Version 2.6.23 ist ein Completely Fair Scheduler mit dynamischem Lastausgleich (load-balancing) [Aas05]. Das heißt, dass während der Laufzeit des Systems in regelmäßigen Abständen von n Zeiteinheiten ein Lastausgleich vorgenommen wird. Die Last einer CPU wird vom Scheduler in der Variable `cpu_load` als Attribut einer jeden Runqueue gespeichert. Bei jedem `scheduler_tick()`, das heißt einmal pro Jiffy-Intervall, erfolgt eine Neuberechnung der CPU-Last durch die Methode `rebalance_tick()`. Liegt der letzte Lastausgleich länger als n Zeiteinheiten zurück, so wird ein neuer Lastausgleich durchgeführt und ein neues Intervall beginnt. Um den Lastausgleich durchzuführen, laufen auf jeder CPU spezielle Kernel-Threads mit einer hohen Priorität. Befinden sich die CPUs bei

einem Lastausgleich bezüglich ihrer aktuellen CPU-Last in einem Ungleichgewicht, so werden Prozesse von einer Runqueue einer CPU mit hoher Last zu einer Runqueue einer CPU mit wenig Last verschoben. Dabei werden Prozesse aus dem **expired**-Array der Runqueue beginnend mit der niedrigsten Priorität bevorzugt verschoben.

Zur weiteren Analyse wird ein hypothetischer Fall angenommen, um die nachfolgenden Definitionen besser erklären zu können. Es wird eine Situation betrachtet bei der neben dem Kernel-Thread für den Lastausgleich und dem Leerlaufprozess nur ein weiterer Prozess auf dem System, dessen Laufzeit länger ist, als das Intervall für den Lastausgleich, läuft. Bei einem Lastausgleich wird angenommen, dass der Prozess von der CPU1 zu CPU2 migrieren wird. Die Zeit für die Migration ist Zeit die bei der Ausführung des Prozesses verloren gegangen ist. Diese Zeit soll direkte Migrationskosten genannt werden. Der Sachverhalt ist in Abbildung ... dargestellt.

### Direkte Migrationskosten

Unter direkten Migrationskosten versteht man die Zeit, die für die reine Migration eines Prozesses von einer CPU auf eine andere CPU vergeht. Während dieser Verzögerungszeit kann der Prozess nicht ausgeführt werden.

Direkte Migrationskosten entstehen beispielsweise nach einem Lastausgleich, wenn Prozesse einer Runqueue einer anderen CPU zugewiesen werden. Für aktiv von einer CPU ausgeführte Prozesse beinhalten die direkten Migrationskosten die Zeitspanne vom Eintritt in den Kern, die verstrichene Zeit für das Einplanen des Prozesses in den Scheduling-Plan auf der anderen CPU, einem anschließenden Kontextwechsel und schließlich die Zeitspanne vom Kernelaustritt.

Die direkten Migrationskosten sind abhängig von dem verwendeten Betriebssystem und der zu Grunde liegenden Prozessorarchitektur eines Systems. Durch die direkten Migrationskosten verlängert sich die Durchlaufzeit eines Prozesses. Abhängig vom Zustand der Runqueue auf der CPU nach der Migration, kommt zu den direkten Migrationskosten noch eine weitere Verzögerung hinzu, bis ein Prozess auf der CPU nach der Migration wieder ausgeführt wird. Diese Verzögerung lässt sich durch den Scheduler zumindest annähernd vor der Migration abschätzen, indem die Runqueue in die der Prozess verschoben wird analysiert wird. Alle Prozesse im **active**-Array und alle Prozesse im **expired**-Array mit einer höheren Priorität werden vor dem Prozess ausgeführt werden, da Prozesse bei der Migration immer in das **expired**-Array verschoben werden. Wenn all diese Prozesse ihr Quantum komplett ausnutzen, ergibt das die maximale Verzögerung.

Zusätzlich zu den direkten Migrationskosten müssen noch die indirekten Migrationskosten berücksichtigt werden. Nach der Migration sind der L1- und der L2-Cache auf der anderen CPU für den Prozess kalt, da beide Caches üblicherweise über das MOESI-Protokoll synchronisiert sind und die Daten des Prozesses noch in den Caches der alten CPU liegen [AMD11]. Bei einem gemeinsam genutzten L3-Cache können Lesezugriffe auf nicht modifizierte Cache-Lines immerhin ohne Zeitverzögerung aus dem L3-Cache geladen werden.

Aufgrund der Folge eines Kontextwechsels nach einer Migration ist auch der TLB für den Prozess anschließend kalt. Dies hat die größte Auswirkung auf die Durchlaufzeit des Prozesses, da alle Seitenzugriffe auf der anderen CPU zunächst mehrere Speicherzugriffe auf die Seitentabelle nach sich ziehen.

### **Indirekte Migrationskosten**

Bei indirekten Migrationskosten handelt es sich um die negativen zeitlichen Auswirkungen für die Durchlaufzeit eines Prozesses, die nach einer Migration des Prozesses auf eine andere CPU durch einen dort „kalten“ Cache verursacht werden.

Indirekte Migrationskosten können eine große Varianz aufweisen, abhängig von dem zum Migrationspunkt aktiven Prozesszustand. Die minimalen indirekten Migrationskosten ergeben sich für den Fall, dass ein Prozess nach der Migration auf keine Daten in den Cache-Lines vor der Migration zugreift. Nach einer Migration muss in jedem Fall auch der L1-Instruction-Cache auf der anderen CPU für den Prozess neu gefüllt werden und somit können die indirekten Migrationskosten nie gleich null sein.

Bei sehr hohen indirekten Migrationskosten muss der Prozess den Cache erst wieder „warm“ bekommen, damit die vor der Migration durch „heiß“ Caches begünstigte hohe Abarbeitungsgeschwindigkeit wieder erreicht werden kann. Der Scheduler hat ohne Modifikationen selbst keine Möglichkeit indirekte Migrationskosten im Voraus einer Migration abzuschätzen, da er dafür in den Algorithmus der Prozesse und die „Temperatur“ der Caches hineinsehen müsste. Dies ist keine Aufgabe, die der Scheduler in  $O(1)$ -Zeit bewältigen kann.

### **Migration Sweetspot**

Ist die Entscheidung gefallen, dass ein Prozess von einer CPU zu einer anderen migriert wird, so ist ein Migration Sweetspot ein Zeitpunkt an dem die direkten und indirekten Migrationskosten für den Prozess kleiner sind, als bei einer sofortigen Migration.

## 3.2 Vorteile von Migration Sweetspots

Generell sollten Migration von Prozessen zunächst vermieden werden. Ganz vermeiden lassen sie sich jedoch nicht. In einem Mehrkernprozessorsystem kann es zu einer ungleichen Lastverteilung kommen. In solchen Fällen ist es für die Abarbeitungsgeschwindigkeit aller Tasks von Vorteil Prozesse zu migrieren. Für den zu migrierenden Prozess ist eine Migration zu einem Migration Sweetspot am besten.

Aus dem vorherigen Abschnitt ist bekannt, dass die direkten Migrationskosten sich gut vorhersagen lassen. Die Verschiebung eines Prozesses in eine andere Runqueue ist konstant in einer endlichen Zahl von Taktzyklen machbar. Des Weiteren migriert ein Prozess fast immer zu einer weniger ausgelasteten CPU, weshalb die potentielle Verzögerung bis zur nächsten Ausführung des Prozesses ohnehin minimiert wird. Für die direkten Migrationskosten spielt es keine Rolle zu welchem Zeitpunkt ein Prozess auf eine andere CPU migriert.

Ein besserer Anhaltspunkt zur Senkung der Migrationskosten ist die Minimierung der indirekten Migrationskosten. Wie kann dies mit dem Wissen um die Probleme bei der Bestimmung der indirekten Migrationskosten erfolgen? Besonders bei speicherintensiven Prozessen, fallen die indirekten Migrationskosten im Vergleich zu den direkten Migrationskosten weitaus höher aus.

Es ist bekannt, dass der Scheduler kein Wissen über den Algorithmus des Programms, den ein Prozesses ausführt, besitzt. Aber wenn dem Scheduler ein einfaches Maß für die „Temperatur“ eines Caches bezüglich eines Prozesses zur Verfügung stehen würde, dann wäre eine grobe Abschätzung der indirekten Migrationskosten möglich. Ein einfaches Beispiel anhand eines Prozesses, der eine Matrixmultiplikation durchführt sollen die Vorteile von Migration Sweetspots gezeigt werden.

### 3.2.1 Beispiel mit einer Matrixmultiplikation

Zur einfacheren Berechnung wird für dieses Beispiel die Multiplikation von zwei quadratischen Integer-Matrizen der Größe [3; 3] gewählt. Die Größe sei so gewählt, dass die Elemente von einer Zeile der Matrix in eine Cache-Line passen. Es wird ferner angenommen, dass alle drei Matrizen  $A \bullet B = C$  komplett in den Cache-Speicher passen und am Anfang des Beispiels keine Daten der Matrizen bereits im Cache stehen. Die Elemente der Matrizen sind zeilenweise abgespeichert und alle drei Matrizen stehen

direkt hintereinander im Speicher. Die Bezeichnung der Elemente der Matrizen sei folgendermaßen.

$$A = \begin{bmatrix} A_1 & A_2 & A_3 \\ A_4 & A_5 & A_6 \\ A_7 & A_8 & A_9 \end{bmatrix} \quad B = \begin{bmatrix} B_1 & B_2 & B_3 \\ B_4 & B_5 & B_6 \\ B_7 & B_8 & B_9 \end{bmatrix} \quad C = \begin{bmatrix} C_1 & C_2 & C_3 \\ C_4 & C_5 & C_6 \\ C_7 & C_8 & C_9 \end{bmatrix}$$

Das Zwischenspeichern von temporären Variablen soll im Folgenden vernachlässigt werden. Der Grund ist zum einen die bessere Übersichtlichkeit und zum anderen gibt es auf modernen x86-Prozessoren einen FMA-Befehlssatz (FMU = fused multiply-add) der Instruktionen der Form  $r1 = r1 + r2 \times r3$  zulässt [int13a]. Das Zwischenspeichern der Multiplikation in einem separaten Speicherblock kann bei der Matrixmultiplikation damit entfallen. Es ergibt sich der Ablaufplan aus Tabelle 1 bei der Berechnung der Matrixmultiplikation. Es soll phasenweise die Belegung des Caches während der Berechnung der Elemente von  $C$  protokolliert werden. Dabei werden auch die Anzahl der Cache-Misses und der Cache-Hits pro Phase gezählt. Ein Strich (beispielsweise  $\overline{A}_1$ ) über einem Element soll einen Cache-Miss anzeigen. Die Berechnung wird von links nach rechts ausgeführt und bei einem Cache-Miss wird die Cache-Line mit den entsprechenden Speicherblock gefüllt.

**Tabelle 1: Ablaufplan einer Matrixmultiplikation ohne Migration**

| Phase                        | Berechnung                                                                              | Cache-Misses | Cache-Hits | Cache-Belegung                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                              |               |                              |               |                              |               |                              |               |                              |               |

|------------------------------|-----------------------------------------------------------------------------------------|--------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|---------------|------------------------------|---------------|------------------------------|---------------|------------------------------|---------------|------------------------------|---------------|

| 1                            | $\overline{A}_1\overline{B}_1 + A_2\overline{B}_4 + A_3\overline{B}_7 = \overline{C}_1$ | 5            | 2          | <table border="1"> <tr><td><math>\overline{A}_1 \rightarrow</math></td><td><math>A_1 A_2 A_3</math></td></tr> <tr><td><math>\overline{B}_1 \rightarrow</math></td><td><math>B_1 B_2 B_3</math></td></tr> <tr><td><math>\overline{B}_4 \rightarrow</math></td><td><math>B_4 B_5 B_6</math></td></tr> <tr><td><math>\overline{B}_7 \rightarrow</math></td><td><math>B_7 B_8 B_9</math></td></tr> <tr><td><math>\overline{C}_1 \rightarrow</math></td><td><math>C_1 C_2 C_3</math></td></tr> </table> | $\overline{A}_1 \rightarrow$ | $A_1 A_2 A_3$ | $\overline{B}_1 \rightarrow$ | $B_1 B_2 B_3$ | $\overline{B}_4 \rightarrow$ | $B_4 B_5 B_6$ | $\overline{B}_7 \rightarrow$ | $B_7 B_8 B_9$ | $\overline{C}_1 \rightarrow$ | $C_1 C_2 C_3$ |

| $\overline{A}_1 \rightarrow$ | $A_1 A_2 A_3$                                                                           |              |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                              |               |                              |               |                              |               |                              |               |                              |               |

| $\overline{B}_1 \rightarrow$ | $B_1 B_2 B_3$                                                                           |              |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                              |               |                              |               |                              |               |                              |               |                              |               |

| $\overline{B}_4 \rightarrow$ | $B_4 B_5 B_6$                                                                           |              |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                              |               |                              |               |                              |               |                              |               |                              |               |

| $\overline{B}_7 \rightarrow$ | $B_7 B_8 B_9$                                                                           |              |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                              |               |                              |               |                              |               |                              |               |                              |               |

| $\overline{C}_1 \rightarrow$ | $C_1 C_2 C_3$                                                                           |              |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                              |               |                              |               |                              |               |                              |               |                              |               |

| 2                            | $A_1B_2 + A_2B_5 + A_3B_8 = C_2$                                                        | 0            | 7          | ...                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                              |               |                              |               |                              |               |                              |               |                              |               |

| 3                            | $A_1B_3 + A_2B_6 + A_3B_9 = C_3$                                                        | 0            | 7          | ...                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                              |               |                              |               |                              |               |                              |               |                              |               |

|   |                                                        |   |   |                                          |

|---|--------------------------------------------------------|---|---|------------------------------------------|

| 4 | $\overline{A_4}B_1 + A_5B_4 + A_6B_7 = \overline{C_4}$ | 2 | 5 | $A_1 A_2 A_3$                            |

|   |                                                        |   |   | $B_1 B_2 B_3$                            |

|   |                                                        |   |   | $B_4 B_5 B_6$                            |

|   |                                                        |   |   | $B_7 B_8 B_9$                            |

|   |                                                        |   |   | $C_1 C_2 C_3$                            |

|   |                                                        |   |   | $\overline{A_4} \rightarrow A_4 A_5 A_6$ |

|   |                                                        |   |   | $\overline{C_4} \rightarrow C_4 C_5 C_6$ |

|   |                                                        |   |   |                                          |

| 5 | $A_4B_2 + A_5B_5 + A_6B_8 = C_5$                       | 0 | 7 | ...                                      |

| 6 | $A_4B_3 + A_5B_6 + A_6B_9 = C_6$                       | 0 | 7 | ...                                      |

| 7 | $\overline{A_7}B_1 + A_8B_4 + A_9B_7 = \overline{C_7}$ | 2 | 5 | $A_1 A_2 A_3$                            |

|   |                                                        |   |   | $B_1 B_2 B_3$                            |

|   |                                                        |   |   | $B_4 B_5 B_6$                            |

|   |                                                        |   |   | $B_7 B_8 B_9$                            |

|   |                                                        |   |   | $C_1 C_2 C_3$                            |

|   |                                                        |   |   | $A_4 A_5 A_6$                            |

|   |                                                        |   |   | $C_4 C_5 C_6$                            |

|   |                                                        |   |   | $\overline{A_7} \rightarrow A_7 A_8 A_9$ |

| 8 | $A_7B_2 + A_8B_5 + A_9B_8 = C_8$                       | 0 | 7 | ...                                      |

| 9 | $A_7B_3 + A_8B_6 + A_9B_9 = C_9$                       | 0 | 7 | ...                                      |

Während der Phase 1 gibt es aufgrund des „kalten“ Caches mehr Cache-Misses als Cache-Hits. Doch schon ab Phase 2 profitiert der Prozess von den Daten im Cache und es gibt weniger Cache-Misses. Nur noch vereinzelt in der Phase 4 und Phase 7 entstehen Verzögerungen durch je zwei Cache-Misses.

Bei einem Lastausgleich zum Anfang der Phase 2 erfolgt anschließend eine sofortige Migration des Prozesses zu einer anderen CPU. Der „warme“ Cache aus Phase 1 geht verloren und es ergibt sich ein neuer Ablaufplan, der in Tabelle 2 zu sehen ist.

**Tabelle 2: Ablaufplan einer Matrixmultiplikation mit Migration ohne Berücksichtigung von Migration Sweetspots**

| Phase                        | Berechnung                                                                                 | Cache-Misses | Cache-Hits | Cache-Belegung                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                              |               |                              |               |                              |               |                              |               |                              |               |

|------------------------------|--------------------------------------------------------------------------------------------|--------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|---------------|------------------------------|---------------|------------------------------|---------------|------------------------------|---------------|------------------------------|---------------|

| 1                            | $\overline{A_1} \overline{B_1} + A_2 \overline{B_4} + A_3 \overline{B_7} = \overline{C_1}$ | 5            | 2          | <table border="1"> <tr><td><math>\overline{A_1} \rightarrow</math></td><td><math>A_1 A_2 A_3</math></td></tr> <tr><td><math>\overline{B_1} \rightarrow</math></td><td><math>B_1 B_2 B_3</math></td></tr> <tr><td><math>\overline{B_4} \rightarrow</math></td><td><math>B_4 B_5 B_6</math></td></tr> <tr><td><math>\overline{B_7} \rightarrow</math></td><td><math>B_7 B_8 B_9</math></td></tr> <tr><td><math>\overline{C_1} \rightarrow</math></td><td><math>C_1 C_2 C_3</math></td></tr> </table> | $\overline{A_1} \rightarrow$ | $A_1 A_2 A_3$ | $\overline{B_1} \rightarrow$ | $B_1 B_2 B_3$ | $\overline{B_4} \rightarrow$ | $B_4 B_5 B_6$ | $\overline{B_7} \rightarrow$ | $B_7 B_8 B_9$ | $\overline{C_1} \rightarrow$ | $C_1 C_2 C_3$ |