# Belegarbeit

# **Evaluation of migration costs in multi-core CPU scheduling**

Stefan Wächtler

March 9, 2012

Technische Universität Dresden Fakultät Informatik Institut für Systemarchitektur Professur Betriebssysteme

Betreuender Hochschullehrer: Prof. Dr. rer. nat. Hermann Härtig

Betreuender Mitarbeiter: Ing. Michal Sojka Ph.D.

| Erklärung                                                                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------|

| Hiermit erkläre ich, dass ich diese Arbeit selbstständig erstellt und keine anderen als die angegebenen Hilfsmittel benutzt habe. |

| Dresden, den 9. März 2012                                                                                                         |

|                                                                                                                                   |

|                                                                                                                                   |

| Stefan Wächtler                                                                                                                   |

|                                                                                                                                   |

|                                                                                                                                   |

# **Contents**

| 1 | Intr | roduction                                                     |

|---|------|---------------------------------------------------------------|

| 2 | Fun  | ndamentals                                                    |

|   | 2.1  | Terms and definitions                                         |

|   |      | 2.1.1 Caches                                                  |

|   |      | 2.1.2 Cache-related preemption and migration delay            |

|   | 2.2  | Architectures used for measurements                           |

|   |      | 2.2.1 Intel Xeon X5650 (Dell system)                          |

|   |      | 2.2.2 Phenom 9550 (AMD system)                                |

|   | 2.3  | NOVA                                                          |

|   |      | 2.3.1 Capabilities                                            |

|   |      | 2.3.2 Protection Domains                                      |

|   |      | 2.3.3 Execution Contexts                                      |

|   |      | 2.3.4 Scheduling Contexts                                     |

|   |      | 2.3.5 Portals                                                 |

|   |      | 2.3.6 Semaphores                                              |

|   |      | 2.3.7 Threads                                                 |

|   | 2.4  | Miscellaneous                                                 |

|   |      | 2.4.1 System Management Mode                                  |

|   |      | 2.4.2 Time stamp counter                                      |

|   | 2.5  | Related Work                                                  |

| 3 | Des  | sign                                                          |

|   | 3.1  | Measurement of CPMD                                           |

|   | 3.2  | Data structures and access patterns of the measurement thread |

|   | 3.3  | Background load                                               |

|   |      | 3.3.1 Constructed background load                             |

|   |      | 3.3.2 Realistic background load                               |

|   | 3.4  | Experimental design                                           |

|   |      | 3.4.1 Memory access times                                     |

|   |      | 3.4.2 Accuracy of preemption length                           |

|   |      | 3.4.3 Preemption                                              |

|   |      | 3.4.4 Migration                                               |

| 4 | lmn  | plementation                                                  |

| - | 4.1  | Migration                                                     |

|   |      | 4.1.1 Setup phase                                             |

|   |      | 4.1.2 Migrations during execution time                        |

#### Contents

|     | 4.2<br>4.3<br>4.4 | Capturing of statistical data                            | 32<br>32<br>33 |

|-----|-------------------|----------------------------------------------------------|----------------|

| 5   | Eval              | uation                                                   | 35             |

|     | 5.1               | Classification of background load                        | 35             |

|     |                   | 5.1.1 Realistic background load                          | 35             |

|     |                   | 5.1.2 Constructed background load                        | 36             |

|     |                   | 5.1.3 Comparison of the used background loads            | 37             |

|     | 5.2               | Accuracy of preemption length                            | 37             |

|     | 5.3               | Experiments                                              | 38             |

|     |                   | 5.3.1 Cache/memory access times                          | 38             |

|     |                   | 5.3.2 Preemption                                         | 43             |

|     |                   | 5.3.3 Migration                                          | 47             |

| 6   | Cond              | clusion                                                  | 57             |

|     | 6.1               | Comparison to observations of Bastoni et al              | 57             |

|     | 6.2               | Factors influencing the costs of CPMD                    | 59             |

|     | 6.3               | Prediction of CPMD                                       | 60             |

|     | 6.4               | Derived scheduling decisions for the Dell and AMD system | 60             |

|     | 6.5               | Observations not presented in [BBA10a]                   | 61             |

|     | 6.6               | Summary and future work                                  | 62             |

| Α   | Mea               | sured CPMD costs                                         | 63             |

|     | A.1               | Xeon X5650                                               | 63             |

|     | A.2               | Phenom 9500                                              | 65             |

| Gle | ossar             |                                                          | 69             |

| R:  | bliogr            | anhy                                                     | 71             |

| UII | いいしだし             | aniia                                                    | 11             |

# **List of Figures**

| 2.1        | Example of the cache hierarchy in recent systems                        | 5        |

|------------|-------------------------------------------------------------------------|----------|

| 2.2        | Example of an $n$ -way set associative cache                            | 7        |

| 2.3        | Example of a preempted job                                              | 10       |

| 2.4        | Architecture Dell Precision T7500                                       | 11       |

| 2.5        | Structure of physical addresses to determine cache line                 | 12       |

| 3.1        | Plan of execution to measure the influence of CPMD                      | 19       |

| 3.2        | Measurement problems of $e_1$ in multi-core systems                     | 22       |

| 3.3        | Linked list as a data access structure                                  | 24       |

| 4.1        | Setup of a migratable thread                                            | 30       |

| 4.2        | Migration of a thread                                                   | 31       |

| 4.3        | Layout of the stack                                                     | 33       |

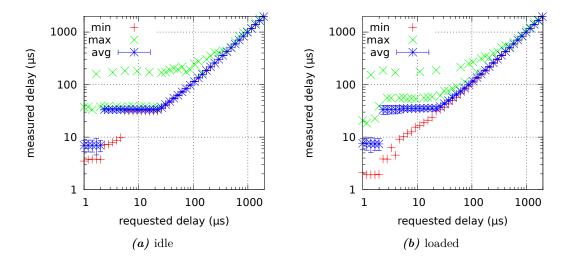

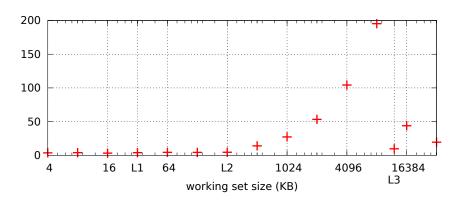

| 5.1        | Measured accuracy of the preemption delay                               | 38       |

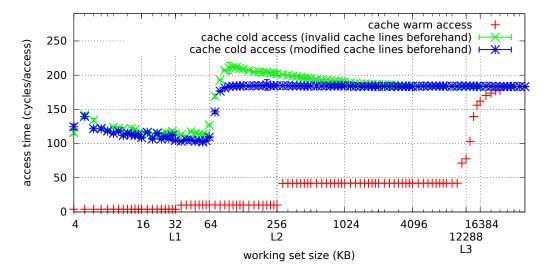

| 5.2        | Access times to the cache and local main memory (Xeon X5650)            | 39       |

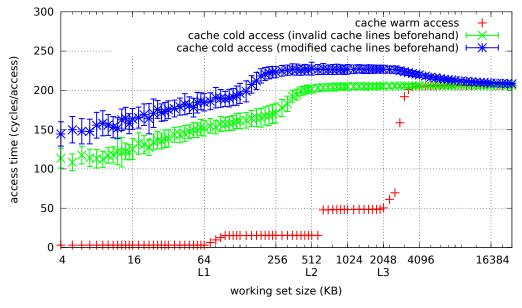

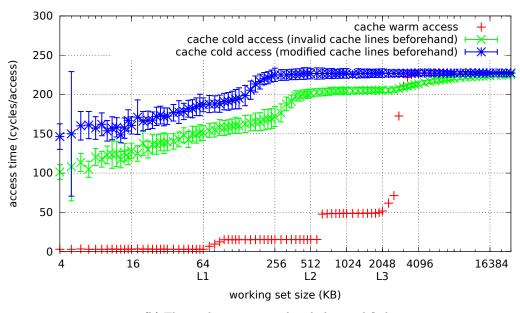

| 5.3        | Access times to the cache and main memory (Phenom 9550)                 | 41       |

| 5.4        | Delay caused by a preemption using the constructed background load      |          |

|            | (Xeon X5650)                                                            | 43       |

| 5.5        | Maximum costs of a preemption determined by the cache warm and cache    |          |

| - 0        | cold access times                                                       | 44       |

| 5.6        | Delay caused by a preemption using the realistic background load on one | , _      |

|            | core (Xeon X5650)                                                       | 45       |

| 5.7        | Delay caused by a preemption using the realistic background load on all | 4.0      |

| <b>F</b> 0 | cores (Xeon X5650)                                                      | 46       |

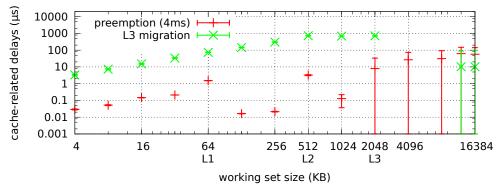

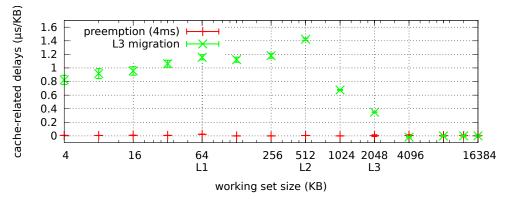

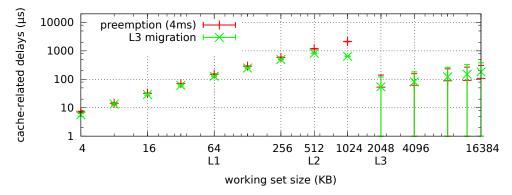

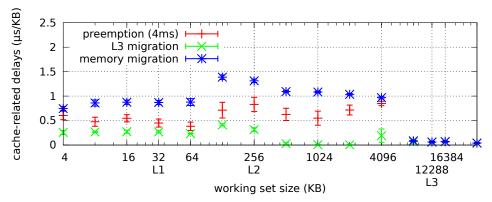

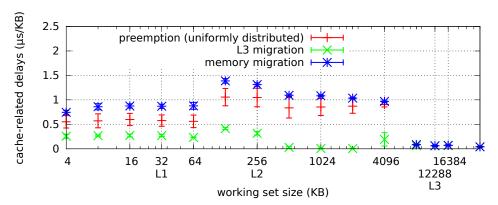

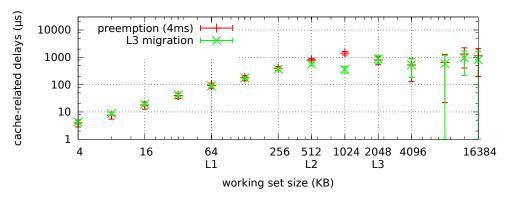

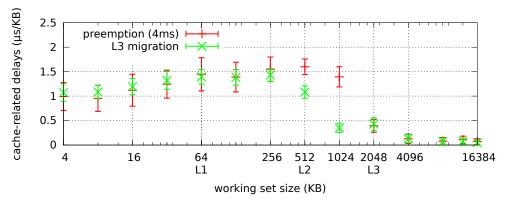

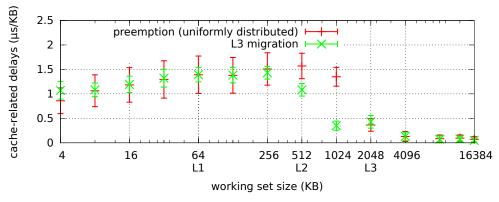

| 5.8        | Migration costs in an idle system (Xeon X5650)                          | 48       |

| 5.9        | Migration costs in an idle system (Phenom 9550)                         | 50       |

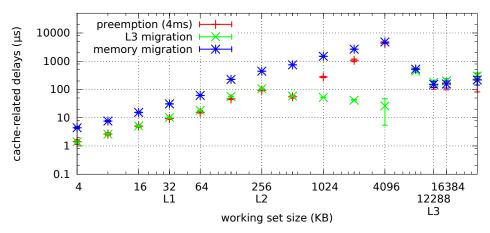

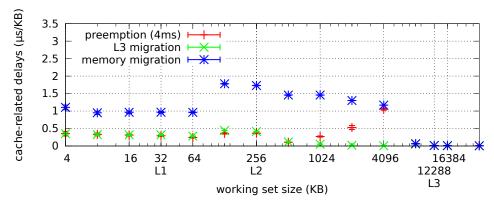

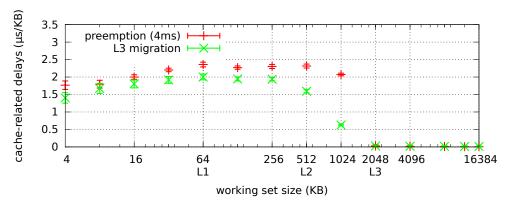

| 5.10       | Migration costs in a loaded system (Xeon X5650)                         | 51       |

| 5.11       | Ratio of the costs of a memory and L3 migration                         | 51       |

| 5.12       | U (                                                                     | 52       |

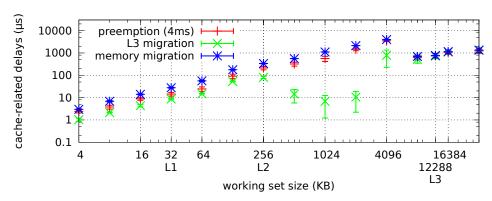

|            | Migration costs in a realistically loaded system (Xeon X5650)           | 54<br>55 |

| 0.14       | Migration costs in a realistically loaded system (Phenom 9550)          | 55       |

## 1 Introduction

Up to the middle of the last decade, the common approach to improve the performance of a CPU was to increase its clock rate. However, a higher clock rate correlates with the production of heat and, therefore, at some point in time it was necessary to come up with another principle to increase the overall performance: multi-core CPUs. Having independently working cores enables to run more than one task in parallel but brings new challenges to operating-system schedulers: Optimal real-time scheduling algorithms that provide scheduling guarantees in multi-core systems are NP-complete. Hence, they cannot be used in practice.

Optimal real-time scheduling algorithms for single cores are well studied and available (e.g. see [Liu00]), so a widely used approach for systems with n cores is to divide the set of all tasks into n distinct subsets. Each core in the system runs its own (single-core) scheduling algorithm with its own subset of tasks. This method is called Partitioned Scheduling [BBA10b]. Tasks are statically assigned to single cores and are not allowed to migrate. Another principle is called Global Scheduling: Tasks can freely migrate between all cores of the system. Mixtures of both principles are called Global Scheduling: Tasks and cores are divided into distinct subsets. Each subset of tasks is assigned to a specific subset of cores that runs its own scheduling algorithm.

However, when comparing the different approaches, the migration costs are often neglected, which is for practical purpose unacceptable. When searching for more efficient ways of multi-core scheduling, it is important to analyze the costs of task migrations. The costs consist of two parts – direct and indirect. Direct costs describe the necessary effort to transfer the values of the registers of the source CPU to the registers of the target CPU. The costs consist of a fixed number of copy operations to/from the memory and are independent of the migrated task. Consequently, direct costs can be estimated quite easily.

In contrast, the indirect costs are hard to quantify because they are influenced by many factors like the size of the task's memory working set, memory access pattern, whether the task was running or was preempted for some time, the cache/memory architecture of the system, the overall memory load in the multi-core system, etc.

The goal of this work is to experimentally evaluate the migration's indirect costs in a multi-core system. The costs are compared to those of a preemption using two different system architectures. The factors described above are varied to find their influences on migration costs. Having comparative values of preemption and migration costs, statements about the consequences of different scheduling decisions are possible. Furthermore, the prediction of these costs might help the system's scheduler to minimize the penalty of its decisions.

The next chapter of this work introduces the necessary basics and terminology that is important to understand the work. Special attention is turned to caches in addition to the used measurement systems. Furthermore, the operating system used in the experiments, called NOVA, is introduced.

Chapter 3 gives an overview of how the indirect migration costs can be measured and describes the design of one method in depth. An exemplary task capable of measuring preemption and migration costs is designed. Additionally, threads able to run as background load to simulate a loaded system are examined: One approach is able to generate reproducible results, the other one generates a realistic load. The last part of this chapter describes the design of the experiments that were carried out.

Some implementation details are given in Chapter 4. NOVA has no built-in support for migrations, so the implementation of a reliable mechanism and its limitations are presented. Especially the setup and execution of threads being able to migrate between cores of the system is in the scope of interest.

The evaluation of the measurements presented in Chapter 5 is one of the major parts of this work. The background loads are classified and cache-related costs that are introduced by a preemption or migration are discussed.

The last chapter compares the results of the evaluation with other published works and draws conclusions about possible scheduling decisions in multi-core systems.

### 2 Fundamentals

The first section of this chapter defines basic terms that are important within this work. Caches are introduced to define cache-related preemption and migration delays (CPMD). Afterwards, the architectures used during the measurements and some of their technical details are presented.

The third section deals with NOVA and some of its basic components. This section is of particular importance for the next chapters because terminology is introduced that is frequently used during this work.

Miscellaneous terms appearing from time to time like the time stamp counter (TSC) are covered in the fourth section. The last section of this chapter describes observations about CPMD made by Bastoni et al. [BBA10a].

#### 2.1 Terms and definitions

#### **2.1.1 Caches**

This section gives an introduction into caching techniques that are necessary to understand the principles of cache-related preemption and migration delays. Due to the complexity of caches not all details can be presented.

#### **Definition**

In general, caches are memories that store recently used data to serve future requests faster. The values in the cache are either earlier computed results or copies of values that are also stored elsewhere. This definition holds for software as well as for hardware caches.

For example, a software cache is used in a web browser to store the images of web pages a user has already visited. If the website is opened again, the cached images need not be retransmitted and, thus, the page will load faster.

The *CPU cache* is a typical hardware cache. It is a small and fast memory that stores data of main memory to speedup the accesses to that data on future reads.

To determine cache-related preemption and migration delays, CPU caches are in the scope of interest. Therefore the term cache will be used as a synonym for CPU caches throughout the work.

Originally, CPU caches were introduced to reduce the performance gap between the processor and main memory in von Neumann architectures. In these architectures the memory controller puts the memory address of a requested word on the address bus and the memory responds with the corresponding data on the data bus. Over the years, the clock rates of CPUs grew and the system's performance was determined by the

clock rate of the system bus that in turn determined the speed of interaction between memory and CPU. To find a solution for this imbalance, one came up with the idea to place a fast accessible memory – the cache – as near as possible to the CPU. The cache transparently saves data that comes from main memory. When later the CPU wants to reload data that was previously fetched from main memory<sup>1</sup>, the cache can handle the request. Hence, several requests to the same memory address gain a speedup of multiple orders of magnitude because the access time to the cache is several times faster than main memory accesses.

Whenever the CPU writes to a memory address, it is sufficient to update the value in the cache and to update main memory later on. This approach hides the latency of main memory accesses and increases the overall performance.

An additional advantage of caches is a lower bus contention: If parts of the data are served by the cache, the total number of accesses to main memory will decrease.

A data request handled by the cache without accessing main memory is called a *cache hit*. The other case is called a *cache miss*.

#### Types of CPU caches

Based on the kind of data saved in the cache, the following notations are used: Caches which hold instructions or data are called *Instruction Cache* or *Data Cache*. The term *Unified Cache* is used for caches that save instructions and data at the same time.

During this work the term cache will be used as a synonym for data or unified CPU caches (unless explicitly stated otherwise).

#### **Cache hierarchies**

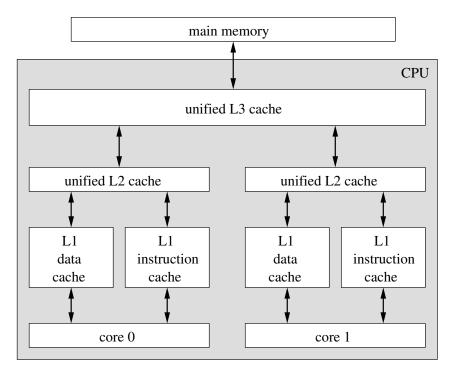

Modern computer architectures build up a hierarchy of caches. Recent systems mostly possess three different cache levels: The Level 1 (L1) cache is split into a separate instruction and data cache. Both are located like the Level 2 (L2) and the larger Level 3 (L3) or last level cache directly on the CPU die (Fig. 2.1).

If the CPU requests data that is not contained in L1 but in a higher level, the data will be moved into the lowest cache level.

Additional terminology is used in multi-core systems: A cache that is used by more than one core in the CPU is called a *shared* cache. Otherwise, it is a *private* cache.

The designer of a system with a hierarchically arranged topology of cache levels must specify whether data held in one cache level is also saved in higher levels. Such caches are called *inclusive* caches. Otherwise, the cache is called *exclusive*. As a consequence of the latter, the same data can never reside in two exclusive caches at the same time.

#### Cache lines

Caches are organized in *cache lines*. A cache line is the unit of data that is interchanged between the cache and main memory and between caches of different levels. Further-

<sup>&</sup>lt;sup>1</sup> The property that a resource referenced some time ago will be accessed again in the near future is called *temporal locality*.

Figure 2.1: Example of the cache hierarchy in recent systems.

more, a cache line is the smallest unit that can be placed in or evicted from a cache at once.

The size of a cache line differs between system architectures and can also vary in caches located at different levels of the hierarchy. A common size in recent systems is 64 bytes.

The disposition into cache lines has several benefits compared with maintaining the units in byte granularity. On the one hand, the principle of *spacial locality* is supported: If the CPU fetches some data from main memory, the load of a whole cache line will increase the probability that later read requests of data near to the first one can be satisfied by the same cache line. Hence, the performance arises. On the other hand, several flags and additional information like the corresponding address in memory are needed to keep track of every cache line and, therefore, some overhead is unavoidable. Larger cache lines reduce this overhead because the number of control information per byte decreases.

Each cache line must contain additional information about its state that describe the actuality of the saved data:

- Invalid the cache line must not be used as it is out of date

- Valid the cache line holds valid data that can be used by the CPU

- Modified the cache line holds data modified by the CPU, but the corresponding data in main memory is stale

Invalid cache lines hold no valid data and, thus, must not be used to transfer data to the CPU. After the computer is powered on all cache lines are in the invalid state. Also special CPU instructions like WBINVL on x86 mark all cache lines in the cache as invalid.

In contrast, valid cache lines hold actual data that can be used by the CPU without accessing main memory. Cache lines enter a valid state when the content was previously loaded from main memory and when both the cache and main memory contain the same data.

Modified cache lines cannot exist if the system uses a *write-through* strategy. In this case, *STORE*-instructions of the CPU save data directly in main memory, the effected cache line becomes valid.

Otherwise, STORE instructions result in modified cache lines without updating the content of main memory immediately. The content is written back when the cache line is evicted from the cache. Therefore, the strategy is also named *write-back*. The advantage is obvious: The time needed to accomplish a STORE instruction decreases and the total number of memory requests using the system bus decreases, too.

The next paragraph deals with new problems that arise when using the write-back strategy in multi-core systems.

#### Cache coherence

Caches introduce new problems in multi-processor systems as the following example shows: Two processors use a common memory but do not share any cache level. One of them reads some data from a certain memory location. After some calculation, it writes an updated value back to the same memory address. When using a write-back strategy, the new value is not placed in main memory immediately. Instead, it resides as a modified cache line in the private cache of the processor. If later the other processor reads from the memory location, it will receive an outdated value even if the access of both processors will be synchronized.

New mechanisms like *cache coherency protocols* (e.g. the *MESI* protocol) were introduced to prevent such inconsistent views on data (see e.g. [amd11, Chapter 7.3]).

#### Cache accesses

When the CPU reads some data, there has to be a procedure to detect whether the requested data is contained in one of the cache lines. However, the cache line must be found and its state must be either valid or modified to use its data. Otherwise, a cache miss occurs.

Every cache line is identified by a tag. The tag is determined by a function that takes the physical address of the requested data as an input. Usually this function extracts the n the most significant bits of the address. Depending on the kind of the cache, an index that is part of the physical address specifies a subset of all cache lines that have to be inspected in order to decide about the existence of the requested data in the cache.

If this subset is equal to the set of all cache lines, the cache will be called *fully* associative. Every cache line might contain the requested data. Depending on the size

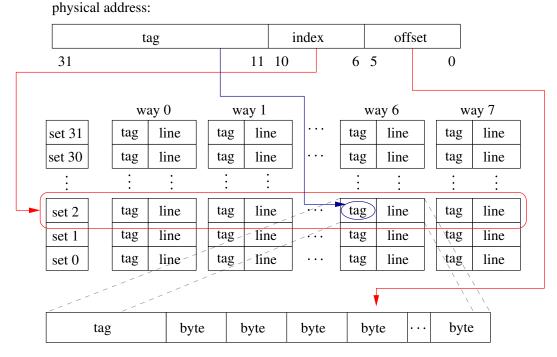

Figure 2.2: Example of an 8-way set associative cache. The index of the physical address specifies the set. If the tag of any valid or modified cache line within this set matches the tag of the physical address, the offset will determine which data to load from the cache line.

of the cache and the size of a cache line, a large number of comparisons is necessary to decide about the existence of the data in the cache. In practice, these comparisons cannot be done in parallel because the circuit would be too big, so other strategies are in use.

An n-way set associative cache has subsets containing n cache lines whose tags can be compared in parallel in order to decide whether the cache holds the requested data. Fig. 2.2 shows an example.

A direct-mapped cache has subsets containing exactly one cache line. Therefore, only one comparison is necessary to decide about the existence of the requested data.

It is easy to see that the effort to determine whether a cache line is available decreases with the number of comparisons: a fully associative cache needs as many comparisons as cache lines are in the cache, an n-way set associative cache needs n, and a direct-mapped cache needs only one comparison.

But the simplicity has its costs: The ratio between cache hits and cache misses becomes worse with decreasing associativity.

An example helps to make this clear: In a direct-mapped cache even two cache lines with the same index are problematic: The first cache line is accessed and, thus, loaded into the cache. If the other cache line is accessed afterwards, the first one will be evicted in order to make space for the second one. If the first one is then accessed again, the second cache line will be evicted and so on. The total number of available cache lines

does not matter. The example can be easily extended to an n-way set associative cache where n+1 cache lines are needed. To have the same example in a fully associative cache with a total number of m cache lines, at least m+1 cache lines are needed to achieve the same effect.

In practice the n-way set associative cache is often used as a compromise.

#### Reasons for cache misses; cache interference and cache affinity

Cache-related preemption and migration delays originate from cache misses. Therefore, this paragraph deals with the different kinds of cache misses and their corresponding reasons [BBA10a]. In addition, the terms cache interference and cache affinity are defined.

- Compulsory misses When a job starts its execution for the very first time, this kind of misses occur because there is no valid data of the job in the cache so far.

- Capacity misses Useful cache lines are evicted in order to make space for new ones. This happens if the number of accessed cache lines of a job exceeds the total number of cache lines.

- Conflict misses occur only in direct-mapped or n-way set associative caches if the mapping constraints of a cache line are not fulfilled. Therefore, useful cache lines are evicted even if not the whole cache is filled with valid or modified cache lines.

- Coherency misses occur only in multi-core systems. When a core modifies a cache line that is also contained in private caches of other cores, the cache coherency protocol has to invalidate the cache line there to prevent the usage of stale data.

The term *cache interference* describes the occurrence of frequent capacity and conflict misses in caches when multiple threads are running in parallel and the caches cannot hold the combined working set of the involved jobs.

A job incurs a bundle of compulsory misses at the beginning of its execution. During computation more and more cache lines of the working set are loaded into the cache and, thus, the overall rate of cache misses decreases over time. This property is also called *cache affinity*.

#### Cache replacement strategies

When a valid or modified cache line must be evicted in order to make space for a new one, a mechanism called *cache replacement strategy* must decide which cache line to remove.

In a direct-mapped cache the position of the new cache line is exactly specified. Therefore, the decision is obvious.

In an n-way set associative or fully associative cache the physical address of the new cache line determines the set of possible replacement candidates. The replacement strategy has to decide which cache line within this set should be chosen for replacement.

An overview about different replacement strategies and their properties can be found in [ZPL01, Chapter 2].

#### 2.1.2 Cache-related preemption and migration delay

Cache-related preemption and migration delays (CPMD) are delays caused by the use of CPU caches. The terms preemption and migration will be defined in order to specify CPMD.

#### Preemption and migration

A system is characterized by a set of tasks  $T = \{T_1, ..., T_n\}$ . Each task  $T_i$  consists of an arbitrary number of jobs. For simplicity, all jobs of a specific task  $T_i$  have a static assigned priority  $p_i$ .

A preemption occurs when job j of an arbitrary task running on core x with the priority  $p_n$  is paused by the OS scheduler in order to execute job k of another task with the higher priority  $p_m$  on core x. After l units of time job k finishes, and job j resumes on core x. Job j incurred a preemption of length l on core x.

A preemption of a job occurs when an interrupt is triggered on a core: The currently running job on that core is interrupted for a short time to handle the interrupt and the scheduler might be invoked thereafter. The scheduler either resumes the interrupted job or it selects another job for execution.

Especially on single-core systems this approach improves the system's responsiveness and achieves a more interactive system. Imagine a long running job that is not preempted by the scheduler in favor of another job with a short execution time: The system might be unusable until the first job stops its execution. By preempting the long running job periodically, it is possible to simulate the parallel execution of multiple jobs even on single-core systems.

Besides the preemption of a job, multi-core systems allow also migrations: The migration of job j is the action of disrupting the computation of j on core x to resume the computation on core y where  $x \neq y$ .

The scheduler of a system decides when to migrate a job from one core to another core, e.g., if the load of the initial core becomes too high.

Both a preemption and migration should be completely transparent for the running job. In reality, this is hard to achieve especially when resources like time are involved: If a job measures points in time periodically by the usage of a fine grained clock source, every preemption will result in a shift of the next measured point in time depending on the preemption length.

Also migrations influence the execution of jobs. The usage of fine grained time stamp counters may be problematic: A thread is going to measure the execution time of an operation. Therefore, it reads the *time stamp counter* (TSC) and starts the operation. During the execution the scheduler is invoked and the thread is migrated to another core. After the operation has finished, the thread reads TSC again to measure the length of the time interval. The result might be wrong due to the lack of synchronized clocks of the involved cores.

#### Definition of cache-related preemption and migration delay (CPMD)

In order to describe CPMD accordingly, it is necessary to introduce some more terminology.

The execution time of job j that does neither experience a preemption nor a migration during its execution is denoted as e. Let  $t_1$  be the point in time when job j starts its execution and let  $t_2$  be the point in time when job j finishes its computations. The execution time e can be defined as  $e = t_2 - t_1$ .

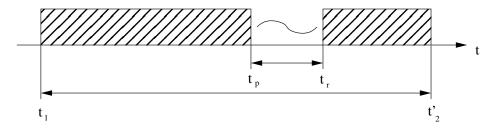

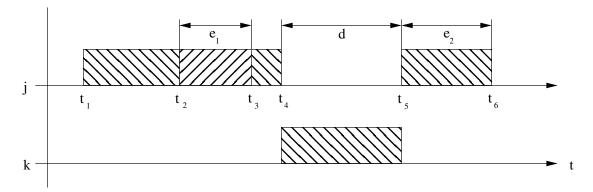

**Figure 2.3:** Job j starts to run at time  $t_1$  and is preempted at time  $t_p$  in favor of another job that runs from  $t_p$  to  $t_r$  on the same core. After it has finished, job j resumes until  $t'_2$ . The length of the interval between  $t_p$  and  $t_r$  is also called the *preemption length* of job j.

Now assume that the same job j starts its execution again at  $t_1$ , but it is preempted in favor of a higher prioritized job k at point  $t_p$  (Fig. 2.3). After k has finished its computations at time  $t_r$ , job j is resumed again until it stops at time  $t'_2$ . The execution time e' of the preempted job can be determined by calculating  $e' = (t'_2 - t_1) - (t_r - t_p)$ .

The execution time e' of a migrated job is calculated as  $e' = t'_2 - t_1$  where  $t_1$  is the start of execution and  $t'_2$  defines the end of execution.

CPMD describes the dependency between the execution time e of a continuously running job and the execution time e' of the same job that incurred a preemption or migration during its execution. The following property holds:  $e \le e'$ . The costs of CPMD can be determined by calculating CPMD = e' - e.

In case of a preemption, the increased execution time of a job is caused by a loss of cache affinity during the preemption and, thus, more cache misses when the job is resumed. Therefore, the execution time e' grows, which results in the cache-related preemption delay (CPD). Similar reasons explain the costs of the cache-related migration delay (CMD): If not all caches are shared between the involved cores, it will be necessary to transmit the cache lines of the job's working set from the private caches of the initial core to the caches of the target when these are accessed again.

If a migration takes place between cores sharing all caches, the costs of CMD will be low. Zero costs are unlikely because the overhead introduced by the implementation of the migration does also evict useful cache lines of the job's working set.

<sup>&</sup>lt;sup>2</sup> There are rare situations, in which e > e'. Further information are presented in Sec. 5.3.3.

#### 2.2 Architectures used for measurements

This section describes details of the architectures used to measure CPMD. A special focus is set on the different cache levels.

#### 2.2.1 Intel Xeon X5650 (Dell system)

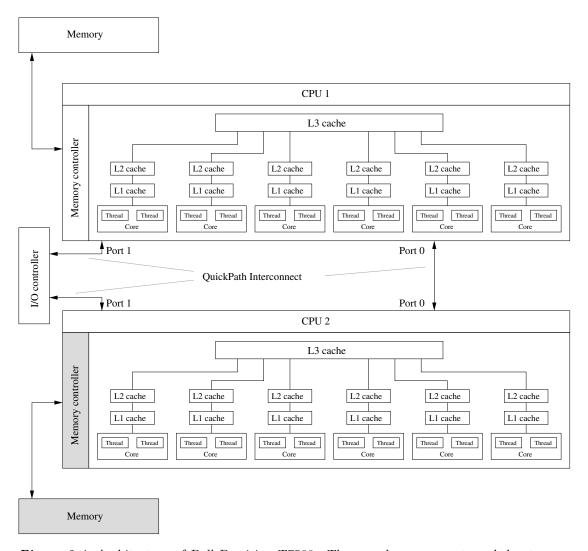

Figure 2.4: Architecture of Dell Precision T7500. The gray boxes are not used due to constraints of the NOVA operating system.

One system used to determine the costs of CPMD is the Precision T7500 produced by Dell. Fig. 2.4 gives a brief overview of the system.

#### Design of the CPU - Simultaneous Multithreading

The system contains two identical Intel Xeon X5650 CPUs comprising of 6 cores per processor. Intel adapted the technique of *Simultaneous Multithreading (SMT)* [TEL98] calling it *Intel Hyper-Threading*. If SMT is enabled, each core will behave like two independent *logical cores*. Each logical core can execute one thread that is also called *hardware thread*. If SMT is disabled, each physical core consists of only one core.

Requirements to use Intel's implementation of SMT are: a capable CPU, support by the chipset, and BIOS. The operating system should be also aware of SMT in order to optimize the allocation of threads [int11b, Chapter 2.2.8].

#### Design of the caches

Figure 2.5: Structure of physical addresses to determine cache line.

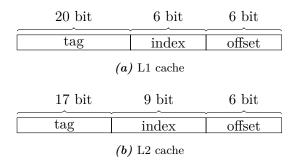

Every CPU possesses a hierarchy of three different cache levels. Each of them has a cache line size of 64 bytes. One physical core has two 32 KB L1 caches, one for instructions and one for data only. The corresponding 512 cache lines are organized as an 8-way set associative cache. Therefore, 64 sets of cache lines exist and eight comparisons are necessary to decide whether a data request can be fulfilled by the cache. The least significant 6 bits of a physical address (Fig. 2.5(a)) are used as an offset to specify the byte or word within a cache line. Bits 6 to 11 specify the set of cache lines that might contain the requested data. The most significant 20 bits describe the tag that is used as the comparison criterion to determine the existence of a cache line.

The L2 cache is also an 8-way set associative unified cache with a total size of 256 KB unique to each physical core. The number of index bits that determine the corresponding set are three bits larger in comparison to the index bits of the L1 cache. Therefore, the tag of each cache line is three bits shorter (Fig. 2.5(b)).

The L3 cache is a 16-way set associative unified cache that is shared between all cores of the CPU. The total size of 12 MB does not allow a straightforward mapping of the index bits into a specific subset: Because each cache line has a size of 64 bytes, there are 196,608 cache lines. Having an 16-way set associative cache, there must be 12,288 sets of cache lines. In contrast to the L1 and L2 cache, it is not possible to have a direct mapping of the physical addresses to the cache line set because the total number

of cache lines is no power of two and, thus, an uniformly distribution is not possible. Instead, a hash function is necessary that takes at least 14 bits as input to decide which cache set should be used. Implementation details by Intel about the hash function are not available.

Whereas L1 and L2 are exclusive caches, the L3 cache is inclusive [int11a, Chapter 2.3.4]. Therefore, data that is saved in the L1 or L2 cache is also contained in the L3 cache. Constructing L3 as an inclusive cache reduces snoop traffic between the cores on a processor that is necessary for cache coherence: If a core accesses some data that is not contained as a valid or modified cache line in L3, one can be sure that the data is also not in one of the private caches of any other core on the same CPU. It is the task of the cache coherency protocol to check whether the L3 cache of another processor holds the actual data.

#### QuickPath Interconnect

Each processor possesses two QuickPath Interconnect (QPI) [qpi09] ports. QPI was introduced by Intel in the second half of 2008. It replaces the Front Side Bus and connects processors in a distributed shared memory system. Intel advertises QPI as a high bandwidth, low latency interconnect that provides good scalability. It is a point to point connection that uses packets for information delivery. When QPI was introduced, the memory controller moved from the northbridge directly onto the processor die. Therefore, a main memory access must be distinguished between a direct and remote access. If the addressed memory is local to the processor, the access will be handled by its own memory controller. Otherwise, QPI is used to send a packet to the processor that has direct access. In the latter case the access time to main memory is higher due to the use of QPI. A cache coherency protocol preserves inconsistent memory views. Therefore, Dell's system can also be called a cache coherent non uniform memory access (ccNuma) system.

One of the QPI links connects the processor to the other one. The second port attaches each processor with the I/O controller. The ordering of the memory modules on the main board influences whether a memory access is local or remote [int11d, p. 28].

#### Memory accesses

The system has 24 GB of main memory that is uniformly distributed between both CPUs. Because the total amount of memory each CPU can access is larger than 4 GB, the usage of a 32 bit operating system that is not aware of the Physical Address Extension (PAE) results in a specific characteristic of the system: All addressable memory is connected locally to exactly one CPU and all main memory accesses on this CPU are directly handled by the memory controller on the die<sup>3</sup>. Main memory accesses of the other core always use the QPI link to access remote memory.

<sup>&</sup>lt;sup>3</sup> The Dell system can be configured in a NUMA or SMP mode. All measurements were executed in NUMA mode. In SMP mode the entire address space is split into chunks that are distributed among the memory banks. This technique improves the performance of operating systems that are not aware of the characteristics of main memory.

#### 2.2.2 Phenom 9550 (AMD system)

The AMD Phenom 9550 is a quad core processor with three cache levels. Each core possesses two identical 64 KB L1 caches, one for instructions and one for data only. L1 is a 2-way set associative cache with 512 sets. Additionally, each core has an 16-way set associative unified 512 KB L2 cache also comprising of 512 sets. All cores share a 2 MB 32-way set associative unified L3 cache. It has got 1024 different sets. In contrast to Intel's architecture, these caches are exclusive. Thus, the overall amount of data which can be saved at a time is the sum of the size of all caches.

The exclusive design of the last level cache adds additional problems: A read miss in the L3 cache produced by a core does not necessarily mean that the cache line is not in one of the private caches of another CPU. Therefore, in contrast to Intel's Xeon, the Phenom has to check if the requested data is contained in one of the private caches of another core. If the data is found there, the cache line will be transferred directly between the caches.

#### **2.3 NOVA**

$NOVA^4$  is a recursive acronym for NOVA OS Virtualization Architecture. It consists of a micro-kernel written and developed by Udo Steinberg and NUL, the NOVA userland, an unprivileged multi-server user environment providing some basic functionality. Most parts of NOVA are written in C++.

The micro-kernel is also called a micro-hypervisor because it supports recent virtualization technologies. NOVA can be used to run general applications in user mode or to host unmodified guest operating systems in *virtual machines (VMs)* by using a *virtual machine monitor (VMM)*. The aim of the micro-kernel is to design a virtualization technology with improved security. This should be achieved by reducing the trusted computing base (TCB) of the system and by lowering the communication overhead between the components running in user mode through a careful design [SK10].

The following subsections specify some important basics of NOVA that are necessary to describe the design and implementation details.

#### 2.3.1 Capabilities

NOVA handles five different types of kernel objects: protection domains, execution contexts, scheduling contexts, portals, and semaphores. If a kernel object is created, NOVA will prepare a so called capability that refers to the newly created kernel object. This capability is used like a key to gain access to the corresponding kernel object by the holder of the capability, e.g., an application. Hence, a capability is opaque and immutable to the user, so it is not possible to inspect, modify, or address the capability directly [SK10]. Capabilities are used to achieve a fine grained control mechanism to specify what a application is able and allowed to do.

<sup>4</sup> http://www.hypervisor.org/

#### 2.3.2 Protection Domains

A protection domain (PD) is a unit of protection and isolation. Like other kernel objects it is referenced by a capability. Protection domains consist of a set of capabilities to other kernel objects and platform resources like memory or I/O ports. The protection domain keeps track of the address space through capabilities to page frames [Ste11].

#### 2.3.3 Execution Contexts

An execution context (EC) is the unit of execution within NOVA and can be compared to threads in a traditional system. The EC is referenced by a capability and is permanently bound to a specific PD and CPU. The EC consists of a scheduling context that is described in the next section, a User Thread Control Block (UTCB), an event selector, CPU and FPU registers, and a reply capability register [Ste11].

One UTCB is associated with each execution context. The UTCB is used for communication and to transfer capabilities within protection domains through the usage of communication objects called portals.

Each hardware exception in NOVA has an associated positive number that is added to the event selector to get a capability selector. To handle a specific exception, a capability to a portal with the corresponding index has to be created and bound to a user-defined function. Thus, an exception results in a call to the specified function handler.

#### 2.3.4 Scheduling Contexts

A scheduling context (SC) is a unit of dispatching and prioritization [Ste11]. It is permanently bound at any point in time to exactly one EC and, therefore, to exactly one CPU. To start the execution of an EC, a SC must be created and assigned to the EC. In order to create such a SC a priority and time quantum must be defined. The priority has to be in the range from 0 to 255, where 255 is the highest available priority. The time quantum defines the time of execution before the scheduler of the system is invoked to select the next SC.

The NOVA scheduler handles different priority queues per CPU. Whenever the time quantum of the SC of a running EC exceeds, the EC is stopped and the time quantum of the SC is replenished. Additionally, the SC is enqueued to the end of its associated priority queue. The scheduler determines the queue with the highest priority that contains a SC whose associated EC is ready to run. The SC waiting to run for the longest time is taken from the queue by the scheduler. Consequently, scheduling decisions within a priority queue are chosen round robin.

#### 2.3.5 Portals

Portals are used as communication end points in NOVA. They are also used to define exception handlers as described in 2.3.3.

#### 2.3.6 Semaphores

A semaphore (SM) is a mechanism to synchronize the execution of ECs. A semaphore uses an internal counter that is initialized with a user-defined value during creation. The semaphore provides two operations: down and up.

When calling the down-operation through the capability referencing the SM, the internal counter of the SM is inspected. If it is larger than zero, the counter will be decremented by one, and the execution will proceed. Otherwise, the EC blocks on the semaphore.

If the up-operation of a semaphore is called and there are blocked ECs waiting for the semaphore, one of them will be unblocked in order to resume its operation. If there are no blocked ECs waiting for the SM, the internal counter of the SM will be incremented by one.

#### 2.3.7 Threads

There is no thread kernel object available in NOVA. In fact, a thread as known from other operating systems can be seen as the compound of a SC and EC. However, a SC is permanently bound to a specific EC that is in turn permanently bound to a specific CPU. Consequently, by using the term thread in this context, it is not possible to migrate a thread between cores since the composition of SC and EC, and EC and CPU is permanently fixed.

A migration of a thread to another core in this context mean that the execution of an EC is interrupted and its internal state is transferred into another EC on the target CPU. A SC has to be assigned to the target EC to keep the execution of the job ongoing. It might also be possible to change the priority of a computation during the migration because the priority of both involved SCs might be different. However, in this work the priorities of the involved SCs stays always the same and does never chance during execution.

#### 2.4 Miscellaneous

#### 2.4.1 System Management Mode

System Management Mode (SMM) is an operational state of recent processors. It is enabled by activating a particular CPU pin or by a special interrupt caused by the advanced programmable interrupt controller (APIC). SMM is used as a transparent mechanism to interrupt the currently running task on the CPU to perform platform specific functions like power management and system security (see e.g. [int11b]).

From the perspective of the operating system SMM results in jumps of the internal clocks that cannot be avoided easily. If measurements in a system are accomplished, SMM will lead to imprecise results.

A tool called *hwlatdetect* is available on Linux that can be used to determine the influence of SMM. The Dell system was traced for 5 minutes, but no occurrence of SMM

was measurable<sup>5</sup>. Therefore, SMM should not influence the measurements on the Dell system.

#### 2.4.2 Time stamp counter

Beginning with the Pentium, Intel introduces a 64 bit *time stamp counter (TSC)* that is reset to zero on power on. The value of the counter is incremented with every processor cycle and allows applications to measure the time at a fine grained granularity. The duration of arbitrary operations can be estimated by reading TSC before and after the operation and by calculating the difference between the two values. The result divided by the clock rate of the CPU determines the period of time.

Caution is recommended in multi-core systems because the counters of the cores need not to be synchronized perfectly. In addition, power saving technologies that throttle the CPU speed can result in wrong values because the values of the counters are incremented with a constant rate.

TSC is used to determine all periods of time within this work, but it is never used to measure any duration in which a migration might occur.

#### 2.5 Related Work

Bastoni et al. already analyzed the influence of CPMD in relation to scheduling decisions [BBA10a]. The costs of preemptions and migrations under different scenarios were evaluated and resulted in five different observations:

- 1. The predictability of CPMD depends heavily on the size of the different cache levels.

- 2. There are no substantial differences between the costs of a preemption and the costs of a migration in a loaded system.

- 3. Preemptions cause always less delay than migrations in an idle system. The costs of L3 and memory migrations are comparable.

- 4. The costs of CPMD are strongly related to the preemption length unless cache affinity is completely.

- 5. The number of tasks in a system does not significantly influence CPMD.

The measurement system used in [BBA10a] comprised of four Intel Xeon L7455 processors each one with six cores and uniform memory access (UMA). All cores on a processor share an unified 12 MB L3 cache. Groups of two cores share an 3 MB L2 cache, every core possesses an 32 KB L1 data cache and an identical instruction cache.

$<sup>^5</sup>$  A threshold that is used as an indicator for long interrupts for example caused by SMM can be passed as an argument to hwlatdetect. Even the lowest possible number of 1  $\mu s$  was unable to find these interrupts caused by SMM

# 3 Design

The first section of this chapter presents two different methods to measure the costs of CPMD and discusses their advantages and disadvantages.

The second section describes the design of a working set that is usable to determine the costs of CPMD. Two different approaches to simulate background loads are discussed in the third section.

At the end of this chapter a detailed characterization of the experiments that were carried out and evaluated later on is presented.

#### 3.1 Measurement of CPMD

In section 2.1.2 the sources of CPMD in recent systems were discussed. In order to determine realistic costs of it, a reliable mechanism to detect and to measure the influences of CPMD has to be designed. This section describes how an application can act to achieve this goal.

Figure 3.1: Plan of execution to measure the influence of CPMD.

A job j repeatedly accessing its working set is released in a system at time  $t_1$  and is chosen by the scheduler to execute (Fig. 3.1). At the beginning, the job incurs compulsory cache misses. At  $t_2$  the job accessed its working set for the first time and most parts of it are loaded into the cache. Between  $t_2$  and  $t_3$  the job accesses its working set for the second time. At  $t_4$  the scheduler is invoked and preempts job j that currently accesses its working set for a third time. It might be that job j exhausted its time quantum or that the priority of another job k is higher than j's priority. When job j is rescheduled again at  $t_5$ , the cache is now loaded with the working set of job k. Parts of j's working set are no longer available in the cache and must be reloaded from

main memory, resulting in a larger total execution time. At  $t_6$  job j finishes its execution after accessing its working set for three times.

According to [BBA10a], it is possible to determine the cache-related preemption and migration delay in two different ways.

Let us assume that a job has neither a possibility to trigger a preemption nor a migration on demand, but it can detect whether it experienced one of these events. In recent systems this is normally not the case because a preemption or migration is done by the system transparently. A job j can run as described before from  $t_1$  to  $t_3$  (Fig. 3.1). After accessing its working set for two times, the job checks whether it experienced a preemption or migration. If so, it has to start again from the beginning by measuring  $t_1$ .

Otherwise, one can calculate the time necessary to access the working set by subtracting  $t_2$  from  $t_3$ . This period of time presents the *cache warm* access time to the working set. After  $t_3$  the job waits to be preempted or migrated in order to continue. While waiting, the job randomly accesses parts of its working set to achieve cache affinity. After detecting a preemption or migration, the job record  $t_5$  and accesses its whole working set again. Thereafter, the measured point in time  $t_6$  allows to calculate the time necessary to access the working set after a preemption or migration by subtracting  $t_5$  from  $t_6$ . Again, the job must be aware of a preemption and migration between  $t_5$  and  $t_6$ . If it experiences such an event, it will have to start from the beginning by measuring  $t_1$  again.

The delay d caused by the preemption or migration can now be determined by calculating:  $d = (t_6 - t_5) - (t_3 - t_2) = e_2 - e_1$ .

This method is called *schedule-sensitive* [BBA10a]. It has one major drawback: A long time is needed to get a large number of valid samples because a preemption or migration is neither allowed between  $t_1$  and  $t_3$  nor between  $t_5$  and  $t_6$ . The occurrence of such an event cannot be influenced by the job and depends on the utilization of the system. Furthermore, the time necessary to wait for a preemption or migration after  $t_3$  might be quite long in case of a system with a low utilization.

The second approach to measure CPMD is called *synthetic method* [BBA10a]. It requires the possibility to let an application decide by itself when it will be preempted or migrated. If a preemption or migration is only accomplished on explicit requests, there will be no need to check for it during runtime. According to Fig. 3.1, the job starts its execution at  $t_1$  and measures  $t_2$  and  $t_3$  as described before. Thereafter, it asks some service for a preemption or migration. When the job starts again either after a preemption or on another core after a migration,  $t_5$  and  $t_6$  are determined. The delay d can be calculated as shown before.

The explicit request of a preemption or migration used by the synthetic method allows to get one valid sample on each round. However, this methodology has two drawbacks: It is not possible to examine dependencies between scheduling decisions and CPMD, and it is not possible to measure the influence of the total number of tasks in the system on CPMD[BBA10a, Chap. 3.2].

NOVA has no built-in support to inform a thread about a preemption during execution, but the schedule-sensitive method requires such a mechanism to work. Therefore, changes in the kernel would be indispensable. Furthermore, we are interested in as many

valid samples of CPMD as possible, so the schedule-sensitive method might not be a good choice.

The synthetic method allows to collect a huge number of valid CPMD samples within a short period of time. In addition, the preemption length can be freely chosen by the application. This property might be very useful in order to study the influences on CPMD.

After weighing the advantages and disadvantages, one has to conclude that the synthetic method is the better choice for the purpose of this work. Nevertheless, the question arises whether the synthetic method can be implemented in NOVA efficiently and with less effort.

NOVA is designed as a micro-kernel and implements only a few primitives in the kernel as described in Sec. 2.3. The design does not provide a mechanism to enable migrations out of the box. Anyway, it is possible to implement thread migrations in the user land by using ECs and SCs in combination with event handlers and semaphores. In this way, it is possible for a thread to trigger a migration of itself to a specified core. More information about the implementation of the migration functionality is provided in Sec. 4.1.

An application is able to trigger a preemption for a specified time by using a timer functionality provided by a service of the NOVA userland (NUL). Thereby it is possible to block the execution for a specified time and to resume it thereafter. During blocking other threads are scheduled.

Let us recall Fig. 3.1 in combination with the synthetic method and NOVA: An application starts its execution at  $t_1$ . It accesses its working set for the first time to bring it into the cache and measures the time needed to access its working set again. Some properties of the application's SC have to enforce that there is neither a preemption nor migration up to  $t_3$ . Otherwise, conclusions about  $e_1$  might be wrong. Since a migration does only occur on explicit request by the job, it will not happen unexpected.

In contrast, a preemption is handled by the scheduler of NOVA and must be prevented: On the one hand, the time quantum of the SC could be chosen sufficiently long to prepare the SC with enough computation time. On the other hand, the priority of the scheduling context can be specified cleverly as follows: If all other SCs in the system that are combined with user defined ECs have a lower priority, they will not be scheduled because the time quantum of the measurement thread will be replenished directly after it runs out of time. The second approach is more convenient because determining the length of the time quantum is hard.

If the measurement thread has determined the time needed to access its cache warm working set after  $t_3$ , it will preempt itself for a specified period of time l. The thread blocks thereby on a semaphore and the scheduler chooses any other ready thread to run. If there is no such thread available, the system will keep idle. Otherwise, a special-purpose thread is scheduled that has by construction a lower priority than the measurement thread.

This design allows the usage of lower prioritized threads for creating arbitrary simulated background loads to detect the costs of CPMD. Threads running as background load access different working set sizes and load their data into the cache systematically.

From the perspective of the measurement thread these threads pollute the cache lines. Therefore, they will be called *cache polluter threads* or simply *cache polluters*.

After l time units the measurement thread is ready to run again. However, l is used as a parameter to control the time the cache polluter threads are able to work. The influence of a preemption or migration can now be determined as described before.

In single-core systems  $e_1$  is determined without the influence of other threads running in parallel, because at any point in time only one thread can be executed in the system. Hence, multiple measurements of  $e_1$  result in similar values.

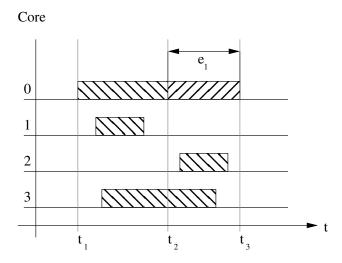

**Figure 3.2:** Measurement problems of  $e_1$  in multi-core systems.

In multi-core systems this cannot be guaranteed because other threads are running on other cores in parallel. Fig. 3.2 shows an example where the cache is shared between all cores. The measurement thread on core 0 accesses its working set between  $t_1$  and  $t_2$  to bring it into the cache. Another thread on core 1 does its calculation in parallel and, thus, loading its own working set also into the cache. It cannot be guaranteed that parts of the working set of the measurement thread does not get lost because of cache interference. The same holds for the thread on core 3.

The measurement of  $e_1$  might also be influenced by the thread on core 2: Data that will be accessed by the measurement thread could be evicted from the cache through loads by the other thread beforehand.

Therefore, it is necessary to remeasure  $e_1$  whenever the background load is changed. Otherwise, the costs of CPMD would not be well defined due to  $e_1$ 's missing relationship to the background load.

# 3.2 Data structures and access patterns of the measurement thread

In order to find the dependency of different factors on CPMD, the working set accessed by the measurement thread has to be defined. The goal of this section is to design a proper data structure that can be used to construct this working set. It must be sensible to CPMD on the one side, and its properties must be easily adaptable to study the influences of CPMD on the other side.

In fact, desired properties of the data structure are:

- 1. Simple design

- 2. Dynamic in size

- 3. Low utilization of the CPU besides memory accesses

- 4. Enforcement of sequential accesses

- 5. Sensitive to CPMD

- 6. Possibility to modify data

A linked list is a common data structure that fulfills all of these properties: It is simple in design and easily extendable in size by increasing the number of list elements dynamically. This property is needed to study the influence of CPMD on the working set size. Furthermore, the elements of the list are sequentially accessible without complex calculations, so the CPU only waits most of the time to receive data from the caches or main memory. This property enables to measure additional characteristics like the cache and main memory access times.

Enforcing a sequential access by design prevents the compiler from optimizing the code in an undesired way. Otherwise, it would be hard to study the influencing factors of CPMD. If a list element contains a pointer to the next list element, as it is the case in a linked list, it will not be possible to get the address of the next list element without accessing the previous one beforehand.

Additionally, the list structure can be made as much sensitive to CPMD as possible by a proper design of the list elements. Such a design allows afterwards conclusions about the worst case costs.

The possibility to modify data is important to study the costs of CPMD in case of modified cache lines. This property is achievable by extending the list elements by a writable data element.

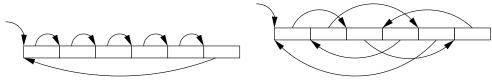

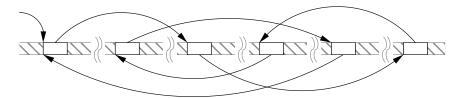

Fig. 3.3(a) shows a possible design of the structure. However, it has one major drawback: The hardware prefetcher of a system can load data from main memory before the data is really needed because the distance of two consecutive reads is always constant, except if the last pointer to the first element is reached. Therefore, this structure is not sufficient to measure realistic access times to the different cache levels and main memory.

Shuffling the list elements as shown in Fig. 3.3(b) prevents the hardware prefetcher to work because the distance of two consecutive reads is no longer constant. Therefore, realistic access times to the caches and main memory are measurable.

An additional improvement is to align the list elements to cache line boundaries (Fig. 3.3(c)). Recall that data between the caches, and between the last level cache and

- (a) List elements are placed contiguously in the memory chunk.

- (b) List elements are shuffled in the memory chunk.

(c) List elements are shuffled and aligned within a cache line.

Figure 3.3: Linked list as a data access structure.

main memory is changed cache line wise. Thus, placing only one list element within a cache line leads to a maximum sensitivity to CPMD.

The constructed list structure of Fig. 3.3(c) has got all needed properties and is used in the experiments to simulate the working set of the measurement thread.

The used phrase "access the working set" means in case of a linked list that starting at an arbitrary list element all other list elements are accessed step by step until the initial one is reached again. Depending on the number of list elements, at least parts of working set are loaded into the cache.

## 3.3 Background load

The goal of this section is to describe the necessity of a well defined background load to study the influences of CPMD in loaded systems. Furthermore, two different approaches to create background load are introduced.

The term background load is defined as the set of all user threads in the system excluding the measurement thread. In this sense, for example the former defined cache polluter threads are elements of the background load.

The background load is necessary to achieve effects of cache interference between the measurement thread and threads of the background load. If there is none of the latter one, the cache will not be polluted when the measurement thread is preempted. Accordingly, the working set of the measurement thread resides in the cache and CPD will be around zero<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup> In practice the costs of CPD might be also available in an idle system because the scheduler of the system is invoked and it might also change some contents of the cache during its execution. Furthermore, interrupts handled by the operating system can occur, possibly evicting useful cache lines.

A lack of background load will not remove the costs of CMD if modified cache lines are in one of the private caches of the initial core: The cache lines have to be transferred to the target core and, thus, the costs of a migration are not zero.

If a thread does not modify the memory, CMD can be zero because the working set of the thread might be already contained in the private cache of the target core due to a previous execution, but this is unlikely.

A typical system comprises of more than one running thread. Hence, from the perspective of a single thread there is always background load existent and, thus, CPMD is always present. Therefore, in order to use the measurement thread to detect CPMD a background load has to be modeled.

Two approaches to create usable background load are introduced in the next subsections.

#### 3.3.1 Constructed background load

User defined threads only responsible for polluting the cache are called *constructed* background load. These threads have several benefits:

- no constraints in reference to the used working set

- reproducible results

If there are no constraints concerning the working set and its access, arbitrary background loads can be created and, thus, the pollution of the caches can be controlled at a fine-grained level.

Another advantage is the reproducibility of measurements: Experiments can be repeated under the same settings arbitrarily and, thus, the influence of different system properties can be studied.

The major drawback of a constructed background load and its associated access to the working set is that the background load is not realistic: A regular application executes instructions to solve a specific problem. Therefore, the access to the working set varies highly with the type of an application and it might be the case, that not all factors influencing CPMD are detectable with the constructed background load.

To reduce the implementation effort, the measurement thread's data structure of a shuffled linked list (Fig. 3.3(c)) is reused for the constructed background load. Hence, the size of the working set and the rate used to modify cache lines can be easily controlled. The cache polluters can be started and stopped on demand on arbitrary cores in the system.

#### 3.3.2 Realistic background load

To study the influence of a more realistic background load the functionality of NOVA and the services provided by NUL are used to setup virtual machines (VMs). Each VM is started before the measurement and runs permanently on exactly one core. The VMs compile the Linux kernel in an endless loop. The compilation of the kernel needs a great amount of computing power and has a permanently changing working set. Because the

needed source files of the Linux kernel came from a disk, interrupts occur frequently making the background load even more realistic. The number of VMs running in parallel can be changed during startup to observe the influences on CPMD.

#### 3.4 Experimental design

This section provides an overview about the experiments that were carried out to detect the costs of CPMD.

#### 3.4.1 Memory access times

The goal of this experiment is to determine the access times to the different cache hierarchies and main memory in an otherwise idle system. The experiments also show the penalties of accessing remote memory through QPI in the Dell system.

The measurement uses the list structure defined in Sec. 3.2. The experiment is run under three different circumstances depending on the state of the cache lines *before* the measurement is started:

- 1. valid cache lines

- 2. invalid cache lines

- 3. modified cache lines

All three experiments are carried out using different working set sizes.

The first experiment enables to determine the access time to the different cache levels. The working set – or at least parts of it – are loaded into the cache before the measurement is started. Thereafter, the access times to the cache or main memory are measurable by accessing the working set. If its size grows above the size of a cache level, the cache cannot hold all the needed data and, thus, the access time will increase because the next cache level or main memory has to handle the request. This experiment allows to determine the *cache warm* access times that are near the best case possible.

The cache cold access times are studied with the other remaining experiments: If the cache contains only invalid cache lines (second experiment) beforehand, each list element has to be fetched from main memory to get the address of the next list element. Thus, this setup measures main memory access times. The worst case access times of an otherwise idle system will be determined, if the cache contains only modified cache lines (third experiment) before the working set is accessed: In order to load the working set, modified cache lines must be evicted.

#### 3.4.2 Accuracy of preemption length

As described in Sec. 3.1 the length of a preemption is controlled by a timer service implemented in NUL. The accuracy of the length of a preemption has to be verified, otherwise no statements about CPMD in relation to the preemption length are possible.

In an otherwise idle system a thread measures the point in time  $t_1$  before it is preempted for a period of time l. Immediately after the preemption the point in time  $t_2$  is measured. The period  $t_2 - t_1$  and l should be approximately equal.

The results of the experiment in an idle system will be the same in a loaded system if all user threads are running with a lower priority than the SC of the EC that is responsible for handling the timer interrupt and the priority of the measurement thread. That is the case in the used design.

#### 3.4.3 Preemption

The costs of a preemption are determined with this experiment. The measurement thread is permanently bound with exactly one cache polluter to a single core. The following parameters are changed to study the costs of a preemption:

- working set size of measurement thread

- preemption length d

Changing the working set of the measurement thread allows to determine its sensitivity to CPD. Additionally, different preemption lengths influence the time the cache polluter thread is able to run, so the relation of the preemption length and CPD can be studied.

Furthermore, the experiment is repeated using the realistic background load instead of the constructed one. Additionally, CPD is studied in a heavily loaded system where each core runs a VM.

#### 3.4.4 Migration

Different kinds of migrations are explored within this experiment on the Dell and Phenom system to gain knowledge about CMD: between cores sharing a cache level, and between cores with no caches in common<sup>2</sup>. Thereby, the measurement thread is periodically migrated between the involved cores determining the necessary time to access its working set after each migration.

The experiment is repeated using different system states: idle, loaded with constructed background load, loaded with realistic background load.

The working set size of the measurement thread is varied to study its influence on CMD.

$<sup>^2</sup>$  The Phenom system does only allow migrations between cores that share the L3 cache due to the limitation of one physical processor.

# 4 Implementation

This chapter describes important implementation details. The first section gives an overview about the implementation of a thread migration. The second section covers the collection of statistical data, followed by details about the mechanisms that were used to control the polluter threads.

The last section is about the implementation of an additional system call in the kernel that is needed by one of the experiments.

## 4.1 Migration

NOVA contains no possibility to create a thread like object that can be migrated directly between different cores of a system. Therefore, such a mechanism has to be implemented.

To explain the details, this section is divided into two additional subsections: The first one discusses the necessary setup, the second one shows what happens during runtime when migrating a thread.

#### 4.1.1 Setup phase

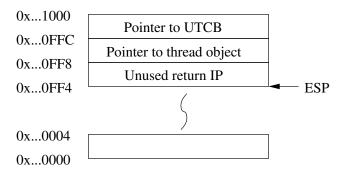

To achieve the ability to migrate a thread between different cores of the system, an EC for the thread has to be created on every core that should be able to execute it afterwards. To limit the overhead of a migration, it is necessary to share as much resources as possible per EC (e.g. stack).

Additionally, two portals for exception handling are created per EC. The *startup* exception handler is called the first time when an EC starts its execution. It sets up the instruction pointer properly to ensure that the EC begins at the correct instruction after the handler returns. The other handler is called recall exception handler. It is invoked when the recall system-call is used.

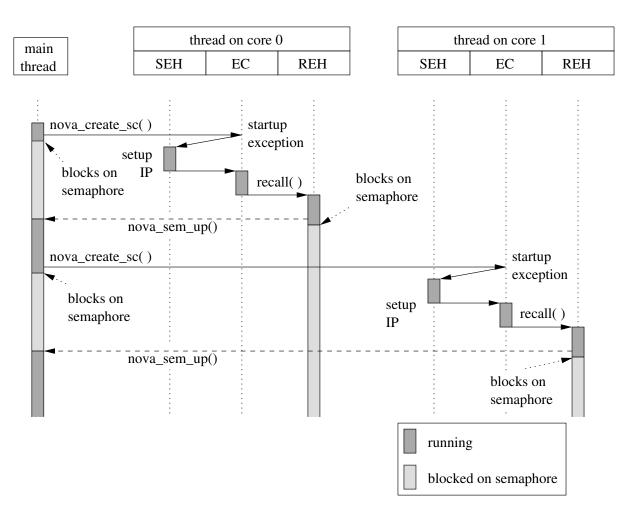

Fig. 4.1 shows an exemplary setup of a thread that should be migratable between core 0 and core 1 afterwards. The main thread creates an EC with the associated handlers on the first core. Additionally, a SC is created and bound to the EC by the main thread that blocks on a semaphore, waiting for the setup of the EC to complete.

The newly created SC is scheduled eventually and produces a startup exception because it does not know which instruction to execute yet. Therefore, the startup exception handler is called and sets up the instruction pointer properly. After it returns, the EC starts its execution and uses the recall system-call to trap into the kernel, ending up with the invocation of the recall exception handler. Its implementation ensures that the main thread is unblocked again, so it can proceed to setup ECs on other cores as well. The handler itself blocks on a semaphore used to control its execution because

Figure 4.1: Setup of a migratable thread. On each core there is the startup exception handler (SEH), the execution context (EC), and the recall exception handler (REH).

there is no other work to do yet. The corresponding EC will not be rescheduled before its execution handler returns.

After the last handler wakes up the main thread again, the following situation occurs: The main thread is ready to run and every created EC is blocked on a dedicated semaphore in its associated recall handler.

It would be possible to avoid the sequential setup if every EC uses its own stack at least during the setup phase. This stack can be small in size just to handle the execution of the recall system-call. Nevertheless, the parallel setup is not used because the overall speedup is insignificant due to its one-time initialization at the beginning.

#### 4.1.2 Migrations during execution time

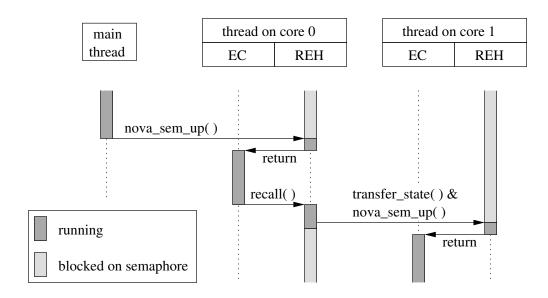

Figure 4.2: Example of a migration from core 0 to core 1. The recall exception handler implements the actual migration. It copies the necessary registers between the involved UTCBs.

Fig. 4.2 shows an exemplary execution of the formerly set up thread. The main thread starts one of the ECs by calling the up-operation on the semaphore that blocks the recall exception handler on the target core. Thus, it continues with its execution and jumps into the kernel after its return. Depending on the definition of the handler, parts of its UTCB are copied into the CPU registers before the EC proceeds running.

Let us recall the last executed function of all ECs: They executed the recall systemcall to trigger an exception and entered the recall exception handler. Only one EC continues with the next instructions now; the other ECs stay blocked.

At some point in time the running thread triggers a migration. This is done by writing the id of the target core into the *EBX*-register and by calling the recall function, which enters the recall handler. It determines the target core of the migration by reading its UTCB that contains the value of EBX. Now the recall exception handler transfers the content of its own UTCB, which refers to the state of the interrupted EC, into the

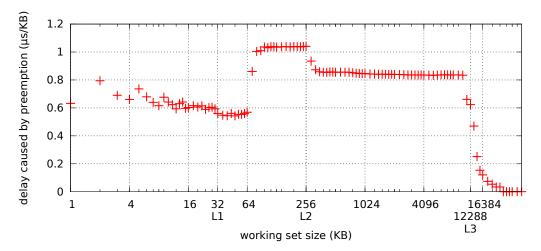

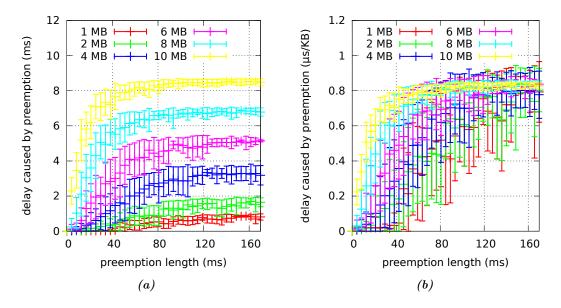

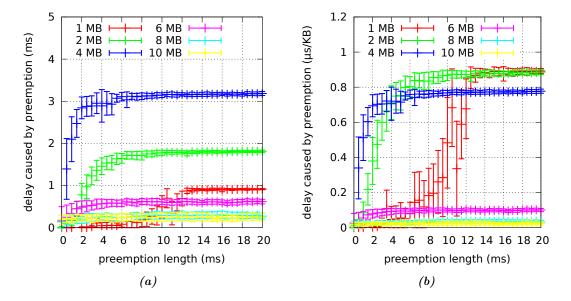

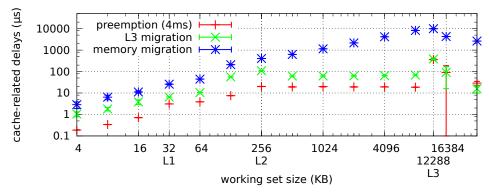

UTCB of the exception handler on the target core. Thereafter, the EC is unblocked. The handler of the origin EC blocks on its own semaphore, waiting for a future release.