# Verification of the Fiasco IPC Implementation

by Endrawaty

Thesis Report

International Master Program

Computational Logic

March 2005

Institute of Theoretical Computer Science

Department of Computer Science

Dresden University of Technology - Germany

Overseeing Professor : Prof. Dr.-Ing. habil. Horst Reichel Supervisor: Dr. Hendrik Tews Master Thesis Assignment (Computational Logic)

Student: Endrawaty Endrawaty Matr. No. 2982167

# Verification of the Fiasco IPC implementation

**Context** The microkernel Fiasco is an implementation of the L4 interface in C++. It is used in the context of the DROPS-project. One of the services that is provided is inter-process communication (IPC). In Fiasco IPC is the only means to send data from one process to an other one. Fiasco's IPC is special in the sense that

- the kernel is peemptible almost everwhere (so an ongoing IPC might be preempted by some other activity)

- the IPC is stateless, that is the data send is not cached in the kernel, it is copied directly from the sender to the receiver (so the kernel must suspend one IPC partner until the other one is ready)

**Assignment** The aim of this master thesis is to develop and verify an abstraction of Fiascos IPC implementation. The abstraction should have the form of a finite state automaton, where one automaton models one process that is engaged in an IPC. For the verification several such automaton are set in parallel. Properties of interest for the verification are dead lock, live lock, safty properties (of availability) or liveness properties (message delivery).

The student can choose his preferred formalism for the IPC model. All of CCS, CSP,  $\pi$ -calculus, or promela are possible. The properties should be formulated in a suitable modal logic. They should be verified with a suitable proof assistent or model checker.

overseeing Professor: Prof. Horst Reichel

Advisor: Dr. Hendrik Tews

Begin: October 1st 2004

**Due date:** April 1st 2005

Dresden, October 29th 2004

# Statement of Academical Honesty

Hereby, I declare that the work of this master's thesis is completely the result of my own work, except where otherwise indicated. All the resources I used for this master's thesis are given in the list of references.

Date: March 16th, 2005

Signature:

# Acknowledgements

I would like to express my gratitude to the following people below, who has helped me in numerous kinds of way, during the work of my master's thesis:

- Hendrik Tews: for all his support and guidance during the time I worked on my thesis. I learned a lot of new important knowledge from him, ranging from technical stuff until various strategies in tackling big and delicate problems. This master's thesis has been a wonderful experience for me thanks to him.

- Michael Hohmuth: for his time and patience in answering my questions about Fiasco IPC.

- Gerard J. Holzmann: for his insightful guidance on Promela and SPIN.

- Ari Saptawijaya: for proof-reading my thesis report.

- Ren Jie Yun: for being a kind dorm-mate. She often prepared meals for me voluntarily, because she knew I was pretty much occupied with my thesis.

- Andi Wijaya Tan: for being my pillar and my shelter. His love and encouragement

has been my source of inspiration in completing my master study in these two and

a half years.

- My parents, sisters, and brother: for always believing in me.

I could pursue this master study thanks to the financial support that I have received from the International Quality of Network scholarship, for one year and 5 months (Oct 02 - Feb 04). Without this scholarship, I would not be able to come to and study in Dresden. I am grateful to get this chance to study in Computational Logic, which to me personally is a very challenging subject to stimulate a new way of thinking. Therefore, I owe my thanks to the people who have established Computational Logic program and who have given me the scholarship.

# Abstract

Fiasco is a microkernel which is developed in the context of DROPS (Dresden Real-Time Operating Systems)-project. One of Fiasco's system calls is IPC (Inter-Process Communication). In this master's thesis, a model for Fiasco IPC has been built. The real Fiasco IPC code which was written in C++ has been reverse-engineered into a model in Promela. After the model was built, some properties were proposed and verified using SPIN. Those properties are safety properties (freedom of deadlock, some "bad" things that should never happen) and liveness properties (freedom of certain bad cycle, some "good" things eventually happen).

X CONTENTS

# ${\bf Contents}$

| 1  | Intr               | oducti  | ion                                    | 1  |  |  |  |  |  |  |  |

|----|--------------------|---------|----------------------------------------|----|--|--|--|--|--|--|--|

| 2  | Fias               | sco IPO | C                                      | 2  |  |  |  |  |  |  |  |

|    | 2.1                | L4 and  | d Fiasco                               | 2  |  |  |  |  |  |  |  |

|    | 2.2                | How II  | PC Works                               | 3  |  |  |  |  |  |  |  |

|    |                    | 2.2.1   | IPC States                             | 3  |  |  |  |  |  |  |  |

|    |                    | 2.2.2   | IPC Phases                             | 4  |  |  |  |  |  |  |  |

| 3  | Pro                | mela    |                                        | 6  |  |  |  |  |  |  |  |

|    | 3.1                | Prome   | ela vs Programming Languages           | 6  |  |  |  |  |  |  |  |

|    | 3.2                |         | Types and Data Objects                 |    |  |  |  |  |  |  |  |

|    | 3.3                | Proces  | SSES                                   | 8  |  |  |  |  |  |  |  |

|    | 3.4                | Meta    | Terms and Basic Statements             | 9  |  |  |  |  |  |  |  |

|    |                    | 3.4.1   | Inline                                 | 10 |  |  |  |  |  |  |  |

|    | 3.5                | Compo   | ound Statements                        | 10 |  |  |  |  |  |  |  |

|    |                    | 3.5.1   | Atomic Sequences                       |    |  |  |  |  |  |  |  |

|    |                    | 3.5.2   | Selection Construct                    | 11 |  |  |  |  |  |  |  |

|    |                    | 3.5.3   | Repetition Construct                   | 12 |  |  |  |  |  |  |  |

| 4  | Modeling Design 13 |         |                                        |    |  |  |  |  |  |  |  |

|    | 4.1                |         | al Modeling Conventions                | 13 |  |  |  |  |  |  |  |

|    | 4.2                |         | d in Promela                           |    |  |  |  |  |  |  |  |

|    | 4.3                | Global  | l Variables                            | 14 |  |  |  |  |  |  |  |

|    | 4.4                | The In  | nlines                                 | 16 |  |  |  |  |  |  |  |

| 5  | SPI                | N Sim   | ulation and Verification               | 18 |  |  |  |  |  |  |  |

| •  | 5.1                |         | ation                                  |    |  |  |  |  |  |  |  |

|    | 5.2                |         | ctness Property                        |    |  |  |  |  |  |  |  |

|    | 5.3                |         | ating The Verifier                     |    |  |  |  |  |  |  |  |

|    | 5.4                |         | iling The Verifier                     |    |  |  |  |  |  |  |  |

|    | 5.5                | •       | ng The Verifier                        |    |  |  |  |  |  |  |  |

|    |                    | 5.5.1   | Setting the Number of Reachable States |    |  |  |  |  |  |  |  |

|    |                    | 5.5.2   | Setting the Search Depth               |    |  |  |  |  |  |  |  |

|    |                    | 5.5.3   | Other Run-Time Options                 |    |  |  |  |  |  |  |  |

|    | 5.6                |         | s Verification Attempts                |    |  |  |  |  |  |  |  |

|    | 0.0                | 5.6.1   | SPIN Version and Hardware Used         |    |  |  |  |  |  |  |  |

|    |                    | 5.6.2   | Default Verification                   |    |  |  |  |  |  |  |  |

|    |                    | 5.6.3   | Verification of Proposed Properties    |    |  |  |  |  |  |  |  |

| 6  | Con                | chisio  | ns and Future Work                     | 31 |  |  |  |  |  |  |  |

| •  | 6.1                |         |                                        |    |  |  |  |  |  |  |  |

|    | 6.2                |         | e Works                                |    |  |  |  |  |  |  |  |

| Re | efere              | nces    |                                        | 33 |  |  |  |  |  |  |  |

| CONTENTS | xi |

|----------|----|

| ONTENTS  | X1 |

A Fiasco IPC Model in Promela

**35**

# 1 Introduction

Software systems may range from simple to complex ones. The more complex a system, the bigger possibilities it might have errors. Some errors can be so subtle that they are usually unseen at the initial testing phase. Meanwhile, the ultimate goal of software engineering is to deliver a system which is bugs-free and provably correct. But most situations show that software development spends most of its time in fixing the errors.

Two significant aspects of systems which contribute to their complexity are concurrency and nondeterminism. Concurrent and nondeterministic systems produce a large number of possible executions. When they contain errors, testing method would not be a wise solution to trace the sources of errors. It will be hard to have a testing method that could provide a complete coverage for all possible errors of complex systems. A famous quote from Dijkstra applies in this case: "Program testing can be used to show the presence of bugs, but never to show their absence." The two main problems in testing such distributed systems are [1]:

- 1. limited controllability of events in distributed systems executions and

- 2. limited observability of those events.

In order to prove the correctness of distributed systems, we can turn to the so-called formal methods. Taken from http://www.fmeurope.org/, formal methods are defined as mathematical approaches to software and system development which support the rigorous specification, design and verification of computer systems. Two well-established approaches to formal verification of hardware and software systems are theorem proving and model checking.

Theorem proving is a technique where both the system and its desired properties are expressed as formulae in some mathematical logic [11]. This mathematical logic defines a set of axioms and a set of inference rules. Strictly speaking, theorem proving is the process of finding a proof of a property from the axioms of the system.

Model checking is a technique that relies on building a finite model of a system and checking that a desired property holds in that model [11]. The check is performed as an exhaustive state space search which is guaranteed to terminate since the model is finite. Model checking produces counterexamples, which usually represent subtle errors in design, and thus can be used to aid in debugging [11]. Despite these advantages, model checking suffers from the state explosion problem.

In this master's thesis, we developed a model abstraction for Fiasco IPC (Inter-Process Communication) and applied model checking to verify it. The microkernel Fiasco is an implementation of the L4 interface in C++. It is used in the context of DROPS (Dresden Real-Time Operating System Project). DROPS is a research project aiming at the support of applications with Quality of Service requirements. The Fiasco IPC abstraction is focused on short IPC with features such as thread lock and zero timeout. The abstraction should have the form of a finite state automaton, where one automaton models one process that is engaged in an IPC. For the verification several such automaton are set in parallel.

The preferred formalism for the IPC model is Promela (Process Meta Language). Promela is a nondeterministic language which is loosely based on Dijkstra's guarded command language notation. Promela also borrows the notation for input output operation from Hoare's CSP (Communicating Sequential Processes). The choice on Promela is de-

2 Fiasco IPC

cided based on the fact that Fiasco is written in C++, while Promela's syntax resembles the syntax of C programming language.

SPIN (Simple Promela Interpreter) will be used as the model checker. SPIN receives models specified in Promela. The properties can be expressed as LTL (Linear Temporal Logic) formulae for SPIN to verify. Properties of interest for the verification are deadlock, livelock, safety properties or liveness properties. SPIN has been developed at Bell Labs since the eighties. It has been available freely since 1991 at [2]. It continues to be upgraded to keep in line with new developments in the field of formal verification. In April 2002, SPIN was awarded the System Software Award for 2001 by ACM. Some documentations, manuals and tutorials about Promela and SPIN can be found in [1, 2, 8, 9, 10].

This master's thesis report is organized as follows.

- Section 2 gives a brief overview of Fiasco IPC.

- Section 3 describes some interesting features of Promela which are used in modeling the Fiasco IPC.

- Section 4 provides explanation of how we abstract the real Fiasco IPC code until we come up with our model.

- Section 5 reports the various simulation and verification efforts for our model.

- Section 6 draws conclusions from this master's thesis, both in the context of our experience in translating C++ code to Promela and our experience with Promela and SPIN. This section also proposes some future works.

# 2 Fiasco IPC

This section is intended to provide an overview about Fiasco IPC. Before doing so, we feel the necessity to provide some brief information about L4 and Fiasco itself in Section 2.1. Further, we summarize the important facts about IPC in Section 2.2. For more detail and comprehensive reference about Fiasco IPC, we suggest to consult [3, 4, 5].

# 2.1 L4 and Fiasco

Fiasco is a new implementation of the L4 interface for the x86 architecture. L4 itself is an operating system microkernel [7]. By microkernel, we mean that it alone is not an operating system in the traditional sense, but rather constitutes a minimal base on which a variety of complete operating systems can be built. A microkernel is an operating system kernel which provides only essential services such as tasks, threads, inter-process communication (IPC), and memory management primitives.

L4 is a microkernel interface defined by Jochen Liedtke [7]. Currently, there exist L4 implementations for:

- x86 architecture (by Jochen Liedtke),

- MIPS CPU (by University of New South Wales),

- Alpha CPU (by Sebastion Schonberg).

Fiasco is meant to replace the L4/x86 microkernel and it is designed with the following intended characteristics[5]:

- having good real-time properties. This means that Fiasco kernel should be preemptible: interrupts shall be deliverable at virtually any time.

- maintainable. To achieve this, Fiasco is written in a high-level language, C++. Only five percent of assembler codes is allowed when we need to implement low-level operations or to meet the performance requirements. The source code of Fiasco shall be organized in subsystems with clean programming interfaces so that it is easy to replace subsystem implementation.

- not need to be portable, but it should serve as a model for future L4 implementation,

- distributed under a freeware (open source) license. This means that Fiasco shall not

contain components which are not freeware, and that all tools and documentation

necessary to build and use Fiasco should also be freeware.

# 2.2 How IPC Works

IPC is one of the system calls in Fiasco. It is the secure, kernel-assisted message transfer between a sender and a receiver [3]. Parties that are involved in an IPC are threads which act as a sender and a receiver, respectively. A successful IPC operation consists of a handshake and a message transfer between a sender and a receiver [3]. In L4, there is only one kind of IPC receiver, that is the thread, and two kinds of IPC senders, those are thread and (kernel-internal) hardware-interrupt signal. In the operating system world, thread is defined as a basic unit of CPU utilization and it must live inside a process [7].

During IPC, the sender executes a send operation and the receiver executes a receive operation. Send operations are always addressed to a receiving thread. Receive operations can be parameterized to only accept messages from a specified sender (*closed wait*) or from any sender (*open wait*). Both operations have a timeout parameter that limits the duration of blocking while waiting for an IPC partner.

The maximum possible operations in one IPC system call are one single send operation, followed by one single receive operation. This particular system-call mode is named *call* or *reply-and-wait*, depending on whether the involved receive operation is a closed or an open wait, respectively.

The server usually uses a zero timeout for its send operations to prevent unresponsive clients from stalling the server. L4 supports this programming convention by guaranteeing that a client that sent a request using a call is ready to receive an answer as soon as the server received the request. In other words, shift from send mode to receive mode in calls and reply-and-wait is atomic.

# 2.2.1 IPC States

Two threads involved in an IPC keep track of their own state and also modify their IPC partner's state. That is the reason why IPC states need to be represented as explicit data, i.e, as part of the each thread's state word [3]. The states are defined by bit patterns in the state word, as shown in Table 1.

4 2 Fiasco IPC

| State             | State flags used in IPC |           |     |      |      |      |      |      |        |

|-------------------|-------------------------|-----------|-----|------|------|------|------|------|--------|

|                   | ready                   | receiving | ipc | send | busy | busy | poll | poll | cancel |

|                   |                         |           |     |      |      | long |      | long |        |

| Sender states     |                         |           |     |      |      |      |      |      |        |

| send prepared     | +                       |           | +   | +    |      |      | +    | -    |        |

| sleeping          | _                       |           | +   | +    |      |      | +    | -    |        |

| woken up          | +                       |           | +   | +    |      |      | -    | -    |        |

| long IPC in       | +                       |           | +   | +    |      |      | -    | -    |        |

| progress          |                         |           |     |      |      |      |      |      |        |

| page fault in IPC | +                       |           | +   | +    |      |      | -    | +    |        |

| window            |                         |           |     |      |      |      |      |      |        |

| page-in wait      | -                       |           | +   | +    |      |      | -    | +    |        |

| after send        | +                       |           |     | -    |      |      |      |      |        |

| Receiver states   |                         |           |     |      |      |      |      |      |        |

| setup             | +                       |           | +   |      |      |      |      |      |        |

| prepared          | +                       | +         | +   | -    | -    | -    |      |      |        |

| going to          | +                       | +         | +   | -    | +    | -    |      |      |        |

| rendezvous        |                         |           |     |      |      |      |      |      |        |

| waiting           | -                       | +         | +   | -    | +    | -    |      |      |        |

| in long IPC       | -                       | +         | +   | -    | -    | +    |      |      |        |

| page-in           | +                       | +         | +   | -    | -    | +    |      |      |        |

| after receive     | +                       |           |     | -    |      |      |      |      |        |

|                   |                         |           |     |      |      |      |      |      |        |

Legend: + = flag set; - = flag cleared; otherwise, flags can be set or cleared.

Table 1: Sender and Receiver States

Each state transition changes the bit pattern in a unique way. But two states can have the same pattern if there is no transition between them. It is important to notice, that not all bits are significant for each state. This allows a thread to stay in receiver-setup state while carrying out a send operation. Therefore, for a combined send-receive IPC, Fiasco can set up the receive operation before carrying out a send operation. This allows the thread to atomically switch from a sender state to a receiver state by clearing the "send" flag. In the sender states, the additional flags used for receiving are irrelevant.

Fiasco must check the validity of every state transition. Since Fiasco allows preemption and parallel execution of sender and receiver, state checking and modification should be atomic from the IPC's partner point of view.

## 2.2.2 IPC Phases

An IPC can maximally contains one send operation and one receive operation. A thread which is engaged in such an IPC performs the IPC in the following order:

- 1. setup for receive operation (as a receiver),

- 2. do send operation (as a sender),

3. do receive operation (as a receiver).

It is important to note from the order above that send operation is *always* performed before receive operation. But receive setup phase always takes place before a send operation [3]. This adopted convention facilitates atomic switching from the send part to the receive part. In effect, this fulfills the L4 specification requirement that threads must accept reply IPC immediately, without requiring a timeout in the sender.

In general, both send and receive IPC operations can be grouped into four phases. Those phases are described as follows:

## • Setup

During setup, a thread can do the following based on send or receive part:

- In receive part: the thread sets up its TCB (Thread Control Block) so that it can be a receiver. For a closed-wait receive, the thread sets its TCB's IPCpartner attribute to point to the desired IPC partner's TCB.

- In send part: the thread set its TCB's IPC send-partner attribute to point to the desired IPC partner's TCB. Then it puts itself into state "send prepared".

Next, it enqueues its TCB in the receiver's sender list.

#### • Rendezvous

During rendezvous, the sender is the active party and the receiver becomes passive (goes to sleep). The sender will wake up the receiver when the receiver needs to page in a virtual-memory page (in the receiver's address space), or when the IPC has been finished.

Once the receiver has entered the "prepared" state, senders can asynchronously rendezvous using method ipc\_send\_regs, for example, by putting the receiver into the final state (for short IPC) or into state "in long IPC" (for long IPC).

However, the receiver would normally proceed to state "going to rendezvous" where it checks if a sender has queued in the receiver's sender queue. If that is the case, the receiver wakes up the sender using the <code>ipc\_receiver\_ready</code> operation; the sender becomes active, rendezvouses and executes the IPC. The sender in the end will put the receiver into final state or state "in long IPC".

If there is no sender waiting for a rendezvous, the receiver tries to proceed to state waiting where it sleeps until a sender rendezvous. This change from state "going to rendezvous" to state waiting only succeeds if no sender has asynchronously put the receiver into another state (prepared, in long IPC, or final), in which case execution proceeds there. Meanwhile, the sender prepares for IPC by entering state send prepared. It queues in the receiver's sender queue and attempts a first rendezvous using <code>ipc\_send\_regs</code>. If successful, the sender directly proceeds to its final state (for short IPC) or "long IPC in progress" (for long IPC). Otherwise it starts sleeping by going to state sleeping. When a receiver sends an <code>ipc\_receiver\_ready</code> request, the sender continues in state woken up. It then switches back to state send prepared where it retries the <code>ipc\_send\_regs</code> operation.

## • Data Transfer

The receiver enters this phase only when the sender starts a long message transfer by putting the receiver into state "in long IPC". On the other hand, the sender

6 3 Promela

enters this phase when ipc\_snd\_regs cannot complete the IPC without looking at IPC-message buffers in user memory. Our model does not include this phase since we only model short IPC.

#### • Finish

For the receiver, IPC finishes when the "ipc" state flag is removed from its state word. For the sender, send operation finishes when an error condition removes the "ipc" state flag, and it also has to monitor its state word to detect this condition. Otherwise, the send operation ends when the "send" flag is removed, that is when the sender enters its final state. When reaching that state, the sender needs to check if the send operation is followed by a receive operation. If it is not followed by a receive operation, then the "ipc" state flag is removed also.

# 3 Promela

This section is meant to provide an overview of Promela. Promela is a specification language which is accepted by SPIN. Promela provides formalisms to abstract distributed systems and produces models for verification in SPIN. SPIN is a model checker tool to check those verification models. More hands-on experience with SPIN will be covered in the simulation and verification phases. We will explain about those two phases in the Section 5.

As a specification language, Promela has features which would help its users in modeling process synchronization and coordination. It is intended for systems description language, instead of implementation language. In line with these facts, Promela has few computational functionalities. Furthermore, it has no notion of time or clock and it does not have floating point numbers.

For detail reference about Promela, we suggest to consult the book "The SPIN Model Checker: Primer and Reference Manual" by Gerard J. Holzmann [1]. In this report, we cover only certain features of Promela which are used in our model. Examples will be given along the way, taken from the actual Fiasco IPC model.

This section is organized as follows. In Section 3.1, we give a general comparison between Promela and programming languages. In Section 3.2, we explain about data types and data objects that we use in our Promela model. In Section 3.3, we explain about Promela processes. Then in Section 3.4, we give explanation about Promela meta terms and basic statements. Finally in Section 3.5, we cover the compound statements.

# 3.1 Promela vs Programming Languages

For people who have done some programming, especially in C language, Promela would seem familiar and learning about it would not be a difficult task. This is due to the fact that Promela adopts some syntaxes from C programming language. Those similar syntaxes include the following:

- boolean and arithmetic operators,

- assignment and equality, using a single equal and double equals,

- variable and parameter declarations,

- variable initialization and comments, and

- the use of curly braces to indicate the beginning and end of program blocks.

After learning the similarities, now we continue by mentioning some primary differences between Promela and C language, such as:

- semicolon in Promela is used as a statement separator, while in C, it is used as a statement terminator. So it will not be a syntax error in Promela as it is in C when the last statement of a sequence is not ended by a semicolon.

- Promela's main unit of execution is a process, while in C it is the main function.

From the above explanation, we get a brief overview of the similarities and differences between Promela and the C programming language. Now we try to compare Promela with common programming languages in broader sense. First, we will give features of most common programming languages which are **not** possessed by Promela:

- 1. functions that return values. Having no functions that return values leads Promela to have only two levels of scope. The first is global to the whole Promela model. The second level is local to a certain process.

- 2. expressions with side effects, which is allowed in C, for example:

```

counter = x++;

```

3. pointers.

Features of Promela which can not be found in most programming languages are as follows:

- 1. the specification of nondeterministic control structures. Nondeterminism of Promela can arise as follows:

- If there are multiple guard conditions which evaluate to true at the same time, SPIN will select one of these guards nondeterministically for execution.

- If there is more than one process that has an executable statement and that

could proceed at any point in an execution, then the semantics of Promela state

that any of these processes may be selected for execution and the choice itself

is nondeterministic.

This nondeterminism will be clear as soon as we explain the whole Promela syntax and semantic in the next subsections.

- 2. primitives for process creation, and

- 3. a rich set of primitives for interprocess communication.

The basic building blocks of Promela models that we use are: structured data, asynchronous processes, and synchronizing statements. We will discuss in more detail each of these building blocks in the following subsections.

3 Promela

| bit   | 0,1               |

|-------|-------------------|

| bool  | false, true       |

| byte  | 0255              |

| pid   | 0255              |

| short | $-2^{15}2^{15}-1$ |

| int   | $-2^{31}2^{31}-1$ |

Table 2: Basic Data Types

# 3.2 Data Types and Data Objects

Promela has some basic data types which are almost similar to C's data types. The range of values for each Promela's data type depends typically on the machine used. Table 2 summarizes the basic data types used in our Promela model and their typical value range on most machines.

Promela requires that all variables are declared before they can be used. We give below some examples of our model's variables declaration with the types from the basic data types above:

```

bool have_sender;

short sender;

```

We can also declare one-dimensional arrays of variables in Promela as follows:

```

short rcv_partner[N];

short snd_partner[N];

```

The variable N which represents the number of threads in our model are used above to denote the size of the arrays. The definition of N as a macro is given as follows:

```

#define N 2

```

We can also define new data types of record structures. The following example introduces the structure IPC\_prm and declares an array variable <code>ipc\_g\_prm</code> of this new structure:

```

typedef IPC_prm

{

bool has_receive_part;

bool open_wait;

short partner;

bool has_send_part;

};

IPC_prm ipc_g_prm[N];

```

# 3.3 Processes

A process is the main unit of execution in Promela model. There should be at least one process declaration and one process instantiation for a model to be useful for modeling a

distributed system. We have only one type of process in this master's thesis, the thread process type, which is given as follows:

```

active [N] proctype thread()

provided (ipc_lock_owner[_pid] == -1 || ipc_lock_owner[_pid] == _pid)

{

...

}

```

Process types are always declared globally in Promela. The keyword proctype followed by the identifier thread introduces a new type of process. So the "proctype thread" above defines the behavior of a process, not its execution. A proctype body may consists of zero or more data declarations and at least one statement.

The keyword active indicates that we want this process type to be instantiated. Following the keyword active, we have [N] which is how we tell that we want N processes to be instantiated of the same process type thread.

In the example above, we also use provided clause following the empty parameter list of proctype declaration. A provided clause begins with the keyword provided and followed by a conditional statement in round bracket. It defines additional global constraints on process executions. In our model, the provided clause imposes that our processes of the process type thread cannot take any step unless the value of ipc\_lock\_owner[\_pid] evaluates to -1 or to the process' pid. The absence of provided clause would be interpreted as the expression true which imposes no constraints on process executions.

Promela has other ways to instantiate a process, using the keyword init and run. But we will not use them here. More information about them can be found in [1].

Active processes can be differentiated from each other by the value of their process instantiation number, which is available in the predefined local variable <code>\_pid</code>. The <code>\_pid</code> is a non-negative integer starting from zero and assigned in order of process creation. Because Promela defines finite state systems, the number of processes is required to be bounded. SPIN limits the number of active processes to 255.

Since Promela supports asynchronous processes, a newly created process need not to start executing immediately after instantiation. Each process can interleave its executions with other processes in a nondeterministic way.

Promela processes can terminate and die. These two actions are different in the following sense:

- A process terminates when it reaches the end of its code. When a process terminates, it does not necessarily die. It indeed has no more statements to execute, but it will still be regarded as an active process in the system and the pid stays associated with this process.

- A process dies when it is removed from the system and its pid can be reused for another process.

# 3.4 Meta Terms and Basic Statements

In our Promela model, we use many Promela meta terms and basic statements. Meta terms that we use in our model include the following:

• inline,

10 3 Promela

- boolean values: false and true,

- comments (starts with a /\* and ends with a \*/),

- skip (performs no operation),

- macros, and

- LTL (Linear Temporal Logic),

Interesting meta terms to discuss are inline and LTL. We will discuss about inline in Subsection 3.4.1. LTL will be part of verification phase which is discussed in Section 5.

For basic statements, we use assert, printf, and conditional statement. All these basic statements are the same as what we would find in C programming language. More information about assert statement will be given in Section 5, when we speak about correctness property.

### 3.4.1 Inline

A Promela inline is very similar to C-style macro definition. It is very useful for structuring and organizing a Promela model. At an inline's point of invocation in the Promela code, the SPIN parser performs the following:

- a textual substitution of the body of the inline definition,

- a direct textual substitution of all actual parameter names (that are provided at the point of invocation) for the formal names that are used in the definition.

Formal parameters of an inline definition have no type specification. They are just place holders for the actual variable names that are inserted when the inline is invoked. The body of an inline definition can contain declarations for local variables, but they will be included in the text segment that is inserted at each point of invocation. Therefore, their scope depends on the point of invocation of the inline.

The general rules are that an inline definition must appear before its first use, and must always be defined globally. It may itself contain other inline calls, but it may not call itself recursively. Below is an example of an inline definition do\_send from our model with three parameters: ds\_pid, ds\_partner, and ds\_ret:

```

inline do_send(ds_pid, ds_partner, ds_ret)

{

...

}

```

# 3.5 Compound Statements

Compound statement is a construct which comprises of other smaller statements as constituents. There are five types of compound statements in Promela, viz. atomic sequences, deterministic steps, selections, repetitions and escape sequence. In the following subsections, we only discuss compound statements which we will use in our Promela model.

# 3.5.1 Atomic Sequences

Here is an example of atomic sequence:

```

atomic {

assert(ipc_lock_owner[iu_rec_pid] == iu_snd_pid);

ipc_lock_owner[iu_rec_pid] = -1

}

```

Atomic sequence is the simplest compound statement which is uninterruptable. This means that all statements inside an atomic sequence will be executed as one indivisible unit, non-interleaved with other processes. All steps in the sequence will complete before any other process is given the chance to execute.

If any statement in atomic sequence is unexecutable, then the atomic chain is broken and another process can take over control. When the blocking statement becomes executable later, control can nondeterministically return to the process and the atomic execution resumes as if it had not been interrupted.

## 3.5.2 Selection Construct

A Promela selection construct starts with the keyword if and ends with fi. The selection body should contain one or more option sequences, with every single option sequences starts with a double colon ::. The first statement after the double colon :: in each sequence is called the guard. The following is an example of an if selection construct taken from our model:

The above selection structure contains two option sequences. The first sequence's guard is (so\_snd\_pid == rcv\_partner[so\_rec\_pid]). The second is else which represents the negation of the first guard. Removing the else option would make execution blocks until the first guard evaluates to true. This facilitates modeling interprocess synchronization.

Only one sequence from the list will be executed. A sequence can be selected only if its guard statement is executable. In the example, the two guards are mutually exclusive, but this is not required. If more than one guard statement are executable, then one of them will be selected nondeterministically. When none of the guards is true, executions will block and it is not regarded as an error. These two characteristics make Promela different from other programming languages. They are very useful to synchronize processes in Promela models.

Another difference between Promela and other programming languages is that Promela does not restrict the type of statements that can be used as a guard. It may be an assignment, printf, skip, etc. Below is another example of if construct which at first might seem a little bit confusing:

3 Promela

```

if

:: ipc_g_prm[_pid].has_receive_part = false

:: ipc_g_prm[_pid].has_receive_part = true

```

The above if construct contains two option sequences, where each sequence has an assignment as the guard. Because assignments are always executable, here Promela introduces its nondeterminism in choosing which option sequence to execute.

Another form of Promela selection construct can also be written in the following way:

```

(ipc_lock_owner[irr_snd_pid] == -1);

ipc_lock_owner[irr_snd_pid] = irr_rec_pid;

```

This example shows that Promela treats a condition as a full statement. In the above example, we use semicolon after the condition (ipc\_lock\_owner[irr\_snd\_pid] == -1). Actually we could also write the above construct with an arrow after the condition as the following:

```

(ipc_lock_owner[irr_snd_pid] == -1) ->

ipc_lock_owner[irr_snd_pid] = irr_rec_pid;

```

The above two examples are equivalent because arrows and semicolons are equivalent in Promela. In general, usually only a condition is followed by an arrow as a statement separator. The reason is because a condition has the possibility to block the execution when it does not evaluate to true. All other statements are followed by a semicolon. But this preference between arrow and semicolon is not imposed by Promela grammar. Further analysis will lead us to the following busy wait cycle which is the long form of the above two examples:

# 3.5.3 Repetition Construct

A Promela repetition construct starts with the keyword do and ends with od. The repetition body should contain one or more option sequences. It is almost similar to Promela selection construct. The only difference between a selection and a repetition construct is that a repetition is automatically repeated from the start when the execution of an option completes. Whereas for a selection construct, execution moves on to the next statement. The execution of a repetition can be broken by either transfering control explicitly by a goto statement, or by executing a break statement. Here is an example of repetition construct:

```

in_snd_ls = true;

break

:: ((sender_ls[ds_partner].snd_ls[i] != ds_pid) &&

(i < (sender_ls[ds_partner].last_index - 1)))    ->

i++

:: else ->

break

od;

```

# 4 Modeling Design

This section reports the design process of the Fiasco IPC model. As we have mentioned before, the original Fiasco source code is written in C++. The IPC system call is performed by the sys\_ipc method of Class Thread. There are a lot of abstractions which have to be made to convert from the object-oriented paradigm of the Fiasco C++ code into Promela formalism.

This Section is organized as follows. In Section 4.1, we will explain which conventions that we follow in modeling the Fiasco IPC. In Section 4.2 and 4.3, we explain how we translate the threads and variables of IPC, respectively, into Promela. In the last part, Section 4.4, we describe the inlines in general and we give an example of how we translate a C++ function into a Promela inline.

# 4.1 General Modeling Conventions

The IPC system call is quite complex with many additional features which are outside the scope of our model, such as long IPC, next-period IPC, page-fault IPC, or interrupt IPC. In this master's thesis, we only model short IPC with the following features:

- thread lock,

- timeout is always set to zero,

- data copying is represented by a boolean value which indicates whether the data has been copied or not. We do not model the actual message, since we are interested more in the executions of IPC rather than the result of a message delivery through IPC.

Even with such a simple modeling design, we come up with quite a complicated Promela model due to the delicate executions of IPC, with a lot of inline calls. The primary guidance rules in the modeling design are as follows:

- there is only one process type, that is the thread,

- the scope of the threads' IPC parameters and IPC states variables are global,

- the model performs the following nondeterministic choice of IPC parameters:

- having receive part or not,

- having send part or not,

- whether or not the receive operation is an open receive,

- which thread is to be the partner.

- thread runs continuously in a loop for doing IPC,

We assign integer values as error code to the following specific error messages:

- Transient Error = -1

- Send Error / Enotexistent = -2 (Receiver does not exist)

- Retimeout = -3 (Receive timeout)

- Setimeout = -4 (Send timeout)

- Recanceled = -5 (Receive canceled)

- Secanceled = -6 (Send canceled)

- Reaborted = -7 (Receive aborted)

# 4.2 Thread in Promela

Fiasco's threads are modeled as Promela's proctype construct. In our model, the only type of process is thread. We build our model to be able to have variable number of threads. To do that, we use a constant N to represent the number of threads. The definition of N as a macro has been given in Section 3.2. The complete definition of thread is given in the Appendix, with the specific location: "loc 90"

The process type thread performs an infinite loop, where in each loop, it is assigned to do an IPC with a nondeterministic choice of IPC parameters. Possibilities of thread id are as follows:

- nil thread: -2,

- invalid thread id or null pointer: -1,

- existing thread:  $0, \ldots, N-1$ ,

- non-existing thread: > N

# 4.3 Global Variables

In this subsection, we will elaborate on the data objects used in the model. As we have explained in Section 3, there are only two levels of scope in Promela models, viz. global and process local scope. The scope of a variable is global if it is declared outside all process declarations. It is local if it is declared inside a process declaration.

The reason why we assign some variables to be in global scope is because IPC requires the sender and the receiver to access each other's state. This can be done easily using global variables. Another second important reason is because later on in the verification phase, we will need to specify properties in never claims construct which could only work based on global variables.

In the following, we will explain about the global variables used in our model. We start by giving the definition of data types IPC\_Prm and IPC\_Output as follows:

```

typedef IPC_Prm

{

bool has_receive_part;

bool open_wait;

short partner;

bool has_send_part;

};

typedef IPC_Output

{

short error = -10;

short dope = -10;

bool msg_copied;

short rcv_source = -1;

}

```

The above two data types are intended to save the value of the IPC parameters and the IPC output for each thread. We derive these two data types as an abstraction from the registers described in [5]. Then we declare the array variable <code>ipc\_g\_prm</code> and <code>ipc\_output</code> to be of type <code>IPC\_Prm</code> and <code>IPC\_Output</code>, respectively.

```

IPC_Prm ipc_g_prm[N];

IPC_Output ipc_output[N];

```

Below we give another data type definition, IPC\_State, and a declaration of array variable ipc\_state of this new type IPC\_State. We model IPC states that we described in Section 2 by defining the data type IPC\_State as follows:

```

typedef IPC_State

{

bit ready;

bit receiving;

bit polling;

bit ipc_in_progress;

bit send_in_progress;

bit busy;

bit cancel;

bit polling_long;

bit busy_long;

bit rcvlong_in_progress;

};

IPC_State ipc_state[N];

```

For the receiver's sender list, we introduce a new data type Sender\_List. It consists of two fields: snd\_ls[N] which is an array of type short, and last\_index which points to the next empty index of the array snd\_ls. The definition of Sender\_List and a declaration of array variable sender\_ls of this type are given below:

```

typedef Sender_List

{

short snd_ls[N];

byte last_index;

};

Sender_List sender_ls[N];

```

In the following, we give declarations of three arrays of type short: ipc\_lock\_owner, rcv\_partner, and snd\_partner:

```

short ipc_lock_owner[N] = -1;

short rcv_partner[N];

short snd_partner[N];

```

As the variable name describes, <code>ipc\_lock\_owner[x]</code> saves the process <code>pid</code> which locks process with <code>pid x</code>. We initialize <code>ipc\_lock\_owner</code> with -1 since this variable is used in the provided clause of process type <code>thread</code>. The executions of process <code>thread</code> depend on the value of this variable. Meanwhile, the array variables <code>rcv\_partner</code> and <code>snd\_partner</code> save the value of thread's partner when it acts as a receiver and as a sender, respectively.

# 4.4 The Inlines

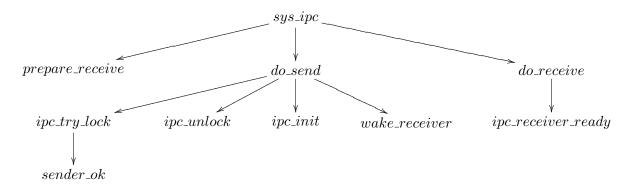

Now we give the structure of the Promela implementation of IPC system call's functions. These functions are modeled as inlines in Promela. The connection between the main function sys\_ipc and the auxiliary functions is depicted in the picture below.

We translate all the above auxiliary functions into Promela inlines. As an example, below we give the C++ function ipc\_try-lock and further below we give the translation result, that is the Promela inline ipc\_try\_lock (note that the comment "loc" followed by a number is intended to match statement in C++ with statement in Promela):

```

inline int Receiver::ipc_try_lock(const Sender* sender) // loc 220

{

if (EXPECT_FALSE (state() == Thread_invalid)) // loc 221

return Ipc_err::Enot_existent; // loc 222

thread_lock()->lock(); // loc 223

```

4.4 The Inlines

```

if (EXPECT_FALSE (!sender_ok (sender)))

// loc 224

{

thread_lock()->clear();

// loc 225

return -1;

// loc 226

}

// OK, loc 227

return 0;

}

inline ipc_try_lock (itl_snd_pid, itl_rec_pid, itl_ret) /* loc 220 */

{

bool sok;

printf("ipc_try_lock(snd:%d, rec:%d, ret:%d)\n",

itl_snd_pid, itl_rec_pid, itl_ret);

if

:: (itl_rec_pid >= N) ->

/* loc 221 */

itl\_ret = -2

/* loc 222 */

:: else ->

atomic {

assert(ipc_lock_owner[itl_rec_pid] != itl_snd_pid);

(ipc_lock_owner[itl_rec_pid] == -1);

ipc_lock_owner[itl_rec_pid] = itl_snd_pid; /* loc 223 */

}

sender_ok(itl_snd_pid, itl_rec_pid, sok);

/* loc 224 */

printf("sender_ok returned %d\n", sok);

if

/* loc 224 */

:: sok ->

/* loc 227 */

itl_ret = 0

:: else ->

/* loc 225 */

atomic {

assert(ipc_lock_owner[itl_rec_pid] == itl_snd_pid);

ipc_lock_owner[itl_rec_pid] = -1;

}

itl\_ret = -1

/* loc 226 */

fi

fi;

}

```

The C++ function ipc\_try\_lock is designed to run in the context of the Receiver object and it has one parameter which is the Sender object. Since Promela is a process-based language, these object-oriented paradigm cannot be matched. As a solution, we translated the Sender object into sender thread's pid: itl\_snd\_pid and add one addi-

tional parameter for the value of receiver thread's pid: itl\_rec\_pid which represents the context of object Receiver in the original code. For the integer return values in C++' ipc\_try\_lock, Promela inline does not have this feature either. Again, the solution was to add another additional parameter for the return value, viz. itl\_ret.

Now we base the explanation on the Promela inline. For every statement with specific comment "loc" in Promela, the corresponding original C++ code can be traced by the same comment. The Promela inline starts by declaring a variable sok of type bool. Then it prints some information using printf which resembles C syntax. On loc 221, it checks the receiver pid's validity. If the receiver is not valid, then ipc\_try\_lock will set the value of parameter itl\_ret into -2 which codes the error Enot\_existent (receiver does not exist). If the receiver is valid, it is locked on loc 223. The locking action is done in an atomic sequence, which is preceded by two other statements. The first statement asserts that the receiver has not yet been locked by the sender. The second is a conditional statement which requires the process to wait until the receiver is not locked by any process, which is coded by -1.

After the receiver is locked, <code>ipc\_try\_lock</code> calls the inline <code>sender\_ok(itl\_snd\_pid, itl\_rec\_pid, sok)</code> and check the return value in the parameter <code>sok</code>. Both actions are marked by the comment <code>loc 224</code>. If the return value <code>sok</code> is true, <code>itl\_ret</code> will be set to 0 on <code>loc 227</code>. Otherwise, the receiver's lock will be cleared on <code>loc 225</code>. This is done in atomic sequence consisting of two statements. The first one is a conditional statement which requires that the receiver's lock owner is the sender. The second is the action of clearing the lock by setting the receiver's lock owner to <code>-1</code>. Later on <code>loc 226</code>, <code>ipc\_try\_lock</code> will return <code>-1</code> which is saved in parameter <code>itl\_ret</code>.

Below is a brief structure of the inline ipc\_snd\_regs which calls the inline ipc\_try\_lock and checks ipc\_try\_lock's return value by examining the third parameter isr\_ret.

# 5 SPIN Simulation and Verification

In this Section, we will explain about the simulation and verification of the model using SPIN. We have explained about how our model was built in the previous two sections. After the model is free from any syntax or typographical error, we do some simulations to get an idea of how the model really works, and then continue with the verification phase. When errors were found during verification, we sometimes switched back to simulation to trace the error. This shows how close is the role of simulation and verification in SPIN.

5.1 Simulation 19

In essence, the two modes of SPIN can be described as follows:

• simulation mode: can give a quick impression of the types of the behaviour that are captured by system model. Simulation itself cannot prove the facts we are interested in.

• verification mode: can prove the facts. When the verifier finds a counterexample to a correctness claim, it relies on SPIN simulation mode to display the error trace using guided simulation.

Logical verification focuses on determining whether design requirements could possibly be violated, not on how likely/unlikely such violations might be. This focus will lead us to achieve system verification where we can state that there is no possible violation of a given requirement.

The verification was done in a series of steps repetitively with increasingly detailed models. Interesting properties to verify are: the absence of deadlock or livelock, the absence of fail condition, or some liveness properties. In SPIN, verification of safety and liveness properties must be done separately. Specifically, safety and liveness properties are classified as follows:

- 1. safety properties (which is SPIN default): assertion violations, deadlocks,

- 2. liveness properties: the absence of acceptance cycles.

We will explain briefly about acceptance cycles in Section 5.2.

This section is organized as follows. First, in Section 5.1, we explain briefly about simulation mode in SPIN. Then in Section 5.2, we give a general overview of various correctness property in SPIN. In Section 5.3, 5.4, and 5.5, we give explanation on how to generate, to compile and to run the verifier, respectively. Finally, in Section 5.6, we describe our efforts in veriging our model using the knowledge that we have explained in the previous four subsections.

# 5.1 Simulation

SPIN offers three kinds of simulation as follows:

- random simulation,

- interactive simulation, and

- guided simulation.

In the beginning of our modeling phase, we used mostly the random simulation to get an insight about the behaviour of the model. After all small modeling errors have been fixed, then we continue with the verification phase.

The beginning of verification phase reports many kinds of errors which we do not find in the simulation. When we find errors, we use guided simulation to trace the errors. SPIN's guided simulation uses trail files which are generated only in verification mode when the verifier finds a counterexample. The SPIN's graphical user interface, XSPIN, helps us conveniently debug the errors. More information about SPIN's simulation mode and XSPIN can be found in [1].

# 5.2 Correctness Property

From the verifier point of view, there are two types of correctness properties:

- 1. states properties: claims about reachable and unreachable states,

- 2. path properties: claims about feasible or infeasible executions, i.e sequence of states.

SPIN can check the above two claims, which are expressed in Promela. There are some basic properties which SPIN checks by default, such as, the absence of system deadlock states. Promela constructs that we use in our model to formalize correctness property are as follows:

## 1. Basic Assertion

Basic assertions in Promela are statements of the form

## assert(expression).

The characteristic of Promela basic assertion is that it is always executable, but has no effect as long as the expression specified evaluates to *true* or to a nonzero value. It has an implied correctness property that it is never possible for the expression to evaluate to *false* or zero. A failing assertion will trigger an error message. Basic assertion is the only type of correctness property in Promela that can be checked during simulation runs with SPIN.

# 2. Accept States

An accept-state label is any label starting with the string "accept". The implicit correctness claim that is expressed by accept-state label is that there should not exist any execution that can pass through an accept-state label infinitely often.

It is important to note that we do not explicitly use accept -state labels in our model. They are only used in some never claims which are generated from LTL formulae. We explain about never claims below.

# 3. Never Claims

Never claim is used to specify behavior that should **never** happen in the system executions. It is the only Promela construct which is capable of checking system properties just before and just after each statement execution. This checking is always performed no matter which process executes a statement.

We can write our own never claims by hand or they can be generated mechanically from LTL formulae by using SPIN command-line option -f. Almost all Promela language constructs can be used inside a never claim, except the ones that have side effect, such as assignments. The limitation is that never claims can only access global variables of a Promela model.

Never claims can be used to match either finite or infinite behavior. A finite behavior is matched if the claim can reach its final state, that is the last part of the claim (the

closing curly brace). An infite behavior is matched if the claim contains acceptance cycle.

A simple example of never claim is the one which is used to check system invariance, which is a safety property. For instance, if **p** is a system invariant property, then the never claim can be written by checking the opposite behavior of the system, that is !p, as follows:

```

never {

do

:: !p -> break

:: else

od

}

```

As soon as p evaluates to false, then the never claim breaks from its loop and terminates, which indicates that error behavior has occured. On the other hand, if p remains true, then the never claim stays in its initial state and this is the behavior that we have expected.

We can include a never claim as part of the model. The other choice is to save it in a separate file. The latter case is normally chosen when there are various claims to be verified for the same model. For the latter case, we use the additional option -N followed by the name of the never claim file when generating the verifier, as follows:

```

> spin -a -N never_claim_file model_file

```

Never claims that we explain above are quite expressive and powerful. But it can be hard to be produce never claims which specify complex temporal properties of a distributed system. To answer this problem, SPIN allows us to specify properties in LTL formulae and it can translate those LTL formulae into never claims. More information about LTL formulae are given below.

# 4. LTL

SPIN has a separate parser which converts LTL formulae into Promela never claims. To invoke this converter, we use the command:

```

> spin -f LTL_formula

```

The argument LTL\_formula given to the command above should be started and ended with a quote. The LTL formulae which can be accepted by SPIN should only consists of:

- propositional symbols (including true and false),

- unary temporal temporal operators: [] ("always" or "box") and <> ("eventually" or "diamond"),

- binary temporal operator: U ("until" strong version),

- three logical operators: ! (negation), && (and), || (or), -> (logical implication).

The propositional symbols which represent state properties are always written with lower-case symbols, for instance, p or q. It is important to remember that LTL formulae to be translated by SPIN cannot contain arithmetic and relational operators.

An example of more complex temporal property than just an invariance property is:

Every system state in which p is true eventually leads to a system state in which q is true

This property can be captured by LTL formulae:

$$[](p -> <> q)$$

To show that the above property should not be violated, we must give the negated version of the formula above to the SPIN converter and the never claim is generated, as follows:

# 5.3 Generating The Verifier

The most important feature of SPIN is probably that it can generate optimized verifiers from a user-defined Promela model [1]. Assuming that our model is in a file called sys\_ipc.pml, we can generate the source code for our model specific verifier by typing:

```

spin -a sys_ipc.pml

```

The verifier is generated as a C program that is stored in a number of files. Those files have a fixed set of names, starting with a three-letter prefix pan. They include the following [1]:

- pan.h is the generic header file for the verifier that contains, for instance, the translated declarations of all global variables and all process types.

- pan.m defines the executability rules for all Promela statements used in the model and their effect on the system state after successfully executed.

- pan.b defines how the effect of each statement from pan.m can be undone when the direction of the depth-first search is reversed.

# • pan.t

contains the transition matrix that encodes the labeled transition system for each process type.

#### • pan.c

contains the computation algorithms, the state space maintenance and cycle detection algorithms, encoding optimized versions of either a depth-first or a breadth-first search.

The source code can further be compiled using various compile-time options to produce an optimized executable verifier. Next, the verifier is run, possibly with some run-time options to get the best verification run. Both compilation and run of the verifier are explained in the following two subsections.

# 5.4 Compiling The Verifier

To compile the verifier for a straight exhaustive verification, without using any compiletime option, we can just compile the file pan.c using the command:

```

gcc -o pan pan.c

```

The file pan.c includes all other files that are generated by SPIN. So, it is enough to give only this file to the compiler. The result of the compilation command above is an executable file called pan. From this point until the end of Section 5, we assume that we always compile pan.c into an executable file called pan.

The use of compile-time options is not a must. However, in our verification, we would need to use some specific compile-time options for the sake of efficiency. In fact, those options would turn out to be a great help for running the verification later. In principle, compile-time options help us to form the behavior of the verifier. We explain some compile-time options [1] that are useful in our verification as follows:

# 1. Basic options:

## • -DBFS

tells the verifier to use a breadth-first search algorithm rather than the default depth-first search. This option is only usable for the search of safety properties violations. It runs slower than depth-first search and can consume more memory. But if memory is not a hindrance, it can help to find the shortest error path. This option can be combined with other options for reducing memory, except the option ¬DSC.

## • -DMEMLIM=N

limits the maximum amount of memory that can be used by the verifier to N Megabytes. This option helps to avoid any paging behavior.

# • -DNP

enables non-progress cycle detection, which later on, enables run-time option -1 and simultaneously disables run-time option -a for acceptance cycle detection.

# 2. Options to increase speed:

#### -DSAFETY

optimizes the code for detection of safety properties violations. This is done when no cycle detection is needed. At run-time, this option disables the options -1 and -a.

#### –DNOFATR.

disables the code for weak fairness algorithm. At run-time, this will disable the option -f.

# 3. Options to decrease memory use:

#### • -DBITSTATE

Uses the bitstate storage algorithm runs to get a better impression of the complexity of the problem that is being tackled. This command does not guarantee exhaustive coverage.

#### -DHC

Compiles with hash-compact option which uses less memory at a small risk of incompleteness of the search.

## -DCOLLAPSE

compiles with the memory collapse option. This preserves an exhaustive verification but uses less memory.

## −DMA=N

Enables the minimized automaton storage method to encode state descriptors. This method can reduce a great amount of memory use, but the trade-off is that it requires quite long run-time. We use this option many times in our verification as we will explain in the next subsection. Further information about this method can be found in [1] page 202.

# • -DSC

is meant only for verification with very large depth-limit. It uses a stack-cycling method. The memory requirements for the stack increase linearly with its maximum depth. This stack-cycling allows only a small part of the stack to reside in memory, with the rest stays on disk. Compiling with this option will make the run-time option  $\neg m$  determine only the size of the in-core portion of the stack, but does not restrict the stack's maximum size.

# 5.5 Running The Verifier

There are some additional options that we can choose in running the verifier to improve its performance. For example, it might be helpful to do the following:

- provide an estimation about the number of reachable states,

- provide the maximum search depth of a non cyclic execution path,

- tell the verifier to search for violations of safety or liveness properties, since the two searches cannot be combined. The default setting is to search for violations of safety properties.

# 5.5.1 Setting the Number of Reachable States

There are two different search modes which have different effects on the setting of the number of reachable states. The two search modes are explained below:

#### 1. Exhaustive search mode:

Exhaustive search mode is performed when the verifier is compiled without any memory compression options. In this mode, the verifier stores all reachable states in a hash table, with a default size of  $2^{18}$  slots. Logically, this state storage method would work effectively if the table as at least as many slots as there are reachable states that will have to be stored in it. If the table has too many slots, memory will be wasted. On the contrary when the table has too few slots, CPU cycles will be wasted. To change from the default size of the hash table to  $2^{25}$  slots, we can do the following command:

### 2. Bitstate mode:

In bitstate mode, each reachable state is stored only using one bit of memory. Given a state, a hash function is used to compute the address of the bit in the hash table. The default size of the hash array is  $2^{22}$  bits. To change the size of the hash array to  $2^{29}$  bits, we do as follows:

The optimal value to be used depends mainly on the amount of physical memory that is available to run the verification. A bitstate run with too small size of hash array will get less coverage, but will run faster.

### 5.5.2 Setting the Search Depth

The default search depth restriction of SPIN verifier is 10,000 steps. If this isn't enough, the search will truncate at 9,999 steps. We can define a different search depth of N steps by the following command:

```

./pan -mN

```

A deeper search depth requires more memory for the search, and this memory cannot be used to store reachable states. In the case that there is not enough memory to allocate a search stack for very deep searches, an alternative is to use SPIN's stack cycling algorithm that arranges for the verifier to swap parts of the search stack to disk during a verification run, retaining only a small portion in memory. Such a search can be set up and executed as follows:

```

spin -a filename

cc -DSC -o pan pan.c

./pan -m100000

```

In the above setting, the value specified with the -m option defines the size of the search stack that will reside in memory. There is no preset maximum search depth in this mode: the search can go arbitrarily deep, or at least it will proceed until the diskspace that is available to store the temporary stack files is exhausted.

# 5.5.3 Other Run-Time Options

Here we give description about other run-time options that we use in running our verifier:

#### -A

Suppresses the reporting of basic assertion violations. We use this when we want to get a different kind of errors, such as non-progress or acceptance cycles.

#### −a

Enables detection of acceptance cycles. This option is disabled when the verifier is compiled with the directive -DNP.

#### -E

Suppresses the reporting of invalid end-state violations.

#### • −n

Disables the default reporting of all unreached states at the end of a verification run.

# 5.6 Various Verification Attempts

The main disadvantage with model checking is the state explosion problem. The Fiasco IPC model also faces this problem, which blows up the memory use during verification run. Due to this fact, at first, we do the verification by setting many cases individually for each verification attempts. During these verifications, we found errors that lead us to improve the model. But memory is still an issue.

In order to keep the nondeterminism of the model, but at the same time reducing memory, we also try to create an auxiliary program written in C, which sets up every possible combination and then run verification for each combination. During this phase, we still meet some problems with the memory use.

After experimenting with many kinds of options for compile-time and run-time, we found two helpful options to reduce the memory, viz. -DSC and -DMA. With these options, we try to set the IPC parameters nondeterministically from SPIN. During this phase, we found many interesting counterexamples which help us to further refine our models.

At this phase, memory is not a problem thanks, to the option -DMA. But still we are concerned about the huge search depth and the stack file produced by the option -DSC. After some consultation on the experts, we try to do the following improvements:

- use the new version GCC, that is gcc-3.4,

- use compile-time option -03 for compiler optimization,

- added compile time option -march=opteron to improve compilation. This option generates instructions for machine specific cpu-type that we use, that is AMD Opteron.

- try running the command:

# spin -A filename

This gives some hints about things that may be redundant for the given properties.

- reexamining the data types, to make sure that we could use smaller domain. For example, changing int to byte or short.

- break the problem up into smaller pieces

- make stronger abstractions

- remove redundancy

- reduce the number of processes

#### 5.6.1 SPIN Version and Hardware Used

All the simulation and verification reported in this master's thesis use a patched SPIN Version 4.2.3 which was released on February 5, 2005. The original SPIN always produces error when producing a big stack file. That is why we use the patched SPIN. The patched SPIN was delivered by Hendrik Tews and it corrects the executions of SPIN when managing big stack files which is bigger than 2GB.

The operating system used is Linux 2.6 with a 32-bit system. The machine on which we perform all the simulation and verification totally has 2048 MB RAM and it has two processors, each with the following description:

• vendor\_id : AuthenticAMD

• model name: AMD Opteron(tm) Processor 248

• cpu MHz : 2192.904

• cache size: 1024 KB

### 5.6.2 Default Verification

SPIN default verification is to check for violations of safety properties. The safety properties which are checked by SPIN are as follows:

- assertion violations:

- unreachable code,

- unintended end states:

We always use the compile-time option -DSAFETY for this default verification. We report the verification result of the model for two and three threads as follows:

## 1. two threads:

The following commands depict the generation, compilation, and run of the verifier:

From the log file log\_ver\_2\_thread, we know that the verification succeeds, with some information as follows:

- verification time (user and system time): 14 hours 12 minutes,

- total memory used: 1,383.323 MB

#### 2. three threads:

Due to lack of memory, we have to use the compile-time option -DBITSTATE and the run-time option -w27 for the verification of the model with three threads. This time the model is saved in another file sys\_ipc\_3\_thread. The commands are:

The verification succeeds, with some information as follows:

- verification time (user and system time): 2 hours 4 minutes,

- total memory used: 1,611.043 MB,

- hash factor: 2.36853

The run-time reduces greatly, but this bitstate method does not guarantee an exhaustive coverage. Especially since the hash factor (the maximum number of states divided by the actual number of states) is only 2.36853, which is too small. The reliable minimum hash factor is 100, which means a coverage of 100%.

## 5.6.3 Verification of Proposed Properties

In this subsection, we specify some properties of Fiasco IPC using never claims. Some claims are hand-written because it simply specified invariant property. Some others are generated from LTL formulae by SPIN. All these properties are proposed for the model with two thread processes instantiated. This is done by setting the number N to two.

1. The state flags "busy" and "send\_in\_progress" are never active at the same time for the same thread.

This invariant property is saved in a file called busy\_and\_send\_in\_progress.ltl below:

The following commands depict the generation, compilation, and run of the verifier for the above property:

From the log file log\_ver\_busy\_sip, we know that the verification succeeds, with some information as follows:

- verification time (user and system time): 8 hours 15 minutes,

- total memory used: 1,458.778 MB,

- we could add the compile-time option <code>-DSAFETY</code> to get more efficient verification

- 2. The state flag "polling" is only ever active when "send\_in\_progress" is also active.

This is another invariant property as the previous one we have. It is saved in a file called polling\_and\_sip.ltl as follows:

Now we use the compile-time option -DSAFETY to do the verification as follows:

The verification succeeds and the log file log\_ver\_polling\_sip gives the following:

- verification time (user and system time): 6 hours 18 minutes

- total memory used: 1,458.484 MB

- 3. The state flag "busy" is only ever active when "receiving" is also active. This invariant property is saved in a file called busy\_receiving.1t1:

The verification is done as follows:

The verification succeeds and the log file log\_ver\_busy\_receiving gives the following:

- verification time (user and system time): 6 hours 16 minutes

- memory: 1,458.484 MB

- 4. The value of each element of array **snd\_partner** must always be greater than or equal zero.

This is also another invariant property which is specified as follows:

```

#define p (snd_partner[0] < 0)

#define q (snd_partner[1] < 0)

never {

do

:: (p || q) -> break

:: else

od

}

```

The options used for the generation, compilation and run of the verifier are the same as we used in the second verification. The verification succeeds with following result:

- verification time (user and system time): 6 hours 9 minutes

- memory: 1,458.727 MB

- 5. The value of each element of rcv\_partner must always be greater than or equal -1. This is also another invariant property which is specified as follows:

```

#define p (rcv_partner[0] < -1)

#define q (rcv_partner[1] < -1)

never {

do

:: (p || q) -> break

:: else

od

}

```