Universität Karlsruhe (TH)

Institut für

Betriebs- und Dialogsysteme

Professor Dr. Alfred Schmidt

## Design and implementation of the Recursive Virtual Address Space Model for Small Scale Multiprocessor Systems

Marcus Völp

Diplomarbeit

Verantwortlicher Betreuer: Dr. Kevin Ephinstone

Betreuender Mitarbeiter: Volkmar Uhlig

September 2002

| Hiermit | erkläre | ich, die vorli | egende Arbeit  | selbständig  | verfaßt | und keine |

|---------|---------|----------------|----------------|--------------|---------|-----------|

| anderen | als die | angegebenen    | Literaturhilfs | mittel verwe | ndet zu | haben.    |

I declare to have written this thesis independently and that no unmentioned literature has been used.

Karlruhe, den 11. September 2002

Marcus Völp

# Contents

| 1                    | Intr | oducti                                    | on                                                         | 17 |  |

|----------------------|------|-------------------------------------------|------------------------------------------------------------|----|--|

|                      | 1.1  | Propo                                     | sed Solutions                                              | 18 |  |

|                      | 1.2  | Outlin                                    | ne                                                         | 18 |  |

| 2                    | Bac  | kgrour                                    | $_{ m 1d}$                                                 | 19 |  |

|                      | 2.1  | Mecha                                     | unisms for Page Based Virtual Memory                       | 19 |  |

|                      |      | 2.1.1                                     | Terminology                                                | 19 |  |

|                      |      | 2.1.2                                     | Linear Page-Tables                                         | 20 |  |

|                      |      | 2.1.3                                     | Multi-Level Page-Tables                                    | 20 |  |

|                      |      | 2.1.4                                     | Guarded Page Tables                                        | 21 |  |

|                      |      | 2.1.5                                     | Inverted Page-Tables                                       | 23 |  |

|                      | 2.2  | Transl                                    | ation Lookaside Buffer                                     | 23 |  |

|                      | 2.3  | Small                                     | Scale Multiprocessors                                      | 24 |  |

|                      | 2.4  | 2.4 Recursive Virtual Address Space Model |                                                            |    |  |

|                      |      | 2.4.1                                     | Map                                                        | 26 |  |

|                      |      | 2.4.2                                     | Grant                                                      | 27 |  |

|                      |      | 2.4.3                                     | Unmap                                                      | 27 |  |

|                      |      | 2.4.4                                     | Overmap and Fast Overmap                                   | 29 |  |

|                      |      | 2.4.5                                     | Page Reference Information Retrieval                       | 30 |  |

|                      |      | 2.4.6                                     | Multiple Hardware Page-Size Support                        | 31 |  |

|                      |      | 2.4.7                                     | Fundamental Consistency Requirements                       | 33 |  |

| 2.5 Mapping Database |      | Mappi                                     | ing Database                                               | 34 |  |

|                      |      | 2.5.1                                     | Structure of the Mapping Database                          | 35 |  |

|                      |      | 2.5.2                                     | Requirements and Constraints                               | 36 |  |

|                      | 2.6  | Unbou                                     | inded Priority Inversion                                   | 39 |  |

|                      |      | 2.6.1                                     | Definition                                                 | 39 |  |

|                      |      | 2.6.2                                     | Unbounded Priority Inversion in Address Space Construction | 39 |  |

6 CONTENTS

|   |                                     | 2.6.3  | Unbounded Priority Inversion of Preorder Unmap                  | 40         |

|---|-------------------------------------|--------|-----------------------------------------------------------------|------------|

|   |                                     | 2.6.4  | Generalization                                                  | 42         |

|   |                                     | 2.6.5  | Helping                                                         | 43         |

|   | 2.7                                 | Summ   | nary                                                            | 45         |

| 3 | Fun                                 | damer  | ntals and Related work                                          | 47         |

|   | 3.1                                 | Existi | ng Implementations of the Recursive Virtual Address Space Model | 47         |

|   |                                     | 3.1.1  | The $\mu$ -kernel Approach                                      | 47         |

|   |                                     | 3.1.2  | L4 $\mu$ -kernel                                                | 48         |

|   |                                     | 3.1.3  | Implementations of the Recursive Virtual Address Space Model .  | 48         |

|   | 3.2                                 | Synch  | ronization                                                      | 49         |

|   |                                     | 3.2.1  | Overview of Synchronization Techniques                          | 50         |

|   |                                     | 3.2.2  | Locking policies                                                | 51         |

|   |                                     | 3.2.3  | Uniprocessor Synchronization                                    | 51         |

|   |                                     | 3.2.4  | Scheduler-Conscious Synchronization                             | 52         |

|   | 3.3                                 | Summ   | nary                                                            | 52         |

| 4 | $\mathbf{M}\mathbf{a}_{\mathbf{i}}$ | pping- | Database Design                                                 | 53         |

|   | 4.1                                 | Марр   | ing-Tree Representation                                         | 54         |

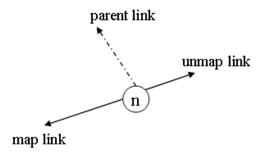

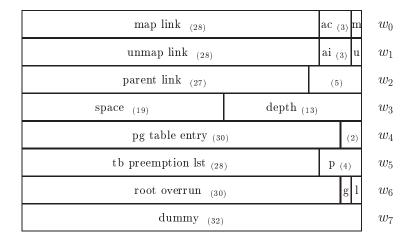

|   |                                     | 4.1.1  | Mapping Node                                                    | 54         |

|   |                                     | 4.1.2  | Requirements                                                    | 54         |

|   |                                     | 4.1.3  | Representations                                                 | 58         |

|   |                                     | 4.1.4  | Summary Tree Representation                                     | 70         |

|   | 4.2                                 | Concu  | irrency and Consistency                                         | 71         |

|   |                                     | 4.2.1  | Granularity                                                     | 72         |

|   |                                     | 4.2.2  | Synchronization Techniques                                      | <b>7</b> 4 |

|   |                                     | 4.2.3  | PTE Lock                                                        | 77         |

|   | 4.3                                 | Preem  | nptability and Progress                                         | 78         |

|   |                                     | 4.3.1  | Restart of Unmap: Problem Analysis                              | 78         |

|   |                                     | 4.3.2  | Preempted-Thread List                                           | 79         |

|   |                                     | 4.3.3  | Token-Based Preempted-Thread List                               | 81         |

|   |                                     | 4.3.4  | Summary                                                         | 83         |

|   | 4.4                                 | Multi  | ple Page-Size Support                                           | 85         |

|   |                                     | 4.4.1  | Split Mapping                                                   | 85         |

|   |                                     | 4.4.2  | Partial Unmap                                                   | 85         |

|   |                                     | 4.4.3  | Root Array Structure                                            | 87         |

|   |                                     | 4.4.4  | Frame Locks Revisited                                           | 88         |

CONTENTS 7

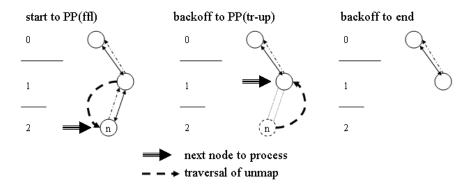

|              |     | 4.4.5                     | Restart-Point Tracking               | 92  |  |  |

|--------------|-----|---------------------------|--------------------------------------|-----|--|--|

|              |     | 4.4.6                     | Space Requirements                   | 93  |  |  |

|              | 4.5 | 5 Summary of the Design   |                                      |     |  |  |

| 5            | Exp | erime                     | ntal Results and Analysis            | 97  |  |  |

|              | 5.1 | Exper                     | imental Setup                        | 97  |  |  |

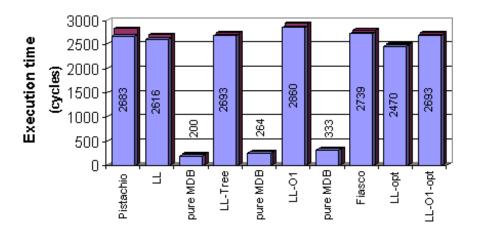

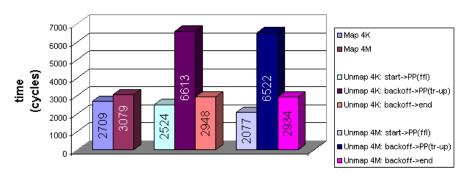

|              | 5.2 | Perfor                    | mance of the Address Space Modifiers | 98  |  |  |

|              |     | 5.2.1                     | Map Performance Comparisson          | 98  |  |  |

|              |     | 5.2.2                     | Unmap Performance Comparisson        | 100 |  |  |

|              | 5.3 | Interru                   | ıpt Latency                          | 102 |  |  |

|              | 5.4 | Analys                    | sis                                  | 103 |  |  |

| 6            | Con | onclusion and Future work |                                      |     |  |  |

|              | 6.1 | Conclu                    | ısion                                | 105 |  |  |

|              |     | 6.1.1                     | Approach                             | 106 |  |  |

|              |     | 6.1.2                     | Summary of Results and Conclusions   | 106 |  |  |

|              | 6.2 | Future                    | e Work                               | 108 |  |  |

| $\mathbf{A}$ | Dat | a Stru                    | ctures                               | 111 |  |  |

|              | A.1 | Mapno                     | ode                                  | 111 |  |  |

|              | A.2 | Preem                     | ption token                          | 114 |  |  |

|              | A.3 | Root o                    | overrun token                        | 114 |  |  |

|              | A.4 | Multip                    | ole pagesize support                 | 115 |  |  |

|              |     | _                         | Dual node                            |     |  |  |

|              |     | A.4.2                     | Rootnode                             |     |  |  |

|              |     | A.4.3                     | Mid-Rootnode                         | 116 |  |  |

8 CONTENTS

# List of Figures

| 2.1  | Linear Page-Table                                            |

|------|--------------------------------------------------------------|

| 2.2  | Multi-Level Page-Table                                       |

| 2.3  | Guarded page-table                                           |

| 2.4  | Inverted Page-Table                                          |

| 2.5  | Symmetric Multi-Processor Hardware                           |

| 2.6  | Mapping of a Page                                            |

| 2.7  | Granting of a Page                                           |

| 2.8  | Unmapping a Page                                             |

| 2.9  | Overmapping a Page                                           |

| 2.10 | Split Mapping                                                |

| 2.11 | United Mapping                                               |

| 2.12 | Partial Unmap                                                |

| 2.13 | Pinning                                                      |

| 2.14 | Modification of Map on the Mapping Database                  |

| 2.15 | Modification of Grant on the Mapping Database                |

| 2.16 | Modification of Unmap on the Mapping Database                |

| 2.17 | Unbound priority inversion of Concurrent Pre-order Unmaps 41 |

| 2.18 | Unbounded Priority Inversion in other Traversal Methods      |

| 3.1  | Left child - Both siblings                                   |

| 4.1  | Page Reference Information                                   |

| 4.2  | Mapping-Database Representation: LL                          |

| 4.3  | Pointers of $LL$                                             |

| 4.4  | Mapping-Node Insertion in LL                                 |

| 4.5  | Mapping-Node Deletion in LL                                  |

| 4.6  | Mapping-Node Reallocation in LL                              |

| 4.7  | Tree-Oriented Representation                                 |

10 LIST OF FIGURES

| 4.8  | Operation-Oriented Representation                                  |

|------|--------------------------------------------------------------------|

| 4.9  | Mapping-Database-Representation: LL-Tree                           |

| 4.10 | Pointers of LL-Tree                                                |

| 4.11 | Child-Link Update in LL-Tree                                       |

| 4.12 | Mapping-Node Reallocation in LL-Tree: Child-Link Update 66         |

| 4.13 | Mapping-Node Reallocation in LL-Tree: Sibling-Link Update 67       |

| 4.14 | First-Child-List shares Left-Most-Leaf                             |

| 4.15 | Mapping-Database Representation: LL-O1                             |

| 4.16 | Pointers of LL-O1                                                  |

| 4.17 | Anomaly in LL-O1 Representation                                    |

| 4.18 | Mapping-Node Reallocation in LL-O1                                 |

| 4.19 | Two Phase Locking Protocol for LL                                  |

| 4.20 | Page-Table-Entry Lock                                              |

| 4.21 | Restart-Point of Preempted Unmap                                   |

| 4.22 | Preempted Thread List                                              |

| 4.23 | Starvation in Thread List                                          |

| 4.24 | Token-Based Preempted-Thread List                                  |

| 4.25 | Partial Unmap with Page Split-Up                                   |

| 4.26 | Separation of Multiple Page-Sizes with Root Arrays                 |

| 4.27 | Tree Representations for Multiple Page-Sizes: LL                   |

| 4.28 | Tree Representations for Multiple Page-Sizes: LL-Tree              |

| 4.29 | Tree Representations for Multiple Page-Sizes: LL-O1                |

| 4.30 | Traversal of Multi Page-Size Mapping-Database                      |

| - 1  |                                                                    |

| 5.1  | Performance of the Map Operation                                   |

| 5.2  | Performance of Wide Unmap                                          |

| 5.3  | Performance of Deep Unmap                                          |

| 5.4  | Preemption Points of Unmap in the Interrupt-Latency Experiment 102 |

| 5.5  | Interrupt Latency                                                  |

# List of Tables

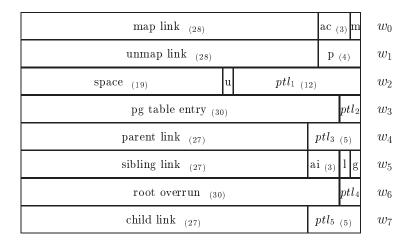

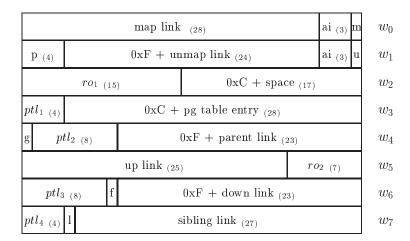

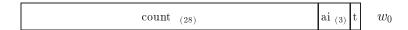

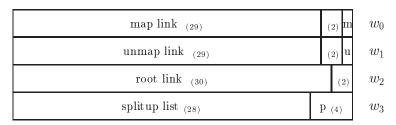

| 4.1 | Content of Mapping Node                | 54 |

|-----|----------------------------------------|----|

| 4.2 | Summary of Representations             | 71 |

| 4.3 | Payload Information of a Mapping Nodes | 72 |

| 4.4 | Space Requirements for Mapping Nodes   | 94 |

## Abstract

Standard virtual memory management (VMM) and protection policies are often not suitable to serve the requirements of special applications such as database management and multi-media. Two approaches have been proposed to support the differing demands of those kind of applications:

- extension of the standard policies with application specific policies, and

- externalization of virtual memory management and protection policies to application specific managers.

An externalization of VMM policies to user level managers makes it possible to select those policies that best serve those requirements. In addition to that, externalization reduces the complexity of inside kernel memory management. The Recursive Virtual Address Space Model is such an approach of externalization.

Undesired behavior and unnecessary complex or slow behavior of existing implementations of this model, however, limit its applicability. Such behavior includes:

- long interrupt latencies, and

- unbounded priority inversion.

The first is caused by non-preemptively executing those operations modifying address spaces as it is done in some existing implementations. Other implementations allow for those operations to be preempted. This avoids long interrupt latencies, but those implementations are prone to unbounded priority inversion. To avoid this unbounded priority inversion, those implementations apply complex timeslice donation and "helping-schemes" [HH01]. In Section 2.6.5, we will point out that those "helping-schemes" imply system behavior that cannot be tolerated in all systems. In particular in small scale multiprocessor systems, this may lead to a behavior that is not desirable in all systems. A frequent migration of threads that get "helped" is an example of such a behavior. We aim to avoid "helping" in our solution.

This thesis investigates the problem of unbounded priority inversion in preemptable implementations of the *Recursive Virtual Address Space Model*. We propose new methods to control concurrent address space construction, that

- do not lead to long interrupt latencies,

- do not lead to unbounded priority inversion,

- do not lead to starvation, and

- do not require helping.

In particular, we propose:

- preemptable post-order traversal,

- roll forward combined with scheduler-conscious locking, and

- efficient restart-point tracking

to achieve those objectives.

In this thesis we describe and evaluate those techniques in the implementation of the  $Recursive\ Virtual\ Address\ Space\ Model.$  We show that a comparable performance to non-preemptive implementations can be achieved for address space construction. The costs of revoking memory from address spaces, however, show an increase by 12.2% compared to the non-preemptive implementations.

## Acknowledgment

At first I would like to thank my wife Sofia for putting up with all the late nights. I like to thank her for her encouragement and especially for her constant support.

I would like to thank her parents and of course my parents for giving me a place to relax and to feel home. Furthermore, I have to thank for their constant support.

I would like to thank my supervisor Volkmar Uhlig for his guidance and advice. Also I have to thank Dr. Kevin Elphinstone, Gerd Lieflaender and Prof. Dr. Alfred Schmidt who made it possible that I could write this thesis and supported me a lot in doing so.

Finally, I would like to thank the many people that supported me during my studies so far. From them I have to mention in particular the people of the System Architecture Group at the Universität Karlsruhe. Thanks for your support and for the possibility to discuss the many problems that came to my mind during the development of this thesis.

Thanks a lot.

## Chapter 1

## Introduction

Virtual memory management (VMM) is an integral part of operating systems for interactive or partially untrusted applications. In general, this part of the operating system tends to be rather complex. Nevertheless, standard virtual memory policies are often not suitable to serve the requirements of special tasks and applications such as database management (DBMS) [Sto81], garbage collection [AL91] and multi-media applications [Map92].

To fulfill those requirements, two approaches have been proposed:

- extension of the VMM-system with application specific policies [BCE<sup>+</sup>94,BSP<sup>+</sup>95, EGM<sup>+</sup>94, CD94, EGK95], and

- externalization of virtual memory management to application specific managers [ABB<sup>+</sup>86, RTY<sup>+</sup>87, HC92, KN93, Lie95, Han99].

In micro-kernels, the second approach is applied.

The Recursive Virtual Address Space Model [Lie95], proposed for the L4  $\mu$ -kernel, is such an approach of externalization. The model provides mechanisms that makes it possible to implement arbitrary virtual memory management and protection policies at user level. Each subsystem can implement those policies, fitting best to the requirements of its applications. It can implement those policies independent of other subsystems. Furthermore, it can use the functionalities provided by other subsystems. This allows to construct systems in a hierarchical manner.

The applicability of the *Recursive Virtual Address Space Model*, however, is currently limited. This is because existing implementations of this model show undesired behaviors or unnecessary complex or slow behaviors such as:

- long interrupt latencies,

- unbounded priority inversion, or

• complex timeslice donation or "helping" schemes.

This thesis investigates techniques and mechanisms to avoid those undesired behaviors. We show that unbounded priority inversion is not inherent to the Recursive Virtual Address Space Model. Instead, we show that it can be avoided by design without having to delay interrupt handling for long times and without having to implement complex timeslice donation or "helping-schemes".

The objective of this thesis is to offer solutions for uniprocessor as well as for small scale multiprocessor systems.

## 1.1 Proposed Solutions

We propose:

- preemption of long running operations to avoid long interrupt latencies,

- post order traversal to avoid unbounded priority inversion,

- roll forward combined with scheduler-conscious-locking to ensure consistency, and

- restart-point tracking to guarantee forward progress and to avoid starvation.

To efficiently track the restart point of preempted operations we introduce a new technique: the token-based preempted-thread list.

The proposed solutions are evaluated using an implementation in the L4Ka Pistachio  $\mu$ -kernel.

### 1.2 Outline

Chapter 2 introduces the Recursive Virtual Address Space Model. Furthermore, it explores the problem of unbounded priority inversion in existing implementations. Chapter 3 describes fundamentals applied in this thesis and work, the approach presented in this thesis relates to. Chapter 4 presents the proposed solutions. At first, we focus on solutions for a single hardware page-size. After that, we extend our approach to support multiple hardware page-sizes. Chapter 5 discusses and analyses the experiments. In Chapter 6 we draw conclusions. Furthermore, an outline of future work is given.

## Chapter 2

# Background

This chapter surveys hard- and software mechanisms to implement page-based virtual memory. It introduces the Recursive Virtual Address Space Model and the *mapping database*, a data structure used to implement this model. In addition to that, this chapter surveys small scale multiprocessor systems.

We analyze the problem of unbounded priority inversion and discuss techniques that have been proposed to avoid this problem. One such technique is "helping".

This chapter ends with identifying the issues and constraints of an implementation of the Recursive Virtual Address Space Model.

## 2.1 Mechanisms for Page Based Virtual Memory

### 2.1.1 Terminology

**Page-Frame** A page-frame (or frame) is a contiguous region of physical memory. It is described by its physical base address and its size, whereby the size is a power of 2 and the base address is aligned to this size.

**Page** A page  $p_v$  is a contiguous region of virtual memory of size s starting from a virtual base address v. s is a power of 2 and one of the hardware page-sizes supported by the processor. v is aligned to the size s.

A virtual address-space consists of a mapping that associates each virtual page to a physical page-frame or marks it "non-present". Additionally, the permitted access to present pages is stored with the mapping.

Page-tables implement this mapping. They are used to translate the virtual addresses of memory accesses to a page into the physical addresses within a frame. Translation lookaside buffer (TLB) hardware caches the result of the most recent translations. The

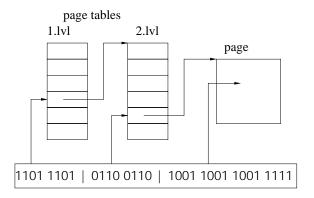

Figure 2.1: Address translation with a linear page-table

purpose of the TLB is to speed up subsequent memory accesses to those pages. If no such translation exists in the TLB, i.e. on a TLB miss, the page table is walked by hardware or by software and an entry for the result of this translation is inserted into the TLB.

Several page-table structures have been proposed [JM98, Szm99, LE96, Lie94]. This section gives an overview of the most common.

### 2.1.2 Linear Page-Tables

A linear page-table (Figure 2.1) is an array of page-table entries (PTEs). The virtual address v to translate is subdivided into two parts. The part with the most significant bits is used to index into the page-table to retrieve a page-table entry. The PTE points to a page frame, or it marks the page as "non-present". In the first case, the remaining part of the virtual address – s bits, whereby s is the page size – is used as an offset into the frame. The second case results in a page-fault, a signal to the operating system, that a "non-present" page has been accessed.

Linear page-tables store a page-table entry for all virtual pages of an address space. Often, several of those page-table entries mark the page as "non-present".

### 2.1.3 Multi-Level Page-Tables

Multi-level page-tables have been proposed to reduce the space required to store pagetable entries that mark pages "non-present" in non-populated regions of the address

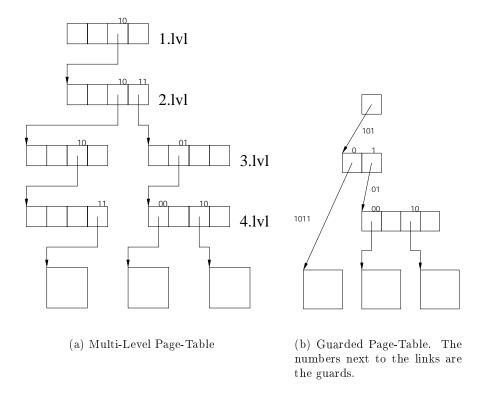

Figure 2.2: Address translation with a multi-level page-table.

space. The multi-level page-table allows for a hierarchy of page-tables to be allocated in multiple levels. Figure 2.2 shows the translation of a virtual address with a multi-level page-table. For the translation of a virtual address v, the multi-level page-tables subdivides v into several parts. The translation starts with the part containing the most significant bits. Those bits are used to index into the page table at the first level. The page-table entry found is in one of three possible states:

page found: A valid translation of the page is found. The page-table entry contains the physical address of the page-frame and information on the permitted access to it. The bits of the remaining parts offset into the page frame.

**non-present:** The translation stops without translating to a page-frame.

page-table: The page-table entry points to a page table at the next level. The bits of the next part are used to index into this page table to find a page-table entry to continue the translation with.

Compared to those parts of the virtual address, the lower-level page-tables are indexed in with, the parts that are used to index into higher-level page-tables contain less significant bits of the address. Therefore, a page-table entry in a lower level stands for a larger region of the virtual address-space than one in a higher level. If no page is mapped in this region, i.e. all page-table entries of higher-level page-tables would mark the pages as "non-present", the lower-level page-table entry can mark the entire region as "non-present". In this case, a higher-level page-table is not required. The space this page-table would require is saved. This, however, comes up with the necessity to walk multiple levels of page tables to complete the translation upon a TLB miss.

## 2.1.4 Guarded Page Tables

To decrease both, the lookup performance of deep multi-level page-tables and the space required for those page-tables in large, sparsely populated address spaces, the guarded

Figure 2.3: Address translation with guarded page-table.

page-table (GPT) [Elp99,Lie94] has been proposed. Furthermore, guarded page-tables allow for efficiently mixing multiple different page sizes.

In sparsely populated address spaces, the page tables of a multi-level page-table often contain only a few page-table entries that point to a page or a page-table at the next level. Guarded page-tables have the ability to compress the translation path through those, sparsely populated regions. Instead of allocating a level of page-table for each fixed sized part of the virtual address, as multi-level page-tables do, the guarded page-table makes it possible to subdivide the virtual address more flexible. Parts containing bits shared by all addresses in a certain region can be split off entirely from the translation. Those bits are stored in the guards that directly shortcut to the next level of page tables or to a page. Only with the differing bits, a page-table is indexed. Guarded page-tables allow for differently large page-tables.

We illustrate the benefits of guarded page-tables in the following example: the translating of the following three 10-bit addresses. Figure 2.3(a) shows the translation of

the virtual addresses  $v_1, v_2, v_3$

$v_1 = 1011010000$   $v_2 = 1011011000$  $v_3 = 1010101100$

by a multi-level page-table, assuming 4 entry page-tables and 4 byte pages. In the first and third level of the multi-level page-table and for  $v_3$  in the fourth level as well, only one page-table entry is used, the rest is marked "not-present".

In our example (Figure 2.3(b)) $v_1$  and  $v_2$  have a common 6-bit prefix,  $v_1$ ,  $v_2$  and  $v_3$  a common 3-bit prefix. With these common prefixes, the guarded page table shortcuts through the sparsely populated page tables, thereby compressing the translation path. The guarded page-table saves both memory capacity and translation steps in sparsely populated address spaces. Furthermore, it allows for efficiently storing several different hardware page-sizes.

Level- and path-compressed trees (LPC) [Szm99] compress the translation path as GPTs do. Furthermore, level-compression flattens densely populated regions of the address space by replacing complete subtrees with a single page-table. Level compression reduces the depth of the page-table tree in densely populated areas, path compression in sparsely populated areas.

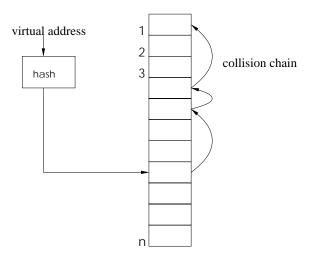

## 2.1.5 Inverted Page-Tables

Instead of storing one page-table entry per virtual page, the inverted page-table (IPT) has one page-table entry per page frame. The page table is called *inverted* because the table is indexed with the physical frame-address rather than the virtual address of the page. Instead, the inverted page-table translates the virtual address by hashing with it into the IPT to retrieve the page-table entry.

Inverted page-tables combine a fast lookup with little space required, provided the hash is collision free. However, in the presence of hash collisions, a collision chain has to be searched for the appropriate page-table entry, or the entire page table has to be rehashed.

## 2.2 Translation Lookaside Buffer

A translation lookaside buffer (TLB) caches the most recent translations from virtual to physical addresses. The entries in a TLB are inserted either by hardware or by software. In the first case, the translation is retrieved by a hardware page-table lookup. In the second, a software handler is responsible to insert the entry.

## inverted page table

Figure 2.4: Inverted Page-Table

After modifying a translation in the page tables to point to a different frame or when reducing the access rights that are stored with the translation, the corresponding TLB entries need to be invalidated to make the changes to become effective.

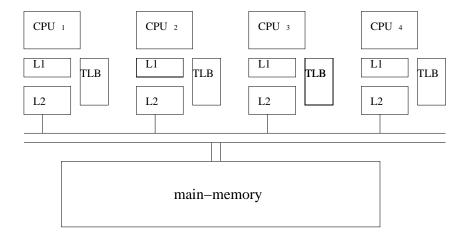

## 2.3 Small Scale Multiprocessors

This section briefly surveys small scale or symmetric multiprocessors. As can be seen in Figure 2.5, symmetric multiprocessor hardware consist of several processors (CPUs) that are connected via a bus or a crossbar to the main memory module. Memory accesses are uniform, i.e. they take equally long for each processor.

Communication between the processors is via the main-memory module, however, a facility exists to deliver an interrupt signal to other processors. This signal is called inter-processor or cross-processor interrupt. Upon receiving this interrupt, the processor executes a handler installed by the operating system.

Each processor has a set of local caches. Those caches are kept consistent by a cache coherency protocol. This protocol ensures, that always up to date values are read from the cache. Modifications to data cached by another processor are written back to main memory, before a read of another processor requests the modified data.

In addition to processor local caches, symmetric multiprocessor systems as well have processor local TLB hardware. However, those TLBs are commonly not kept in a

Figure 2.5: Symmetric Multi-Processor Hardware

consistent state. TLB consistency has to be established by the operating system. The process of invalidating non-local TLB entries is called "TLB-shootdown". Teller [Tel91] and Rosenburg et. al [Ros89] proposed algorithms to shootdown TLB entries.

The synchronization of threads on different processors is supported by symmetric multiprocessor hardware with a series of atomic or memory ordering instructions.

Typically load-store based multiprocessor architectures support an instruction that stores a link between the processor and the memory location it reads (load-linked). A conditional store operation tests whether in between the time from loading the memory to storing it, another processor modified the data in memory. If this is the case, the store fails. Otherwise, the memory location is updated atomically and the store-conditional operation succeeds.

Other processors typically offer a set of atomic read-modify-write instructions such as: test-and-set, fetch-and-add, swap and compare-and-swap.

With those operations, more complex synchronization primitives can be implemented in software.

## 2.4 Recursive Virtual Address Space Model

Traditionally, a virtual address-space is manipulated by modifying the virtual to physical address translations in the page tables. The kernel, however, has to be the only entity in the system, that has direct access to this data structure. Otherwise, protection policies could not be enforced.

On the other hand, implementing virtual memory management and protection policies inside the kernel restricts the system to only a few policies. Those are potentially not optimally suited for any kind of subsystem or application envisaged to run on top of the kernel

An implementation of virtual memory management and protection policies at user level, makes it possible to implement best suited policies for all subsystems or applications. Direct manipulation of the page tables by user-level memory-managers, however, cannot be allowed. Instead, we have to demand for different solutions to manipulate virtual address spaces outside the kernel.

To securely manipulate virtual address spaces at user level, Liedtke has proposed a recursive construction-scheme of virtual address spaces: the Recursive Virtual Address Space Model.

The key idea of this model is to construct an address space recursively by providing it access to the memory of the constructing address space. The important restriction is, that access may only be given to those page frames, the constructing address space itself has access to. To achieve this, virtual pages are used as parameters for those operations modifying address spaces. The frames operated on, are retrieved by looking up the page tables of the source address-space.

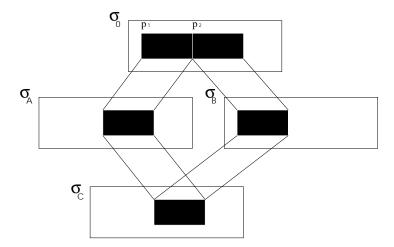

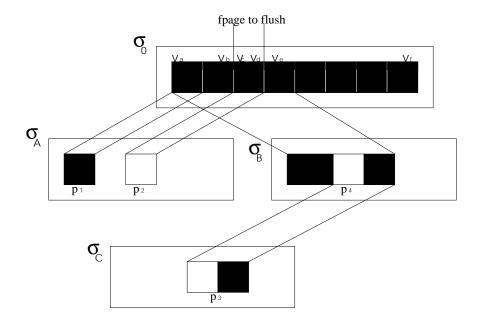

The recursion is initialized by constructing an initial address space called  $\sigma_0$ . This address space has an idempotent mapping to all physical memory, except to those required by the kernel.

The Recursive Virtual Address Space Model allows to construct and manipulate address spaces with the following three operations: map, grant and unmap. We refer to those operations as address space modifiers.

#### 2.4.1 Map

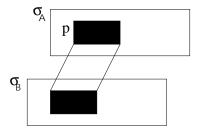

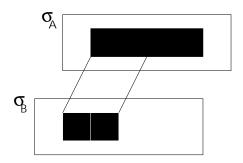

Any thread of an address space – the mapper – can *map* any of its pages to another address space, provided that a thread in the target address space – the recipient – agrees. Afterwards, the mapped page frames are accessible in both address spaces (see Figure 2.6).

It is important to note, that access rights cannot be elevated. The page is mapped into the target address space with the minimum of the rights specified by the mapper and the rights the mapper possesses itself.

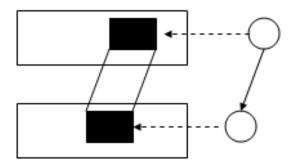

Figure 2.6: A page p is mapped from address space  $\sigma_A$  to  $\sigma_B$ . Afterwards, p is accessible in both address spaces.

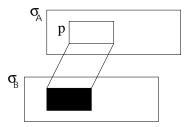

Figure 2.7: A page p is granted from address space  $\sigma_A$  to  $\sigma_B$ . Afterwards, p is accessible in  $\sigma_B$ , but no longer in  $\sigma_A$

#### 2.4.2 Grant

As with map, any thread of an address space can grant any of its pages to another address space, provided an agreement of the recipient. The granted pages are removed from the granter's address space and included into the target address space (see Figure 2.7).

Again the pages are made accessible in the target address space with the minimum of the access rights specified and the access rights the *granter* had to the page, prior to removal.

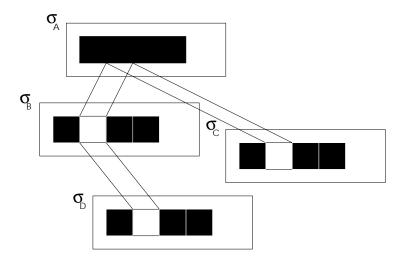

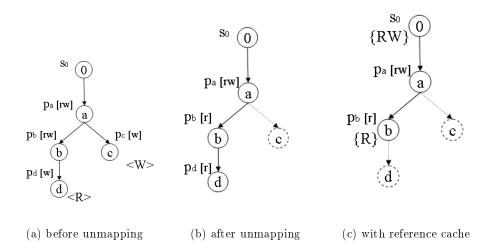

## 2.4.3 Unmap

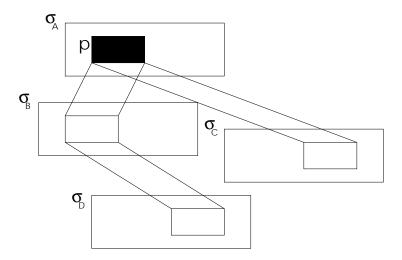

Any thread of an address space can unmap any of its pages. Afterwards, the access rights, specified in the unmap operation, are revoked from all address spaces that directly or indirectly received the page from this thread or from any thread in the same address space (Figure 2.8). A revocation of all access rights from a page results in removing that page completely  $^1$ .

<sup>&</sup>lt;sup>1</sup>Note, the *unmap* operation guarantees, that the access rights are revoked by the time, the *unmap* operation returns. It is up to the implementation, when exactly the rights are revoked during the unmap operation, as long as it does not return from the *unmap* operation as long as a derived mapping

Figure 2.8: A page p is unmapped from all address spaces that directly  $(\sigma_B, \sigma_C)$  or indirectly  $(\sigma_D)$  received it from  $\sigma_A$ . Afterwards, p is no longer accessible in  $\sigma_B$ ,  $\sigma_C$  and  $\sigma_D$ .

Unmap does not require explicit agreement of the address spaces the pages are revoked from. Nevertheless, the operation is safe because it is restricted only to owned pages. Upon accepting a page mapped or granted, the receiving thread, implicitly agrees on a potential revocation.

With a special case of *unmap*, a thread can revoke access from the pages in it's address space as well. We call this special case *inclusive unmap*.

The number of pages to be revoked with unmap cannot be controlled by the thread executing the unmap operation. It can control the number of direct mappings – those pages are mapped by threads in it's address space. However, it has no control on the number of indirect mappings because with receiving a page, the receiver gets as well the right to go on mapping it  $^2$ .

exists that still has an access right that was revoked. By the time *unmap* returns, no derived mapping has an access right that was revoked by the *unmap operation*.

<sup>&</sup>lt;sup>2</sup>The Recursive Virtual Address Space Model does not limit the number of derived mappings. One way to extend the model is to add a quota to each page mapped. In the following we briefly present this solution. However, a complete discussion of appropriate mechanisms to limit the number of derived mappings is out of the scope of this thesis.

The number of derived mappings can be limited by adding a quota to each page mapped. This quota limits the number of mappings that can be directly or indirectly derived from this page. As with access rights, the quota of the owned page limits the number of direct mappings and the quotas handed out. More precisely, the sum of all quotas mapped plus the number of derived mappings has to be less or equal to the quota received with the page. Restricting allowed values for the quota to 0 and infinity

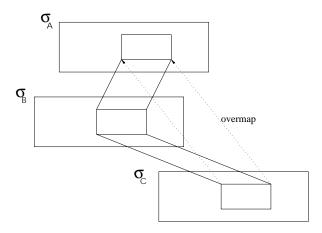

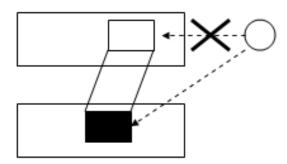

Figure 2.9: The conflicting page p is implicitly unmapped before it is overmapped. This leads to p being completely removed in the address spaces  $\sigma_A$ ,  $\sigma_B$  and  $\sigma_C$ . The map operation of  $\sigma_C$  results in a "no-op"

The unmap operation has to revoke access from all address spaces that directly or indirectly received the mapping from a thread in the address space of the unmapping thread. This number can be large, leading to a long running unmap operation, and the unmapping thread has no way to limit this number. When executing this operation non-preemptively, no other thread on this processor can preempt the unmap operation. Because this includes those threads participated in interrupt handling, interrupt latency increases by the time it takes to complete this long running unmap. To avoid those long interrupt latencies, we propose a preemptable implementation of unmap.

## 2.4.4 Overmap and Fast Overmap

Prior to the *mapping* or *granting* of a new page we check whether this new page conflicts with pages, already mapped in the mappee's address space. In case of a conflict, we implicitly perform an *inclusive unmap* on the old pages.

This operation is called *overmapping*.

Overmapping avoids cyclic mappings as can be seen in Figure 2.9. The implicit inclusive unmap of the destination area removes the source page that if mapped / granted would close the cycle. The resulting map / grant operation is a no-op.

The *inclusive unmap* on *overmap*, removes the *overmapped* pages from all address spaces that directly or indirectly received it from the mappee. In some situations, however,

results in the quota being a map-right. The issues in implementing this quota-based-scheme are: the bookkeeping and enforcement of the quotas, the choice of appropriate mechanisms to publish the quota to threads in the address space and the choice of how to react when the quota is exceeded. Further work is required to explore this and other mechanisms to limit the number of derived mappings.

this is both unnecessary and too slow. In those cases, a way to increase access to a page, avoiding the *unmap*, is preferable. This special case of *overmapping* is called *fast* overmapping.

## Fast Overmap

Fast overmap<sup>3</sup> is a special case of overmapping, avoiding the implicit unmap. Access rights can be extended if the very same mapping already exists. This is the case, when:

- the mapper maps from the same address space as the existing mapping,

- the mapper maps from the same virtual source address as the existing mapping, and

- the mapper maps to the same virtual destination address as the existing mapping

## 2.4.5 Page Reference Information Retrieval

Some processors, for example Intel's IA32 architecture [Int02], set reference information in the page tables – i.e. they store whether a page has been accessed, modified, or the code in it has been executed. Babaoglu et. al [BJ81] proposes an algorithm simulating reference bits on architectures without hardware implemented reference information.

Direct access to the page tables cannot be given to user-level applications or subsystems, since otherwise, implementing protection would be impossible. Therefore, the relevant question is how to provide the subsystems implementing memory management and protection policies with page reference information.

#### Possible solutions are:

- not providing page reference information

The Recursive Virtual Address Space Model does not provide page reference information. Instead, a similar algorithm as proposed by Babaoglu et. al has to be applied to simulate reference information when mapping the page.

- a system-call reads page reference information

To retrieve the information whether the page was referenced (R), written (W) or

executed (X) by any thread of an address space that directly of indirectly received

the page, a system-call reads and resets the page reference information. Because

of the required traversal of all derived mappings, we combine this system-call with

the unmap operation. Upon traversing the pages, access is to be revoked from,

the unmap operation reads and resets the referenced bits from the page tables

$<sup>^3</sup>Fast$  overmap and Reference information retrieval are extensions to the recursive virtual address space model.

and returns the result. Unmap can be configured to revoke no right. In this case, only the reference information is read and reset.

In a deep hierarchy of subsystems, the first solution may lead to high overhead due to repeatedly unmapping and remapping to implement reference information. The trade-offs of page-reference-information retrieval are the overhead added to unmap, reading the reference bits, compared to the costs of the additional page faults generated.

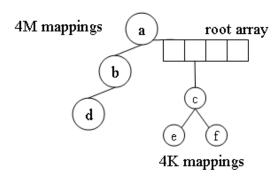

## 2.4.6 Multiple Hardware Page-Size Support

Talluri et. al [TKHP92] investigated the tradeoffs of supporting different hardware page-sizes in the TLB hardware.

Mapping a large memory object with large pages into an address space increases TLB coverage. When accessing the large object, fewer TLB entries have to be assigned to cover the entire memory object. The chance of a TLB hit increases as well, because a larger area is covered by the large page. The likelihood of having a valid translation cached from a previous access increases.

On the other hand, allocating the memory object in physical memory such, that it can be mapped in larger pages is more difficult. A large, free page frame needs to be found. A second counter argument is the write back granularity. The assignment of the memory object with larger pages requires to write the memory object back to secondary storage in a larger granularity, or the lager object has to be split up into a set of smaller pages and reconcatenated later on. Nevertheless, selecting the appropriate hardware page-sizes for the appropriate memory objects and applications may increase overall system performance compared to a system with a single hardware page-size.

#### Flexpages

Hohmuth et. al [HWL96] propose flexpages (fpages) to generalize from a distinct hardware page-size. Similar to a page, a flexpage is specified by its virtual base address and by its size, whereas the size is a power of two and at least the smallest supported hardware page-size. The virtual base address is size aligned.

The Recursive Virtual Address Space Model applies fpages to specify both, the pages to be *mapped*, *granted* or *unmapped*, and the region of the virtual address space to accept mappings in (see the L4-User Manual [AH99] for more details).

The following three special cases can occur for the address space modifiers: map, grant and unmap, when operating on multiple hardware page-sizes: split mappings, united mappings and partial unmap.

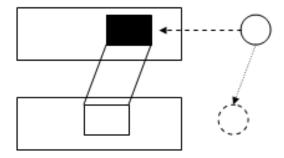

Figure 2.10: Split mapping out of a large page.

Figure 2.11: Adjacent mappings are united into a large page.

### **Split Mappings**

Split mappings (Figure 2.12) can result from a map (or grant) operation if the fpage to be mapped covers only a part of a larger page in the mapper's address space. The fpage is mapped with smaller page sizes into the target address-space, however, those page sizes still have to fit into the fpage.

## **United Mappings**

United mappings (Figure 2.11) unite several adjacent pages in the target address-space into a large page. The pages as well as the according page frames have to be contiguous in memory and must have been mapped with the same access rights.

United mappings are not evaluated in this thesis.

Figure 2.12: Partial unmap of a large page.

## Partial Unmap of Large Pages

Revocation of a part of a large page is called a *partial unmap*. Therefore, the large page is split up into smaller pages.

Alternatively, instead of splitting up the large page into smaller pages, the entire large page could be revoked.

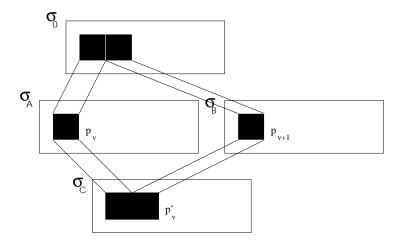

Uniting mappings of pages mapped from different threads requires to split up large pages. Otherwise, one thread can revoke pages mapped by another thread. Guarantees concerning the presence of the page, the second thread associates with the page, can be broken by the first. An example for this is the guarantee, not to revoke the page for a certain time, i.e. to pin the page.

Figure 2.13 illustrates this example: A thread  $\tau_A$  maps a page  $p_v$  and guarantees not to unmap it for a certain period of time  $-p_v$  is pinned.  $\tau_B$  maps  $p_{v+1}$  adjacent to  $p_v$  and both  $p_v$  and  $p_{v+1}$  are united into  $p'_v$ . A revocation of  $p_{v+1}$  resulting in revoking  $p'_v$ , i.e. the page  $p_v$  as well, breaks the pinning guarantee.

## 2.4.7 Fundamental Consistency Requirements

The following consistency requirements have to be met in any implementation of the Recursive Virtual Address Space Model.

**revokability:** The revocation of pages p directly or indirectly mapped into an address space  $\sigma_i$  has to be possible at any time.

Otherwise, the page cannot be revoked, for example to write it back to secondary storage or to hand it out to another client.

Figure 2.13: Revocation of a united page with different guarantees associated to its parts.

restartability: Aborted and not fully completed operations modifying the address space mapping, have to be restartable.

**no privilege elevation:** The receiver of a page p must not be able to elevate the access rights it received p with. The only way to increase the access rights of p is to request a new mapping of p with increased rights. This implies that the mapper, that maps the new mapping, itself has sufficient rights.

If a receiver of a page p would be able to extend its access to a page, protection policies cannot be enforced.

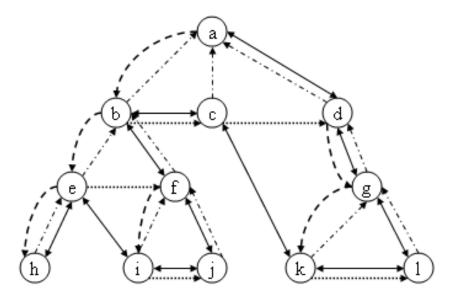

## 2.5 Mapping Database

The Recursive Virtual Address Space Model proposes a recursive construction of address spaces with map, grant and unmap. With those operations, all subsystems can implement their own virtual memory management and protection policies independent of other – even untrusted – subsystems. The operations itself, however, have to be implemented by an entity trusted by all subsystems, i.e. the kernel.

Map and grant can be implemented solely by modifying the page tables. Unmap, however, requires additional information to revoke access from all directly or indirectly derived mappings of a page p. It needs the virtual addresses and the address spaces the page p has been mapped to. This information is stored in a data structure referred to as the mapping database.

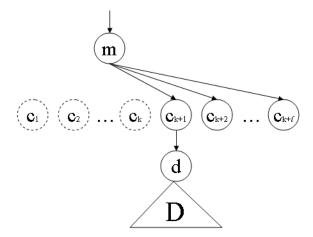

The mapping database contains an entry m for each valid page-table entry of an address space  $\sigma_i$ , i.e. for each page-table entry that translates a page  $p_v$  into a page frame. Given

Figure 2.14: Map inserts a new node into the mapping-database.

this entry  $m(p_v, \sigma_i)$ , the purpose of the mapping database is to find the entries of all virtual addresses and address spaces,  $p_v$  has been mapped to. Unmap iterates through those mapping-database entries and revokes the access from the corresponding pages.

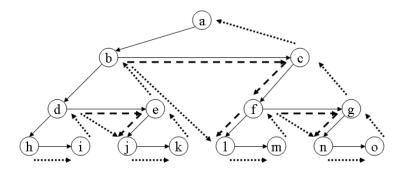

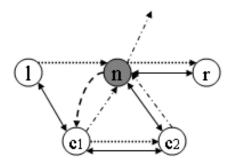

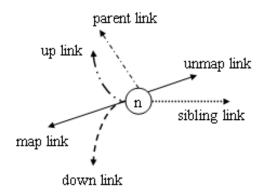

## 2.5.1 Structure of the Mapping Database

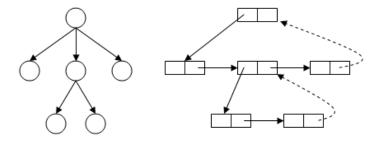

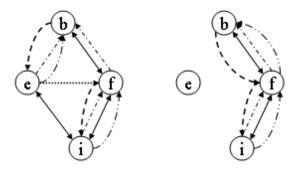

A page  $p_v$  can be mapped several times to one single address space as well as to many address spaces. When uniting adjacently mapped pages into a single large page, a page  $p_v'$  can originate from several pages  $p_v$ . Therefore, the mapping database is a graph. The graph is directed because pages are always mapped form a source address-space into a target address-space. It is acyclic because overmapping avoids cyclic mappings.

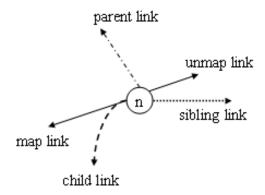

The nodes  $m(p_v, \sigma_i)$  in this acyclic directed graph are the mapping-database entries – or in the following mappings. They denote an address space  $\sigma_i$  and a virtual address of page  $p_v$ . The mapping node stores sufficient information to find and modify the page-table entry of the page  $p_v$  and to invalidate the corresponding entries in the TLBs of the processors in the system.

Outgoing edges are linked to nodes representing pages and address spaces that directly received the mapping of  $p_v$ . Inbound edges are linked to nodes,  $p_v$  originates from.

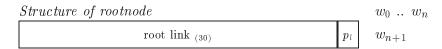

The root nodes of the graph are the nodes, denoted to the initial address-space  $\sigma_0$ . Because of  $\sigma_0$  is constructed with an idempotent mapping of virtual to physical addresses, the  $\sigma_0$ -nodes directly relate to the page frames.

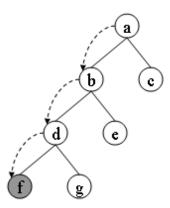

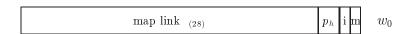

- Map inserts a new node for each page mapped into the mapping database graph and links it as a child to the mapping node of the source page (Figure ??).

- Grant does not modify the mapping database structure, but modifies the page and address space information in the mapping node (Figure 2.15).

Figure 2.15: Grant modifies the existing mapping node only.

Figure 2.16: Unmap removes a node from the mapping database if all rights are revoked from the page.

• *Unmap* iterates through the subgraph of derived mappings to revoke access from the corresponding pages. If all access is revoked from a page, the corresponding mapnode is removed from the mapping database graph as well (Figure 2.16).

With the exception of united mappings, each page originates from exactly one other page (except the pages of  $\sigma_0$ ). If mappings are not united, the indegree of all nodes in the mapping database is 1, except for the root mapping nodes of  $\sigma_0$ . The resulting mapping-database structure is a tree.

## 2.5.2 Requirements and Constraints

### Interface to the Mapping Database

The mapping database offers the following operations as an interface to the database for the address space modifiers: map, grant and unmap.

- find\_map\_node (virtual\_address, address\_space) Given the virtual address and the address space of a page, find\_map\_node searches for the corresponding mapping node in the database.

- find\_page\_table\_entry (mapnode) find\_page\_table\_entry returns the corresponding page-table entry given a mapnode.

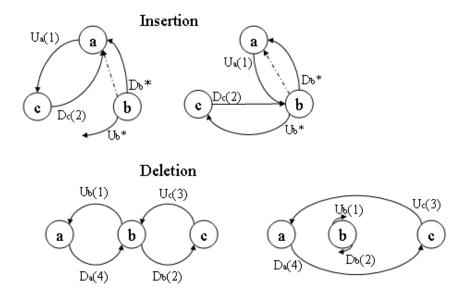

- insert\_mapping (parent\_mapnode) Inserts a new mapnode as a child of the given parent mapnode.

- remove\_mapping (mapnode) Removes the mapnode from the mapping-database graph.

- **Iterator (root\_mapnode)** The mapping database provides unmap with an iterator interface to iterate through all mapnodes of mappings, directly or indirectly derived from the root mapnode.

- find\_first\_leaf (root\_mapnode) The find\_first\_leaf operation searches for the left most leaf node of the subtree with root node: root\_mapnode.

This operation is required only for a post order traversal of unmap. The traversal path starts at this node. Reasoning for post order traversal is given in the next section.

#### Constraints

The following objectives have been committed for the design and implementation of the mapping database.

**space:** The mapping database should require as little space as possible.

time: In general the address space modifiers should perform best possible.

- **preemptability:** Long running operations on the *mapping database* should be preemptable to avoid long interrupt latencies.

- recursion: The limited stack size of an in kernel implementation of the mapping database, demands for iterative instead of recursive algorithms.

- consistency of page tables and mapping database: Modifications of page tables and mapping database have to be consistent. In particular, the three consistency requirements of the Recursive Virtual Address Space Model have to hold: revokability, restartability and no privilege elevation.

- **bounded priority inversion:** Unbounded priority inversion has to be avoided by design of the mapping database.

- **no starvation and deadlocks:** The mapping database has to be free of starvation and must not lead to a deadlock.

uniprocessor and symmetric multiprocessor systems: The objective of this thesis is to provide solutions both for uniprocessor as well as for symmetric multiprocessor systems.

# 2.6 Unbounded Priority Inversion

Existing implementations of the *Recursive Virtual Address Space Model* have lead to undesired behavior or unnecessary complex behavior such as:

- unbounded priority inversion, or

- long interrupt latencies

Complex helping-schemes have been applied to avoid both.

This section examines circumstances leading to unbounded priority inversion in existing implementations of the Recursive Virtual Address Space Model and the means that they apply to avoid that undesired system behavior.

# 2.6.1 Definition

Priority inversion is the phenomenon that the execution of a higher prioritized thread is prevented by a lower prioritized thread [SRL90]. Priority inversion is unbounded if the time of priority inversion is not bounded.

Priority inversion happens if a higher prioritized thread requires a resource held by a lower prioritized thread. The higher prioritized thread is prevented from execution until the lower prioritized releases this resource.

The mapping database is such a resource for the address space modifying operations of the Recursive Virtual Address Space Model: map, grant and unmap.

# 2.6.2 Unbounded Priority Inversion in Address Space Construction

Map, grant and unmap have to prevent conflicting operations from execution, while they modify the mapping database and the page tables. Otherwise, the mapping-database and page-table consistency cannot be guaranteed. If the threads of those prevented operations are higher prioritized as the thread that prevents them, priority inversion occurs. Unbounded priority inversion occurs if the time the higher prioritized threads are prevented from execution is not bounded.

In this thesis orthogonality of scheduling and address space construction is assumed. The Recursive Virtual Address Space Model should not influence scheduling decisions – in particular priority assignment. Conversely address space construction should work independently of the priorities of the participating threads. In particular, a mapper should be able to map to a mappee of any priority, i.e. whether this mappee has a lower or higher priority than the mapper. In any case, the mapper must be able to unmap

this page at any point in time.

It is particularly complicated to bound the time of priority inversion, if a preempted operation prevents higher prioritized operations from execution. For example by holding a lock. This is because we cannot assume, that the lock-holder is scheduled again to release the lock.

In existing implementations two solutions have been applied to solve this problem. The first is to roll forward the operation to completion. The second solution is to "help" out the operation that blocks higher prioritized operations.

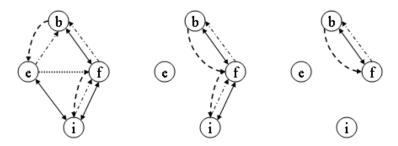

Mapping database operations, mapping, granting or unmapping multiple pages can be preempted after completing with a single page. The Recursive Virtual Address Space Model does not require to order those operations. A multi-page operation therefore can be seen as multiple single-page operations.

Mapping or granting a single page to a target address-space requires to modify only a few nodes in the mapping database. Map inserts a new node, grant modifies the node of the granted page. Those operations can be rolled forward to completion without delaying interrupt handling for a long time. A potential priority inversion caused by those operations is bounded because they are non-preemptively executed to completion. A single page unmap, however, has to revoke access from a potentially large number of pages of the derived mappings. A roll forward of the entire unmap operation may result in long interrupt latencies. Therefore, unmap should be preemptable. To avoid inconsistencies while processing a single node, we assume, that unmap is rolled forward for the time it takes to process this node. Even then, unmap might cause unbounded priority inversion as it is shown in the next section.

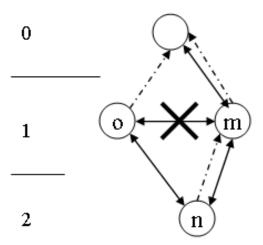

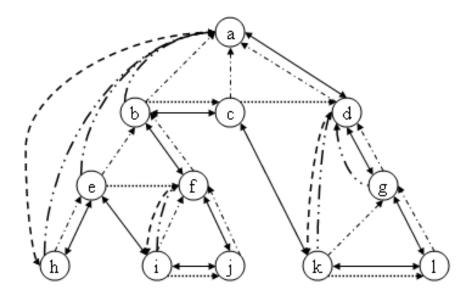

# 2.6.3 Unbounded Priority Inversion of Preorder Unmap

Common to all existing implementations of the Recursive Virtual Address Space Model is a preorder traversal of the mapping database tree for the unmap operation. Unbounded priority inversion occurs, when a lower prioritized unmap operation prevents a higher prioritized mapping database operation from execution by holding a resource required by the higher priority operation. Note, a lower prioritized single page map and grant cannot cause unbounded priority inversion if rolled forward to completion. Because of the roll forward, the time is bound that map or grant potentially blocks the unmap operation.

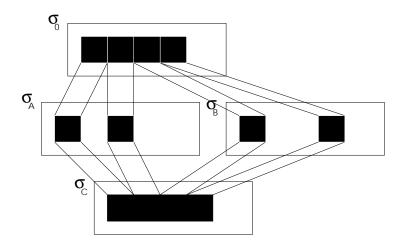

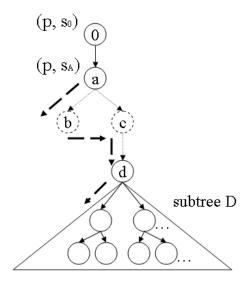

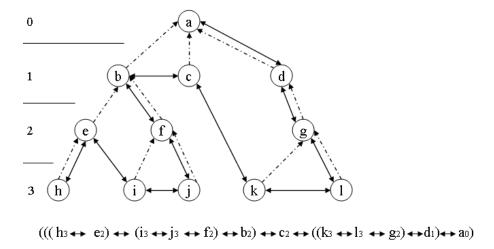

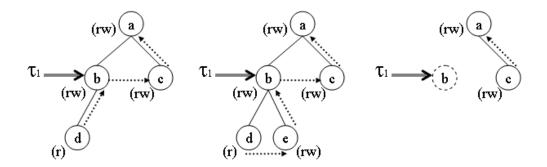

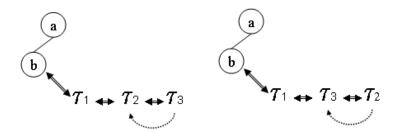

Even if the lower prioritized unmap can be implemented to release all its resources before being preempted, unbounded priority inversion may occur in the presence of a higher prioritized unmap. The following example illustrates this situation (Figure 2.17):

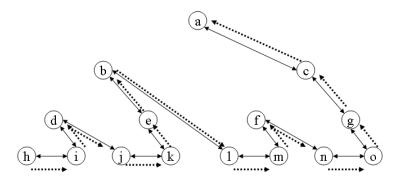

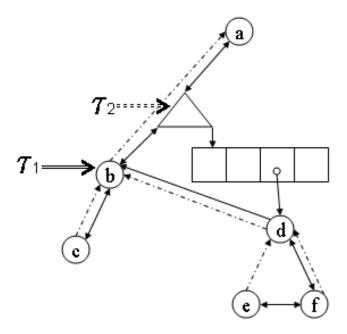

Figure 2.17: Situation of unbound priority inversion of concurrent unmap operations. The dashed lines mark the traversal path of the unmap operation.

We assume that the unmap operation can be preempted after operating a single mapping node, i.e. after revoking access from the page that corresponds to this mapping node. At this time, all resources held by unmap are released. Further, we assume a pre-order traversal of the subtree D of the mapping database to process.

A page p is mapped from address space  $\sigma_A$  to  $\sigma_B$  and  $\sigma_C$ .  $\sigma_C$  further mapped it to  $\sigma_D$  and  $\sigma_D$  continued mapping the page, resulting in a large subtree with root map node d.

A thread  $\tau_A$  in address space  $\sigma_A$  starts to unmap p.  $\tau_A$  manages to remove  $p_B$  in  $\sigma_B$  and  $p_C$  in  $\sigma_C$  before it is preempted. Next, a higher prioritized thread  $\tau_C$  in address space  $\sigma_C$  unmaps  $p_C$ .

Because the mappode c has already been removed from the mapping database,  $\tau_C$  is no longer able to revoke the subtree D with root-mappode d directly. Instead it has to wait for  $\tau_A$  to be rescheduled and complete its operation. Priority is inverted. The priority inversion is unbounded because we do not require the scheduler to reschedule  $\tau_A$  in a limited time again.

The following solutions to avoid unbounded priority inversion in this scenario have been implemented:

1. Unbounded priority inversion is avoided if we would immediately return from  $\tau_C$ 's unmap operation, i.e. not waiting for  $\tau_A$  to complete. This, however, violates the revokability requirement, since D can no longer be revoked by  $\tau_C$ .

Figure 2.18: Generalization of the situation of unbound priority inversion of concurrent unmap operations to other traversal methods.

- 2. In the Fiasco  $\mu$ -kernel the thread  $\tau_C$  donates its timeslice to  $\tau_A$  to help it out of the unmap operation, i.e. to complete the processing of the subtree D.

- 3. Other implementations (for example the x86 assembler implementation L4-Orangepip) execute  $\tau_A$ 's unmap operation to completion, i.e. unmap is implemented non-preemptively. This may result in long interrupt latencies if the subtree D is large.

If instead of  $\tau_C$ , a thread  $\tau_B$  in  $\sigma_B$  would unmap  $p_B$ , the problem does not show up. This is the case because there are no derived mappings from the mapping node b. The fundamental difference, causing the problem for  $\tau_C$ , but not for  $\tau_B$ , is that the preemption of  $\tau_A$  leaves behind the subtree D of derived mappings. This subtree D cannot directly be reached by  $\tau_C$ , and it is large, so that rolling forward  $\tau_A$ 's operation leads to long interrupt latencies.

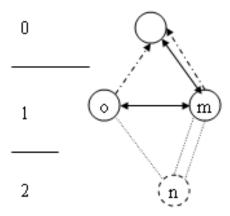

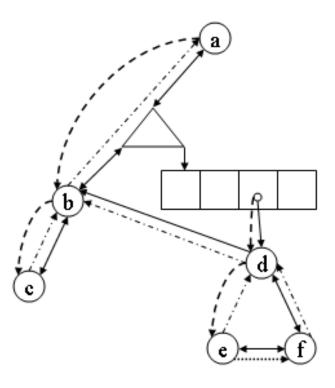

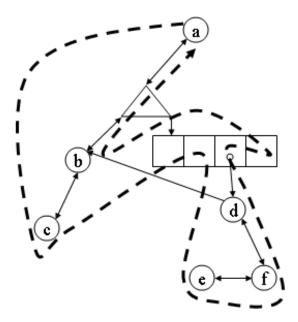

#### 2.6.4 Generalization

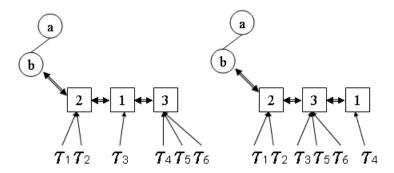

Unmap has to iterate through all mapnodes  $m(p_v, \sigma_i)$  of the subgraph of derived mappings. For each of those nodes processed, access is revoked from the page corresponding to it by modifying the page-table entry. For an arbitrary traversal tough the tree, the following condition holds: Before processing the mapping node  $m(p_v, \sigma_i)$ , i.e. before revoking access from the page  $p_v$ , access from the pages of k of its child nodes has been revoked before, l child nodes remain to process afterwards (see Figure 2.18).

In a pre-order traversal of the tree, k=0 for all mapnodes. All child nodes are processed after the parent node m has been processed.

It is possible to construct a scenario with a similar effect as described above for any traversal order that has a node  $m(p_v, \sigma_i)$  with l > 0. The constraints for this scenario

are that a subtree similar to the subtree D exists that is derived from m. This subtree has to be sufficiently large to cause long interrupt latencies when rolling forward the unmap operation. Furthermore, it has to be linked to one of the l child nodes that have not been processed yet. After revoking m, this subtree D is no longer reachable by a thread in  $\sigma_i$  Unbounded priority inversion does occur if the priority of the preempted unmap is lower than the priority of the thread in  $\sigma_i$ , unmapping m.

A traversal order with l=0 guarantees, that all derived mappings in the tree remain reachable. This is because the following condition holds for all mapping nodes: before revoking access from the page of node m, all child mappings and grant child mappings have been processed before. The traversal method with l=0 for all mapping nodes is called *post order traversal*.

# 2.6.5 Helping

The technique of helping [SRL90,HH01] has been proposed to avoid unbounded priority inversion. A lower prioritized thread blocking a resource needed by higher prioritized threads is "helped" to release the resource and therefore to bound the time, priority is inverted.

This is accomplished by raising the priority of the lower prioritized thread to the priority level of the waiting threads for the time, it holds the resource. The lower prioritized thread effectively runs on the priority level of the waiting thread with the highest priority.

The two most commonly used helping protocols are

- the priority inheritance protocol, and

- the priority ceiling protocol [SRL90].

#### Priority inheritance protocol

The key idea of the priority inheritance protocol is that a thread  $\tau_j$  inherits the highest priority of the threads it blocks by holding a shared resource. The priority of  $\tau_j$  is raised to that of the highest prioritized thread requesting the resource. When  $\tau_j$  releases the resource it unblocks the highest prioritized thread it has blocked. After releasing the resource,  $\tau_j$ 's priority is decreased to its original level.

The priority inheritance protocol bounds the time, priority is inverted. However, it does not prevent deadlocks. Because of chain blocking, a higher prioritized thread may have to wait for a long time until it gets the resource.

# Priority ceiling protocol

The priority ceiling protocol has been proposed to avoid chain blocking. The key idea is to add a ceiling to each resource. This ceiling is the highest priority of all threads currently blocked on the resource. A thread  $\tau_j$  is allowed to acquire and block a released resource, if its priority is higher than the ceiling.

When applying the priority ceiling protocol, the highest prioritized thread blocking on the resource has to wait at most until the current holder releases it. The priority ceiling protocol prevents deadlocks.

#### Wait-free locking with helping

Hohmuth et. al [HH01] proposes a wait-free, i.e. non-blocking starvation free, locking-with-helping scheme. Each resource is protected by a lock. The lock is complemented by a helper stack. When a thread  $\tau_B$  requests the resource and finds it locked by a thread  $\tau_A$ , it inserts its thread control block on the top of the helper stack. Next, it helps  $\tau_A$  to free up the resource and to release the lock by donating its timeslice to it.  $\tau_A$ , when releasing the lock, donates the resource to the thread that is at the top of the helper stack.

Compared to donating priorities along a FIFO wait queue, the stack guarantees a LIFO processing of the waiting threads. When requiring that only one thread exists per priority level and that threads are scheduled according to hard priorities, the highest prioritized thread lands at the top of the stack. Because this thread does not release the processor voluntarily after entering the stack but donates its entire timeslice to the lock-holder, it cannot be preempted by a lower prioritized thread. When we further require, that the lock-holder does not voluntarily release the CPU and does not block, starvation is avoided.

In the L4  $\mu$ -kernel, however, those requirements are not given. First, multiple threads with the same priority may exist. One of those might have entered the stack first, but may be prevented from ever getting the lock because other threads at this priority level can get in front of it on the stack. Starvation occurs. Second, L4 supports hand off scheduling by allowing for a thread to voluntarily donate its timeslice to another one. With this, a higher prioritized thread can temporarily increase the priority of a lower prioritized thread by donating its timeslice. If this lower prioritized thread attempts to acquire the lock while its priority was boosted, it gets on the stack in front of a higher prioritized thread. Again, starvation may occur if this situation persists. Freeness of starvation cannot be guaranteed with the wait-free locking with-helping scheme in the L4  $\mu$ -kernel without restricting possible scheduling policies and timeslice donation.

To "help" out the lock-holder, the timeslices of the "helping" threads are implicitly

2.7. SUMMARY 45

donated to the lock holder. The scheduler, however, accounts this time to the threads that donated it instead of accounting it to the lock-holder. To precisely account for donated time, the kernel has to follow the chain along which the timeslice is donated to the lock holder. Even in the stack based approach, it has to account donated time to the lock holder and when this releases the lock, it has to account the remaining timeslice to the next thread on the stack. Furthermore, it has to provide this information to the scheduler. Both, the accounting and to inform the scheduler about the results is complicated to implement. A more direct approach, for example to roll forward the lock holder is easier to account.

In a multiprocessor system, the scheduler decides on both, the amount of time a thread is allowed to execute and the processor it executes on for that time. Donating this CPU-time to a thread on another processor, therefore requires to either migrate the target thread, or to allow for the donated time to be executed on the other processor later on. Not all scheduling policies tolerate the second option.

Having to implement a "helping" scheme for those, therefore requires to migrate either the lock holder or the "helper" to the same processor, such that the "helper" can donate the timeslice it gets to the lock holder to "help" it release the lock.

Hohmuth el. al proposes a priority queue instead of the stack when migrating the lockholder or when timeslices can be donated across processor boundaries.

When considering the resident cache working set of the lock holder or of the helper, frequent migrations and in particular the transfer of this cache working set may be costly operations. In this situations, having to migrate the lock holder or the helper to be able to donate the timeslice of the helper may be both too complex to implement and too slow.

The solutions presented in this thesis attempt to avoid the necessity of having to implement "helping".

# 2.7 Summary

This section surveyed the necessary background information to understand the Recursive Virtual Address Space Model. The important property of this model is that address spaces can be constructed at user level. Therefore, the model proposes the three address space modifiers: map, grant and unmap.

We presented two optimizations: fast overmap and reference-information retrieval with unmap. Multiple hardware page-size support can lead to split mappings, united mappings and partial unmap of large pages.

The mapping database stores directly and indirectly derived mappings to allow a revocation via *unmap*. It is the fundamental data structure in the implementation of the

Recursive Virtual Address Space Model.

The problem of unbounded priority inversion in the existing implementations of this model has been analyzed. We identified *post-order traversal* of the mapping-database subtree to process on *unmap* as a technique to avoid unbounded priority inversion. In combination with rolling forward parts of the operations that modify address spaces, this traversal method avoids the necessity to implement "helping". The problems and difficulties of those "helping-schemes" have been presented.

# Chapter 3

# Fundamentals and Related work

This chapter provides a review of related work and surveys the fundamentals this work is based on.

In this thesis, we will not introduce to tree and graph theory, but assume the reader is familiar with its terminology. Please refer to [Knu97, Section 2.3, pp 308ff] for more details.

# 3.1 Existing Implementations of the Recursive Virtual Address Space Model

Liedtke [Lie95] proposed the Recursive Virtual Address Space Model and first implemented it in the L4  $\mu$ -kernel. Since then, slightly differing variants have been implemented in the different kernel versions and ports.

# 3.1.1 The $\mu$ -kernel Approach

The  $\mu$ -kernel [ABB<sup>+</sup>86,KN93,ARS89,Lie95,Hil92] is one approach to decrease the complexity of todays operating systems. The key idea is to externalise any policy from the kernel [Lie96] into protected servers executed at user level.

While in  $\mu$ -kernels of the first generation such as Mach, Spring, Chorus only few operating system concepts were deferred into user-level servers, such as paging for example, the second generation  $\mu$ -kernels such as L4, were build on the concept of minimality. Only those functionalities are accepted in the  $\mu$ -kernels, that cannot be implemented in user-level servers.

# 3.1.2 L4 $\mu$ -kernel

The L4  $\mu$ -kernel was developed at the Universität Karlsruhe, at IBM and at the GMD. It provides only three abstractions: threads, address spaces and inter process communication (IPC). Threads execute the program code within the context of an address space. Communication across address space boundaries has to be via inter-process communication or shared memory.

The Recursive Virtual Address Space Model and the three address space modifiers: map, grant and unmap are applied for construction and modification of address spaces. Thereby, map and grant are implemented as a special form of inter process communication. When a thread raises a pagefault, the fault is captured by the  $\mu$ -kernel and translated into an IPC message to the thread's pager. This pager is can resolve the page-fault by replying with a corresponding map-message. After that, the thread will restart at the faulting instruction.

Inter process communication is synchronous and blocking, i.e. both threads participated in the communication have to agree to the communication, the corresponding other thread blocks when this agreement is still outstanding. The L4  $\mu$ -kernel knows short and long copy messages, thereby short messages are guaranteed not to raise page faults. As mentioned above, map and grant are implemented as a special form of IPC. Instead of copying data, memory pages are transferred. As far as known to the author, the L4  $\mu$ -kernel currently achieves the best IPC performance compared to other  $\mu$ -kernels.

The L4  $\mu$ -kernel schedules threads in a prioritized timslice-based round-robin fashion. The parameters for this scheduling can be set by user level scheduling servers. In addition to that, the L4-API supports hand-off scheduling. A thread can donate its timeslice to another thread.

# 3.1.3 Implementations of the Recursive Virtual Address Space Model

The approach presented in this thesis relates to work presented in other implementations of the Recursive Virtual Address Space Model in the L4  $\mu$ -kernel.