Fakultät Informatik Institut für Systemarchitektur, Professur für Betriebssysteme

# OPERATING-SYSTEM CONSTRUCTION

Material based on slides by Olaf Spinczyk, Universität Osnabrück

### **PC Bus Systems (and how to program them)** https://tud.de/inf/os/studium/vorlesungen/betriebssystembau

**HORST SCHIRMEIER**

# **Overview: Lectures**

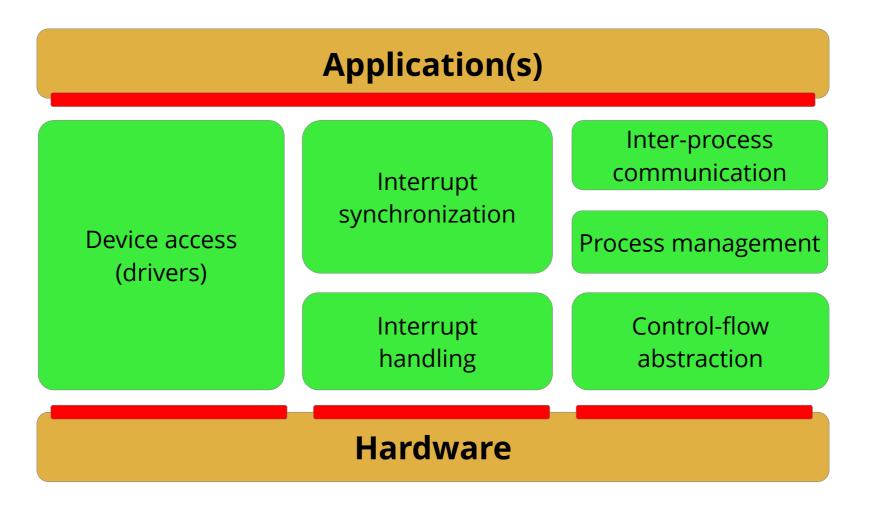

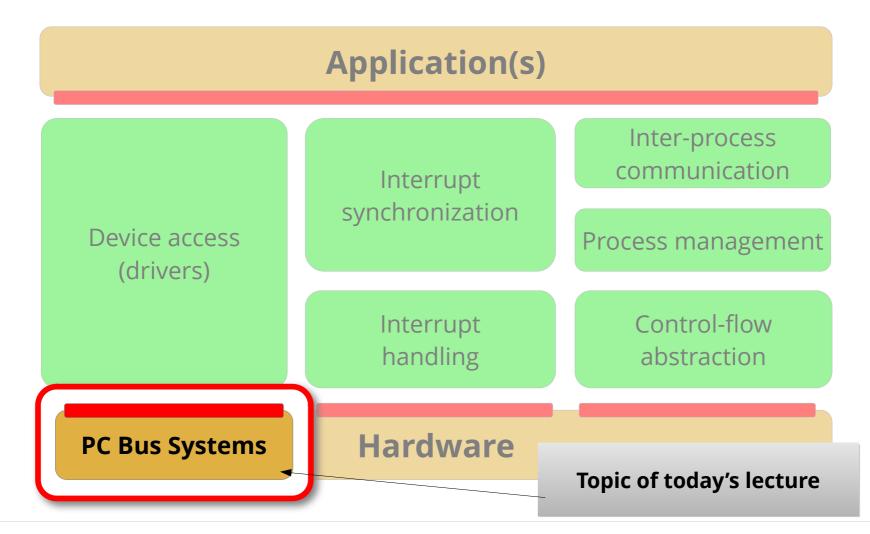

Structure of the "OO-StuBS" operating system:

# **Overview: Lectures**

Structure of the "OO-StuBS" operating system:

#### **OSC: L11 PC Bus Systems**

# Agenda

- History

- PC Bus Systems

- PCI Bus

- PCI from an Operating-System Perspective

- Initialization, PCI BIOS, ...

- PCI Extensions and Successors

- AGP

- PCI-X

- PCI Express

- HyperTransport

- Summary

## Agenda

- History

- PC Bus Systems

- PCI Bus

- PCI from an Operating-System Perspective

- Initialization, PCI BIOS, ...

- PCI Extensions and Successors

- AGP

- PCI-X

- PCI Express

- HyperTransport

- Summary

# History – PC Bus Systems

• Requirements on PC bus systems grew continuously:

| Bus System       | РС      | ISA      | VLB                   | МСА                | EISA               |

|------------------|---------|----------|-----------------------|--------------------|--------------------|

| CPUs             | ≥ 8088  | ≥ 286    | ≥ 386                 | ≥ 386              | ≥ 386              |

| typ. clock freq. | 4,7 MHz | 8 MHz    | 25–50 MHz             | 10–25 MHz          | 8,33 MHz           |

| Multi-Master     | no      | no       | yes (v.2)             | yes                | yes                |

| Bus Width        | 8 bits  | 16 bits  | 32/64 bits            | 32 bits            | 32 bits            |

| Address Space    | 1 MB    | 16 MB    | 4 GB                  | 4 GB               | 4 GB               |

| Transfer Rate    | 1 MB/s  | 4–5 MB/s | 40/64 MB/s<br>(Burst) | 40 MB/s<br>(Burst) | 33 MB/s<br>(Burst) |

**OSC: L11 PC Bus Systems**

# History – PC Bus Systems

• Requirements on PC bus systems grew continuously:

| Bus System       | . PCI                           | AGP                           | PCI-X            | PCI Express                         | HyperTransport                                |

|------------------|---------------------------------|-------------------------------|------------------|-------------------------------------|-----------------------------------------------|

| CPUs             | ≥ 486                           | ≥ 486                         | ≥ P6             | ≥ P4 (Xeon)                         | ≥ Hammer (AMD)                                |

| typ. clock freq. | 33/66 MHz                       | 66 MHz                        | up to<br>133 MHz | (variable)                          | (variable)                                    |

| Multi-Master     | yes                             | no<br>(max. 1 dev.)           | yes              | point-to-point                      | yes, different<br>topologies possible         |

| Bus Width        | 32/64 bits                      | 32 bits                       | 32/64            | up to 32 lanes                      | up to 32 <i>links</i>                         |

| Address Space    | 4 GB/16 EB                      | 4 GB                          | 4 GB/16 EB       | 4 GB/16 EB                          | 4 GB/16 EB                                    |

| Transfer Rate    | 132/528 MB/<br>( <i>Burst</i> ) | /sn x 266 MB/s<br>(1x, 2x,8x) |                  | <i>n</i> x 250 MB/s<br>(1x, 2x,16x) | n x 100–400 MB/s<br>(Burst, per <i>link</i> ) |

**OSC: L11 PC Bus Systems**

# Agenda

- History

- PC Bus Systems

- PCI Bus

- PCI from an Operating-System Perspective

- Initialization, PCI BIOS, ...

- PCI Extensions and Successors

- AGP

- PCI-X

- PCI Express

- HyperTransport

- Summary

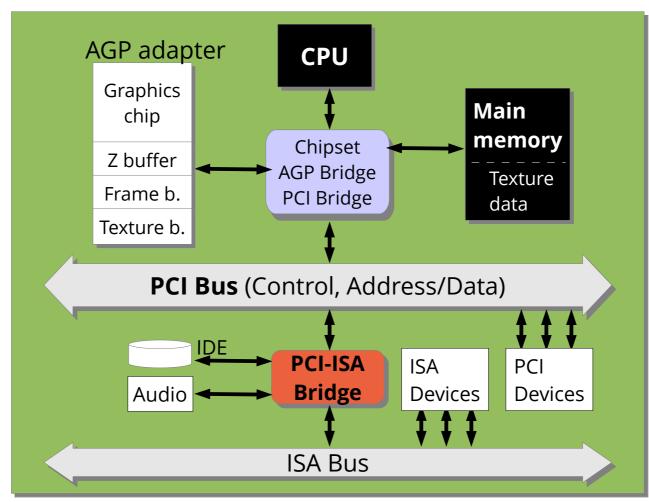

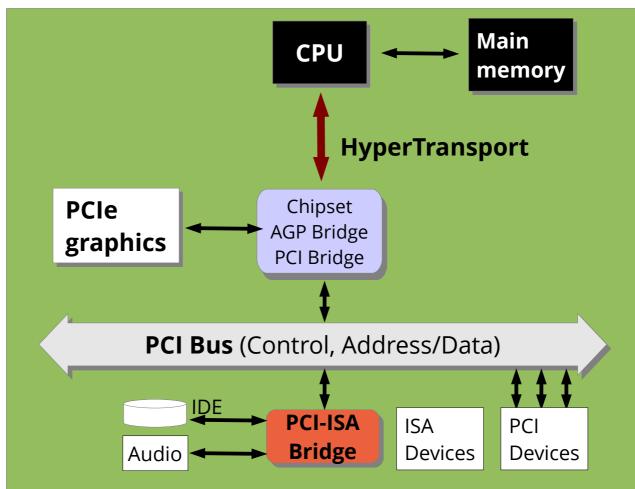

# **PCI-based PC Systems**

**Typical architecture** of the first PCI systems:

The North Bridge CPU decouples host bus and PCI bus. Thus, PCI units and CPU can Host Bus (Control, Address, Data) work in parallel. Addr Data 2<sup>nd</sup> level Main North Addr\_ Ctrl The PCI connection Cache Bridge Memory Tag Ctrl Ctrl between North and South Bridge was later replaced by something PCI Bus (Control, Address/Data) faster. IDE South PCI ISA **Bridges** help **Bridge** Devices Devices Audio integrating ISA and PCI transparently in one system. **ISA Bus**

Data

# PCI – Basic Data

- Specification version 1.0 by Intel (1991)

- Since 1993, the PCI-SIG issues specifications.

- CPU-type independent

- PCI also exists in SPARC, Alpha, Arm and PowerPC systems!

- 32/64 bit, multiplexed address/data bus

- in burst mode max. 132 MB/s respectively 264 MB/s

- 4 interrupt lines (INTA-D)

- Scalable due to bridges and multi-function units

- *Multi-Master* capabilities (better than classic DMA)

- Mechanism to detect and auto-configure devices (resource allocation)

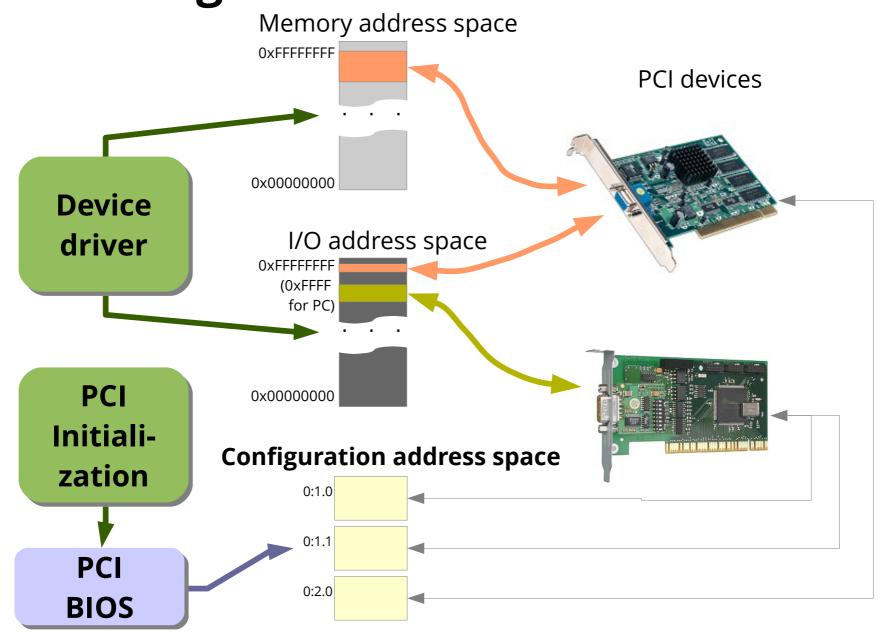

# **Interacting with PCI Devices**

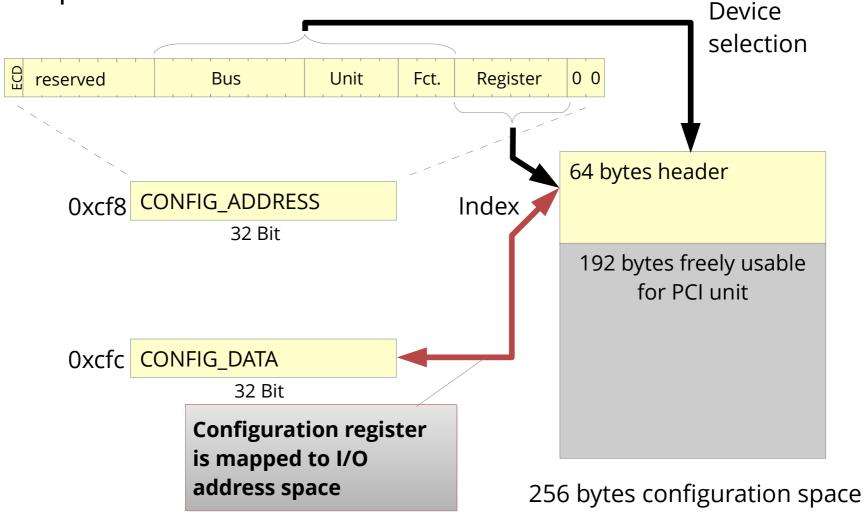

# The PCI Configuration Space (1)

On the PC, the configuration space is accessed indirectly via I/O ports:

12

# The PCI Configuration Space (2)

#### 64-byte header format: •

| <ul> <li>64-byte neade</li> </ul> | _    |                            |            |              |                                                                     | Vendor and Device ID                              |  |  |

|-----------------------------------|------|----------------------------|------------|--------------|---------------------------------------------------------------------|---------------------------------------------------|--|--|

| 31 1615 0                         |      |                            |            |              | uniquely identify a                                                 |                                                   |  |  |

|                                   | 0x00 | Devi                       | ce ID      | Vendor ID    |                                                                     | device. <b>Revision ID</b> and                    |  |  |

| Vendor ID 0xffff                  | 0x04 | Status                     |            | Command      |                                                                     |                                                   |  |  |

| means 'non-existent'.             | 0x08 | Class Code                 |            | e Rev. ID    |                                                                     | <b>Class Code</b> provide additional information. |  |  |

|                                   | 0x0c | BIST                       | Header     | Latency      | CLG                                                                 |                                                   |  |  |

|                                   | 0x10 |                            |            |              |                                                                     | The device can be                                 |  |  |

| Header bit 7=1                    | 0x14 | Base address registers     |            |              |                                                                     | activated and                                     |  |  |

| indicates a <b>multi</b> -        | 0x18 |                            |            |              |                                                                     | deactivated via the<br>Command register.          |  |  |

| function device.                  | 0x1c |                            |            |              |                                                                     |                                                   |  |  |

|                                   | 0x20 |                            |            |              | Here we can define<br>which address ranges<br>the unit uses. At the |                                                   |  |  |

|                                   | 0x24 |                            |            |              |                                                                     |                                                   |  |  |

| <b>BIST</b> allows triggering a   | 0x28 |                            |            |              |                                                                     |                                                   |  |  |

| device's built-in self test.      | 0x2c | reserved or Subsystem IDs  |            |              |                                                                     |                                                   |  |  |

|                                   | 0x30 | Expansion ROM base address |            |              | same time, the device                                               |                                                   |  |  |

|                                   | 0x34 | reserv                     | ved or Cap | pabilities P | Pointer                                                             | announces the (address)                           |  |  |

|                                   | 0x38 |                            |            |              | space it needs.                                                     |                                                   |  |  |

|                                   | 0x3c |                            |            |              |                                                                     |                                                   |  |  |

2023-06-27

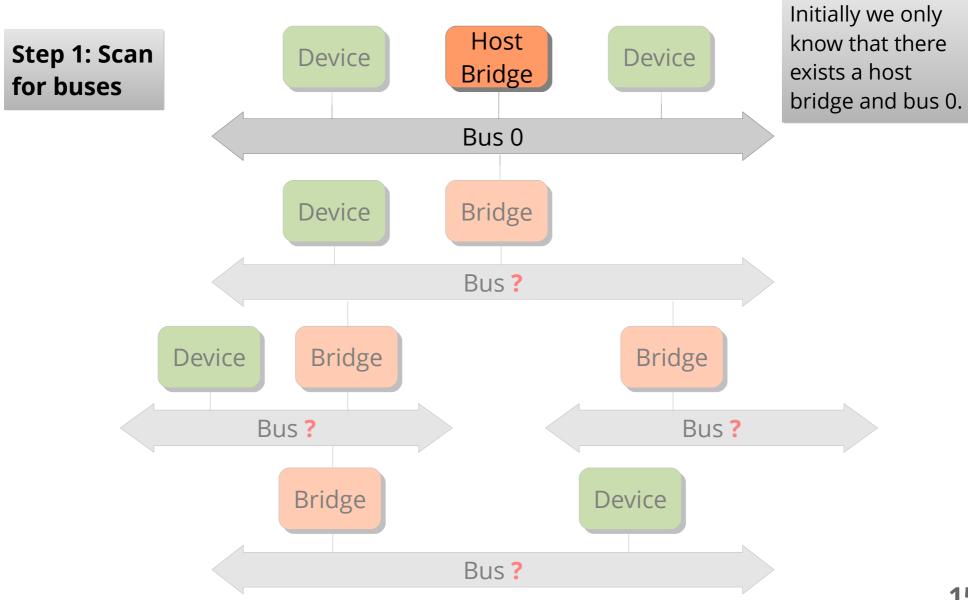

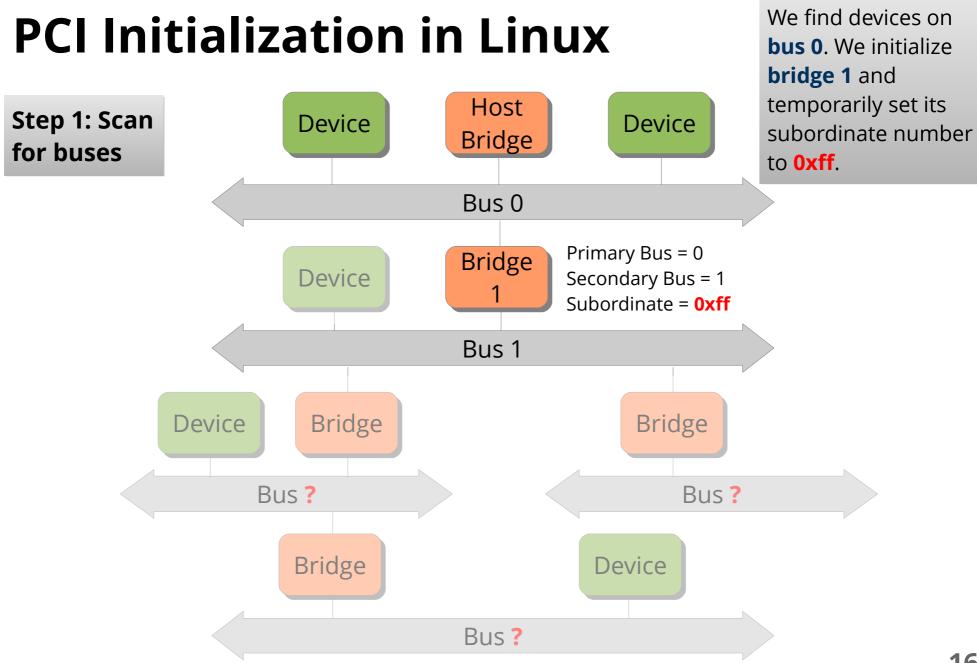

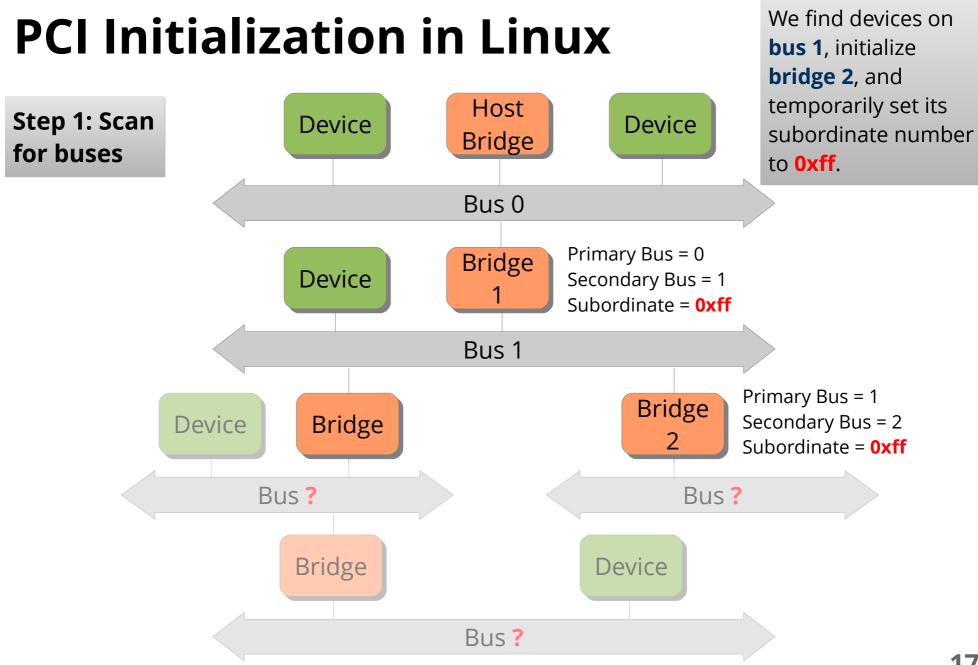

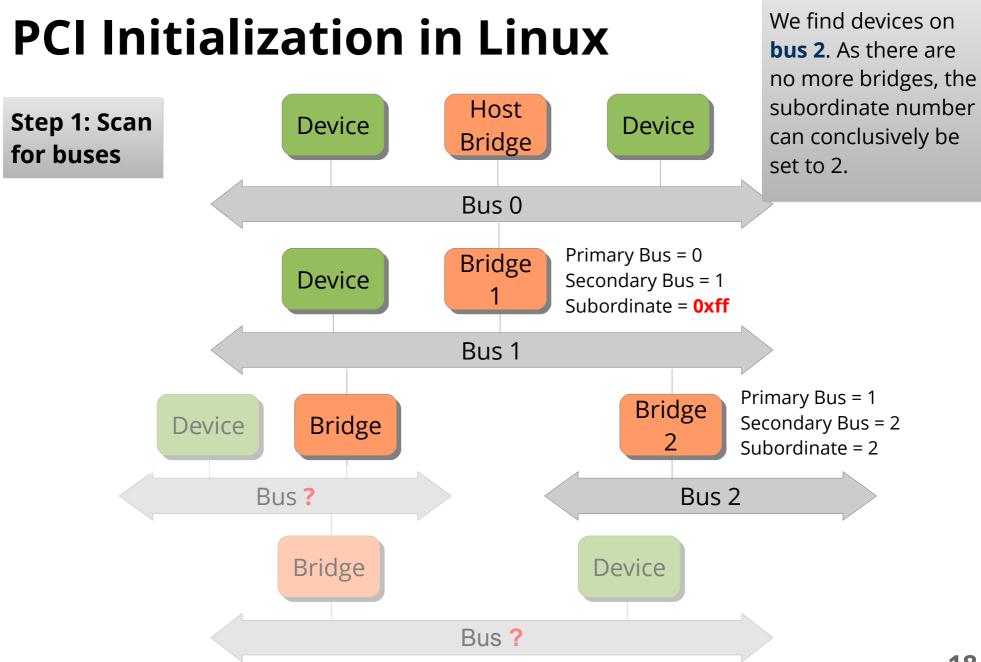

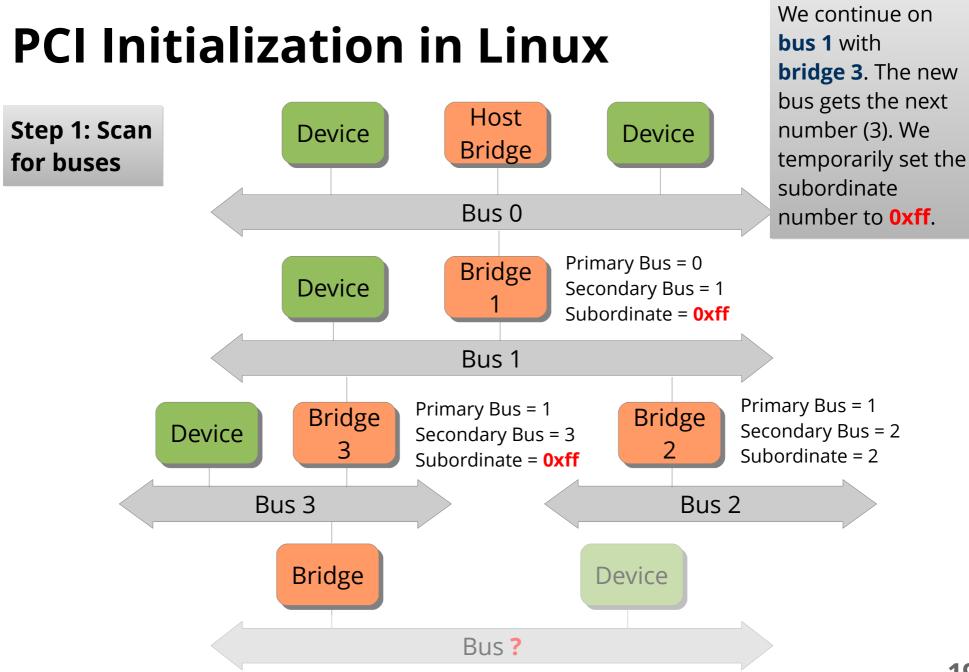

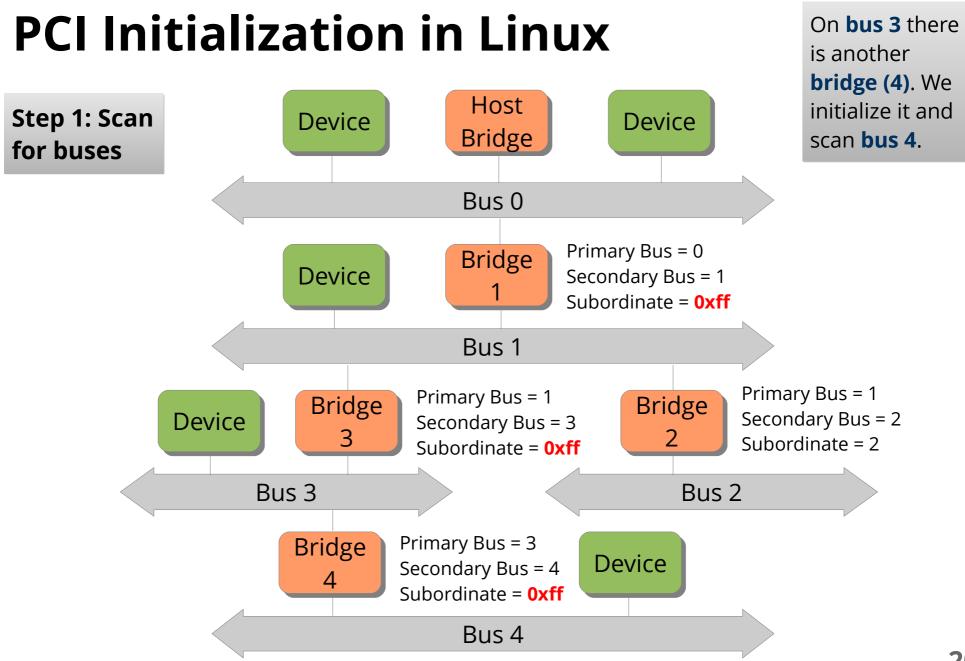

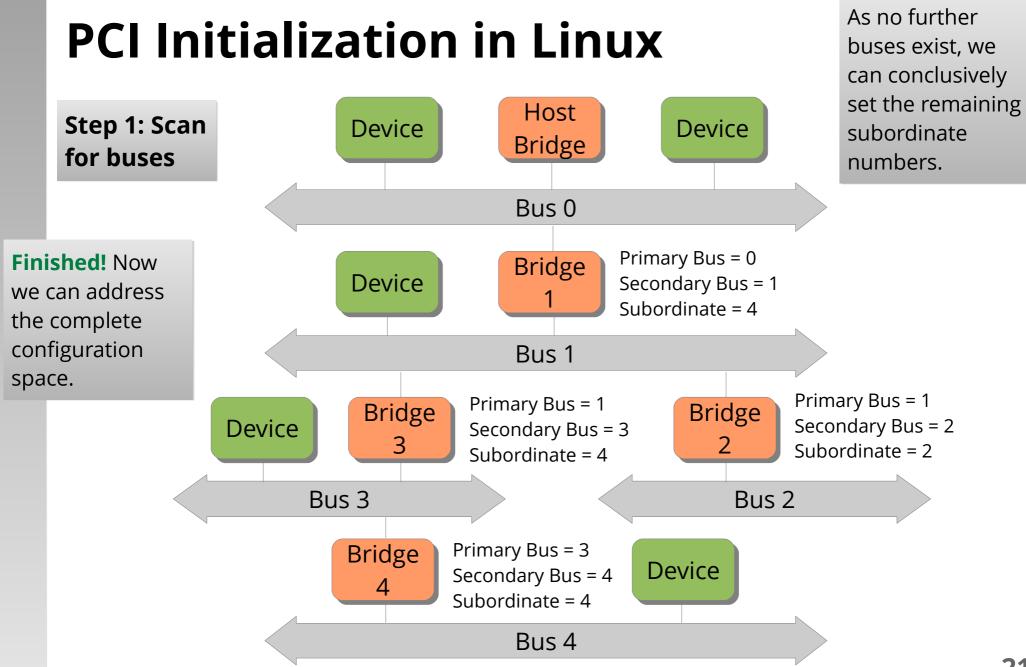

# **PCI Initialization**

Before PCI devices can be accessed by their device drivers, the following steps have to be taken:

- Configure devices' base address registers

- Configure PCI Bridges

- Base address registers depend on devices "below"!

- Bus numbers (*Primary*, *Secondary*, *Subordinate*)

- *Subordinate* is the number of the last downstream bus of this bridge (i.e., "below" a bridge are all buses numbered #secondary to #subordinate)

- BIOS or OS must explore and initialize the PCI bus structure step by step

- Bus numbers and address ranges must never be allocated twice

# **PCI** Initialization in Linux

# **PCI Initialization in Linux**

Step 2: Assign addresses

Algorithm:

- Align I/O and memory addresses of the bridge currently being configured to nearest 4 kiB respectively 1 MiB boundary

- For each device on the current bus (in ascending order of I/O address-space requests):

- Reserve I/O and memory addresses

- Update the global I/O and memory pointers

- Initialize and activate the device

- Recursively apply the algorithm for all connected bridges

- Align resulting addresses (see above)

- Program and activate the bridge

# The PCI BIOS – Overview

- Standardization by PCI-SIG (1993, draft by Intel 1991)

- Usually present on PCs, rarely on other computer types

- Configures PCI bridges and devices at boot time

- minimally if a "Plug & Play" operating system is installed

- otherwise completely

- After booting, the PCI BIOS allows ...

- searching for PCI devices by device class or type

- accessing the configuration space

- Access via

- BIOS interrupt 0x1a (Real Mode)

- the "BIOS32 Service Directory" (Protected Mode)

# The PCI BIOS – in Protected Mode

- The BIOS32 *Service Directory* (in principle) allows to access arbitrary BIOS components.

- It is located somewhere in the range 0xE0000–0xFFFFF:

| Offset | Size    | Description                       |

|--------|---------|-----------------------------------|

| 0x00   | 4 Bytes | Signature "_32_"                  |

| 0x04   | 4 Bytes | physical entry address (for call) |

| 0x08   | 1 Byte  | BIOS32 version (0)                |

| 0x09   | 1 Byte  | Data-structure length / 16 (1)    |

| 0x0a   | 1 Byte  | Checksum                          |

| 0x0b   | 5 Bytes | reserved (0)                      |

• With the BIOS32 service you can test whether a PCI BIOS is available.

# **The PCI BIOS – Functionality**

#### • Specified PCI-BIOS functions:

| Function name              | Arguments                      | Results                                  |  |

|----------------------------|--------------------------------|------------------------------------------|--|

| PCI BIOS Present           | -                              | yes/no, last bus nr.,<br>init. mechanism |  |

| Find PCI Device            | Device ID, Vendor ID,<br>Index | Bus/Dev./Func. Nr.                       |  |

| Find PCI Class Code        | Class Code, Index              | Bus/Dev./Func. Nr.                       |  |

| Generate Special Cycle     | Bus nr.                        | -                                        |  |

| Get Interrupt Routing Opt. | Buffer memory                  | Routing possibilities                    |  |

| Sat DCI Hardwara Interrupt | Bus nr., Device nr.,           |                                          |  |

| Set PCI Hardware Interrupt | int. pin, intnr.               | -                                        |  |

| Read Configuration         |                                | read                                     |  |

| Byte/Word/DWord            | Bus/Dev./Func./Reg. Nr.        | Byte/Word/DWord                          |  |

| Write Configuration        | Bus/Dev./Func./Reg. Nr.,       |                                          |  |

| Byte/Word/DWord            | Byte/Word/DWord to write       | -                                        |  |

# Agenda

- History

- PC Bus Systems

- PCI Bus

- PCI from an Operating-System Perspective

- Initialization, PCI BIOS, ...

- PCI Extensions and Successors

- AGP

- PCI-X

- PCI Express

- HyperTransport

- Summary

# **Accelerated Graphics Port – Hardware**

- AGP, 1997: fast 1:1 connection of **one** (3D) graphics adapter

- (theoretically) N x 266 MB/s transfer rate for AGP 1x, 2x, 4x, ...

# **AGP – Initialization**

- AGP adapter and bridge present themselves to the system like a PCI-to-PCI bridge and a normal PCI device

- full software compatibility

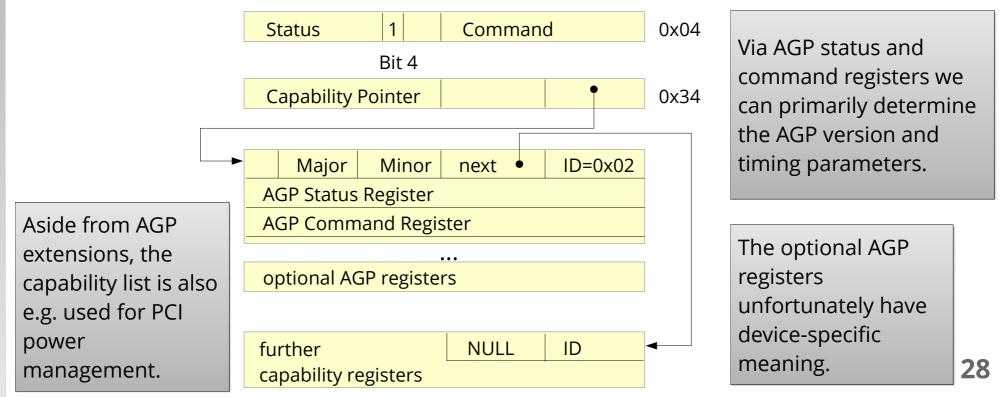

- Special AGP registers can be accessed through the capability list in the configuration space:

# PCI-X (eXtended)

- PCI-bus extension (1999)

- defined by the *PCI Special Interest Group* (SIG) in the PCI 3.0 standard

- Allows for higher bandwidth at full compatibility

- The PCI-X bus uses the configuration of the **slowest** device

| PCI adapter type |         | PC     | l (conventio | PCI-X       |             |             |

|------------------|---------|--------|--------------|-------------|-------------|-------------|

| Bus frequency    |         | 33 MHz | 33 MHz       |             | 66 MHz      |             |

| Voltage          |         | 5 V    | 3.3 V/univ.  | 3.3 V/univ. | 3.3 V/univ. | 3.3 V/univ. |

| Mainboard        |         |        |              |             |             |             |

| PCI              | 33 MHz  | 33 MHz | 33 MHz       | 33 MHz      | 33 MHz      | 33 MHz      |

| PCI              | 66 MHz  | -      | 33 MHz       | 66 MHz      | 33/66 MHz   | 33/66 MHz   |

| PCI-X            | 66 MHz  | -      | 33 MHz       | 33/66 MHz   | 66 MHz      | 66 MHz      |

| PCI-X            | 100 MHz | -      | 33 MHz       | 33/66 MHz   | 66 MHz      | 100 MHz     |

| PCI-X            | 133 MHz | -      | 33 MHz       | 33/66 MHz   | 66 MHz      | 133 MHz     |

- Besides the increased clock frequency: *Split Transactions*

- accessible again via the **capabilities list**

# **PCI Express**

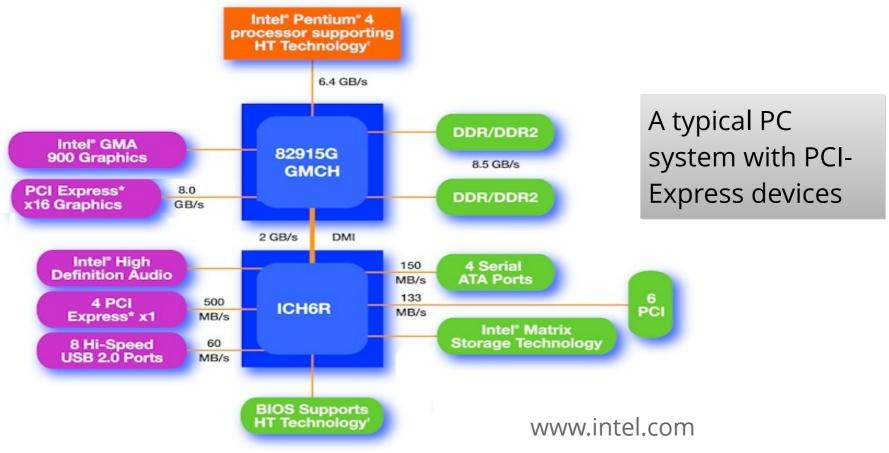

- ... technically has little to do with the original PCI bus

- Bi-directional, serial, point-to-point connections

- Bandwidth per **lane** per direction: 512 MB/s, 8GB/s at x16

# HyperTransport

- (AMD) CPU integrates memory controller and L2 cache

- Standardized communication with North Bridge

# HyperTransport

- Standardized in several versions 2001–2008

- Consortium: AMD, Apple, Cisco, NVIDIA, Sun, ...

- Bi-directional, point-to-point, links with 2–32 bits, clocked up to 3.2 GHz (DDR)

- Depending on version and configuration up to 12.8 GB/s (uni-dir.)

- Successor: AMD Infinity Fabric (HyperTransport "superset"), up to 72 GB/s

- Device configuration like with PCI

- Further uses aside from FSB replacement

- Inter-CPU communication

- Chipset communication (Northbridge ⇔ Southbridge)

- Communication with co-processors: HTX

- Intel pendants: QuickPath Interconnect (QPI, since 2008, 12.8 GB/s) and Ultra Path Interconnect (UPI, 2017, 20.8 GB/s)

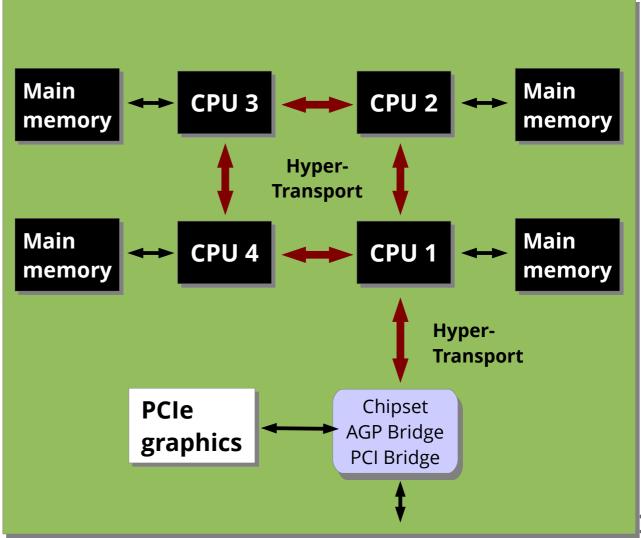

# HyperTransport in MP Systems

• **NUMA** (<u>Non-Uniform Memory Architecture</u>)

CPUs (with multiple cores each) communicate via HyperTransport.

Global address space: Main memory attached to other CPUs can be addressed, but with higher latency.

The operating system must distribute tasks accordingly.

# Agenda

- History

- PC Bus Systems

- PCI Bus

- PCI from an Operating-System Perspective

- Initialization, PCI BIOS, ...

- PCI Extensions and Successors

- AGP

- PCI-X

- PCI Express

- HyperTransport

- Summary

# Summary

- PCI has been dominating PC bus systems for decades

- Newer developments (PCI Express) hardly share similarities with the PCI bus from 1991

- serial point-to-point connections and **switches**

- Aside from physical properties, PCI also defines a programming model

- I/O and memory address spaces

- Configuration and initialization via configuration space

- Bus hierarchies

- Even the newest developments are compatible to PCI on the programming-model level