|

NOVA User-Level Environment

Version testbox/changed-memory-timing-317-g320d8b5

|

|

NOVA User-Level Environment

Version testbox/changed-memory-timing-317-g320d8b5

|

Public Member Functions | |

| bool | receive (MessageMem &msg) |

| Receive MMIO access. | |

| bool | receive (MessageMemRegion &msg) |

| Receive MMIO map request. | |

| bool | receive (MessageTimeout &msg) |

| Timeout for the APIC timer. | |

| bool | receive (MessageApic &msg) |

| Receive an IPI. | |

| bool | receive (LapicEvent &msg) |

| Receive INTA cycle or RESET from the CPU. | |

| bool | receive (CpuMessage &msg) |

| Receive RDMSR and WRMSR messages. | |

| bool | receive (MessageLegacy &msg) |

| Legacy pins. | |

| void | discovery () |

| Lapic (Motherboard &mb, VCpu *vcpu, unsigned initial_apic_id, unsigned timer) | |

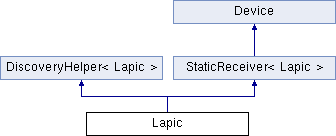

Public Member Functions inherited from StaticReceiver< Lapic > Public Member Functions inherited from StaticReceiver< Lapic > | |

| StaticReceiver () | |

Public Member Functions inherited from Device Public Member Functions inherited from Device | |

| void | debug_dump () |

| Device (const char *debug_name) | |

Public Attributes | |

| Motherboard & | _mb |

Private Types | |

| enum | { MAX_FREQ = 200000000, LVT_MASK_BIT = 16, OFS_ISR = 0, OFS_TMR = 256, OFS_IRR = 512, LVT_BASE = _TIMER_offset, NUM_LVT = 6, APIC_ADDR = 0xfee00000 } |

Private Member Functions | |

| bool | sw_disabled () |

| bool | hw_disabled () |

| bool | x2apic_mode () |

| unsigned | x2apic_ldr () |

| void | init () |

| Handle an INIT signal. | |

| void | reset () |

| Reset the APIC to some default state. | |

| bool | set_base_msr (unsigned long long value) |

| Update the APIC base MSR. | |

| unsigned | get_ccr (timevalue now) |

| Checks whether a timeout should trigger and returns the current counter value. | |

| void | update_timer (timevalue now) |

| Reprogram a new host timer. | |

| bool | send_ipi (unsigned icr, unsigned dst) |

| We send an IPI. | |

| unsigned | get_highest_bit (unsigned bit_offset) |

| Scan for the highest bit in the ISR or IRR. | |

| unsigned | processor_prio () |

| Calc the PPR. | |

| unsigned | prioritize_irq () |

| Check whether there is an EXTINT in the LVTs or an IRQ above the processor prio to inject. | |

| void | update_irqs () |

| Send upstream to the CPU that we have an IRQ. | |

| bool | set_error (unsigned bit) |

| Indicate an error and trigger the error LVT. | |

| void | accept_vector (unsigned char vector, bool level, bool value) |

| Accept a fixed vector in the IRR. | |

| void | broadcast_eoi (unsigned vector) |

| Broadcast an EOI on the bus if it is level triggered. | |

| bool | register_read (unsigned offset, unsigned &value) |

| bool | register_write (unsigned offset, unsigned value, bool strict) |

| bool | trigger_lvt (unsigned num) |

| Trigger an LVT entry. | |

| bool | accept_message (MessageApic &msg) |

| Check whether we should accept the message. | |

Private Attributes | |

| VCpu * | _vcpu |

| unsigned | _initial_apic_id |

| unsigned | _timer |

| unsigned | _timer_clock_shift |

| unsigned | _timer_dcr_shift |

| timevalue | _timer_start |

| unsigned long long | _msr |

| unsigned | _vector [8 *3] |

| unsigned | _esr_shadow |

| unsigned | _isrv |

| bool | _lvtds [NUM_LVT] |

| bool | _rirr [NUM_LVT] |

| unsigned | _lowest_rr |

Additional Inherited Members | |

Static Public Member Functions inherited from DiscoveryHelper< Lapic > Static Public Member Functions inherited from DiscoveryHelper< Lapic > | |

| static bool | discover (Device *o, MessageDiscovery &msg) |

Static Public Member Functions inherited from StaticReceiver< Lapic > Static Public Member Functions inherited from StaticReceiver< Lapic > | |

| static bool | receive_static (Device *o, M &msg) |

Protected Member Functions inherited from DiscoveryHelper< Lapic > Protected Member Functions inherited from DiscoveryHelper< Lapic > | |

| bool | discovery_write_st (const char *resource, unsigned offset, const void *value, unsigned count) |

| bool | discovery_write_dw (const char *resource, unsigned offset, unsigned value, unsigned count=4) |

| Write a dword or less than it. | |

| bool | discovery_read_dw (const char *resource, unsigned offset, unsigned &value) |

| Read a dword. | |

| unsigned | discovery_length (const char *resource, unsigned minlen) |

| Return the length of an ACPI table or minlen if it is smaller. | |

Lapic model.

State: testing Features: MEM, MSR, MSR-base and CPUID, LVT, LINT0/1, EOI, prioritize IRQ, error, RemoteEOI, timer, IPI, lowest prio, reset, x2apic mode, BIOS ACPI tables Missing: focus checking, CR8/TPR setting Difference: no interrupt polarity, lowest prio is round-robin Documentation: Intel SDM Volume 3a Chapter 10 253668-033.

|

private |

|

inline |

|

inlineprivate |

Check whether we should accept the message.

|

inlineprivate |

Accept a fixed vector in the IRR.

|

inlineprivate |

Broadcast an EOI on the bus if it is level triggered.

|

inline |

|

inlineprivate |

Checks whether a timeout should trigger and returns the current counter value.

|

inlineprivate |

Scan for the highest bit in the ISR or IRR.

|

inlineprivate |

|

inlineprivate |

Handle an INIT signal.

|

inlineprivate |

Check whether there is an EXTINT in the LVTs or an IRQ above the processor prio to inject.

|

inlineprivate |

Calc the PPR.

|

inline |

Receive MMIO access.

|

inline |

Receive MMIO map request.

We return true without setting msg.ptr and thus nobody else can claim this region.

|

inline |

Timeout for the APIC timer.

|

inline |

Receive an IPI.

|

inline |

Receive INTA cycle or RESET from the CPU.

|

inline |

Receive RDMSR and WRMSR messages.

|

inline |

Legacy pins.

|

inlineprivate |

|

inlineprivate |

|

inlineprivate |

Reset the APIC to some default state.

|

inlineprivate |

We send an IPI.

This is a strange thing in the manual: lowest priority with a broadcast shorthand is invalid. But what about physical destination mode with dst=0xff?

|

inlineprivate |

Update the APIC base MSR.

|

inlineprivate |

Indicate an error and trigger the error LVT.

Make sure we do not loop, if the ERROR LVT has also an invalid vector programmed.

|

inlineprivate |

|

inlineprivate |

Trigger an LVT entry.

It is not defined how invalid Delivery Modes are handled. We simply drop SIPI, RRD and LOWEST here.

|

inlineprivate |

Send upstream to the CPU that we have an IRQ.

|

inlineprivate |

Reprogram a new host timer.

|

inlineprivate |

|

inlineprivate |

|

private |

|

private |

|

private |

|

private |

|

private |

| Motherboard& Lapic::_mb |

|

private |

|

private |

|

private |

|

private |

|

private |

|

private |

|

private |

|

private |