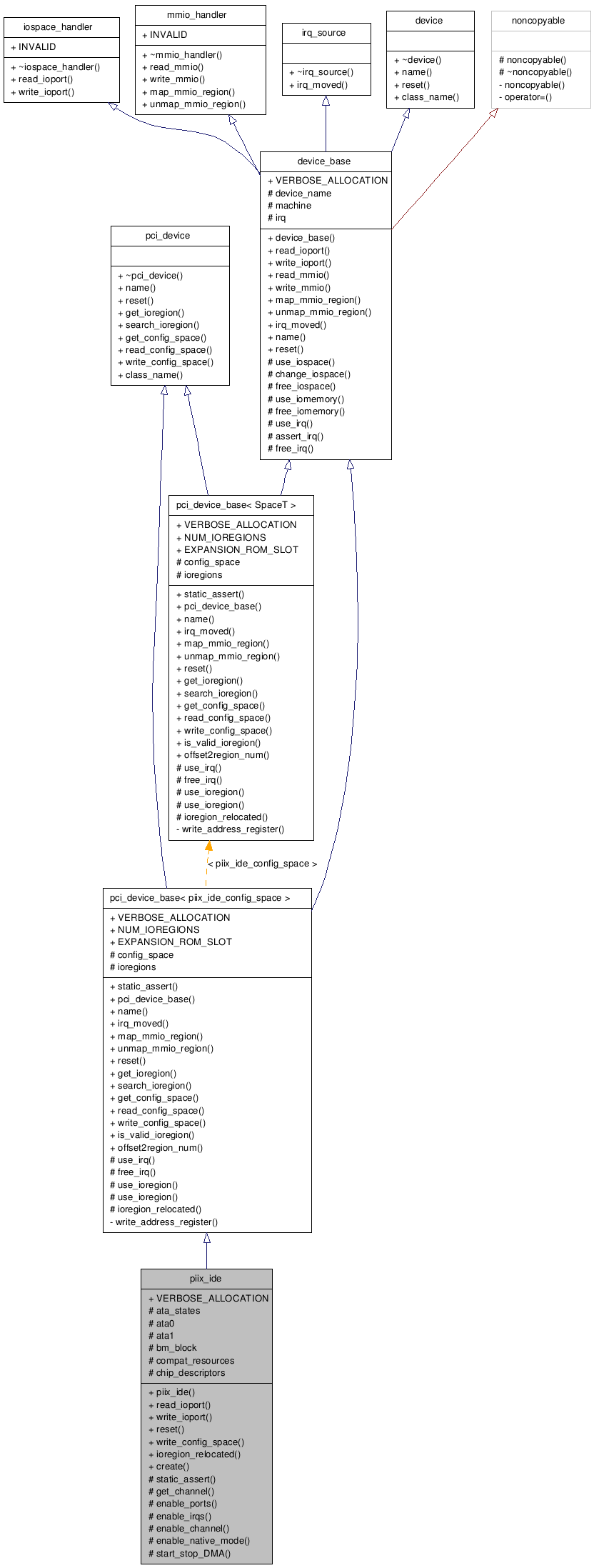

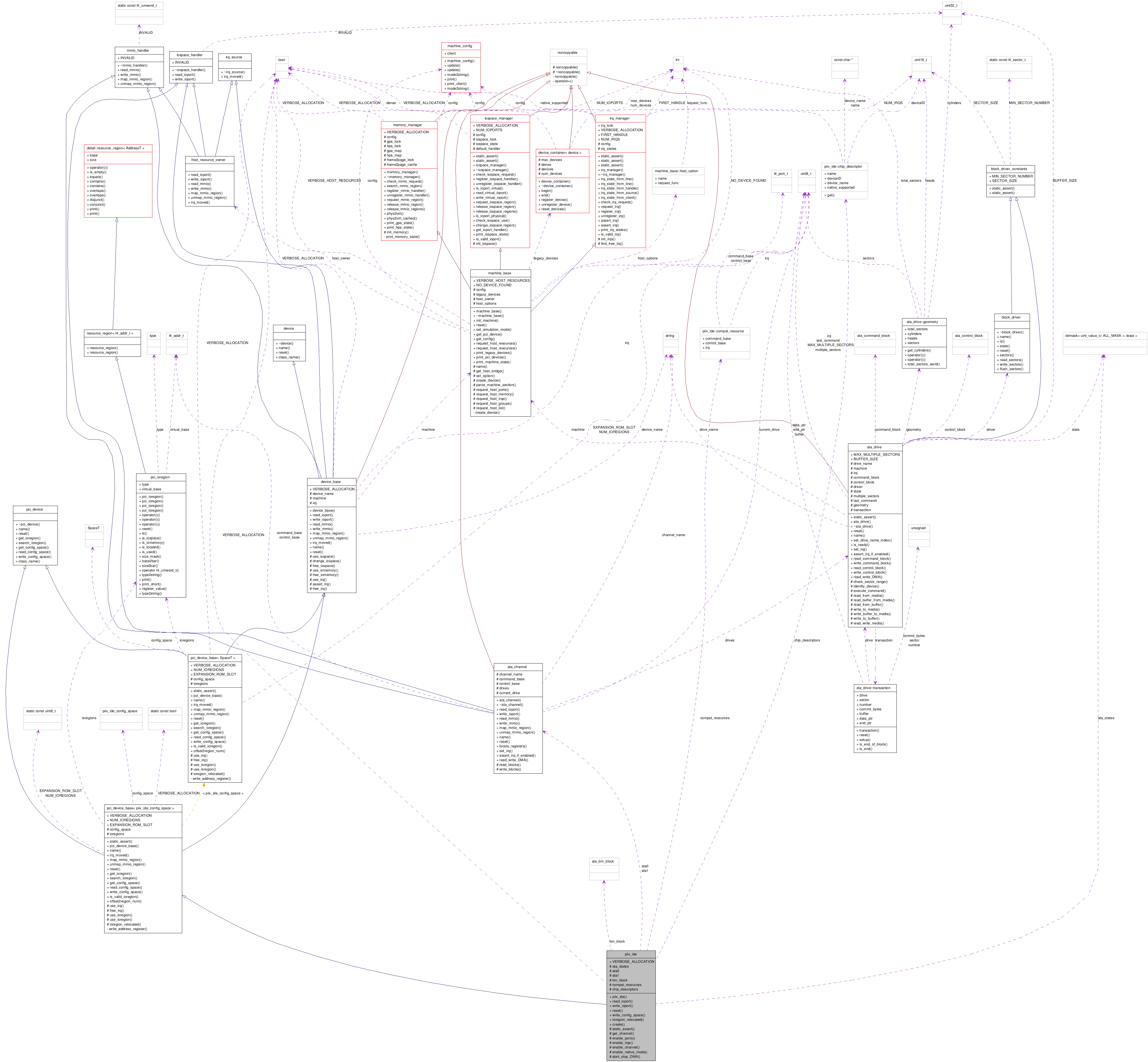

piix_ide Struct Reference

Virtual Intel PIIX/ICH compatible IDE controller. More...

#include <piix_ide.hpp>

Public Member Functions | |

| piix_ide (machine_base &machine, ata_drive *drives[4], const chip_descriptor *chip=nullptr, bool native_enabled=true) | |

| virtual uint32_t | read_ioport (l4_port_t port, access_size access_size) |

| Stub implementation, which always returns an invalid value. | |

| virtual int | write_ioport (l4_port_t port, uint32_t data, access_size access_size) |

| Stub implementation, which always returns -L4_ENOTSUPP. | |

| virtual int | reset (void) |

| Resets the device's state back to defaults as when powering up the machine. | |

| virtual int | write_config_space (pci_config_header16::offset_t offset, l4_umword_t data, access_size access_size) |

| Emulates a device's PCI configuration space write access. | |

| virtual int | ioregion_relocated (uint8_t region_num, l4_gpa_t old_base) |

| Called whenever the PCI configuration space write handler updates an address register. | |

Static Public Member Functions | |

| static pci_device * | create (machine_base &machine, config_node &device_node) |

Static Public Attributes | |

| static const bool | VERBOSE_ALLOCATION = false |

Protected Types | |

| enum | ata_state_constants { DECODE_ENABLED = 0x01, COMMAND_REGISTERED = 0x02, CONTROL_REGISTERED = 0x04, IRQ_REGISTERED = 0x08, NATIVE_MODE_SUPPORTED = 0x10, NATIVE_MODE_ENABLED = 0x20, ALL_MASK } |

|

typedef pci_device_base < piix_ide_config_space > | super_type |

|

typedef bitmask< uint_value_t < ALL_MASK >::least > | ata_state |

Protected Member Functions | |

| static_assert (integer_traits< ata_state::word_type >::const_max >=ALL_MASK,"ata_state's max value is too small") | |

| ata_channel & | get_channel (const uint8_t channel_ix) |

| int | enable_ports (uint8_t channel_ix, bool enable=true, bool verbose=VERBOSE_ALLOCATION, l4_port_t command_base=0, l4_port_t control_base=0) |

| int | enable_irqs (uint8_t channel_ix, bool enable=true, bool verbose=VERBOSE_ALLOCATION) |

| int | enable_channel (uint8_t channel_ix, bool enable=true, bool verbose=VERBOSE_ALLOCATION) |

| int | enable_native_mode (uint8_t channel_ix, bool enable=true, bool verbose=VERBOSE_ALLOCATION) |

| void | start_stop_DMA (uint8_t channel_ix) |

Protected Attributes | |

| ata_state | ata_states [2] |

| ata_channel | ata0 |

| ata_channel | ata1 |

| ata_bm_block | bm_block |

Static Protected Attributes | |

|

static struct piix_ide::compat_resource | compat_resources [] |

| static struct piix_ide::chip_descriptor | chip_descriptors [] |

Classes | |

| struct | chip_descriptor |

| struct | compat_resource |

Detailed Description

Virtual Intel PIIX/ICH compatible IDE controller.Member Function Documentation

| uint32_t piix_ide::read_ioport | ( | l4_port_t | port, | |

| access_size | access_size | |||

| ) | [virtual] |

Stub implementation, which always returns an invalid value.

Implemented here as a dummy to avoid unnecessary overriding in descendant classes. This function is intended to be overridden.

Reimplemented from device_base.

References detail::resource_region< AddressT >::base, iospace_handler::INVALID, pci_device_base< piix_ide_config_space >::ioregions, and pci_device_base< piix_ide_config_space >::name().

| int piix_ide::write_ioport | ( | l4_port_t | port, | |

| uint32_t | data, | |||

| access_size | access_size | |||

| ) | [virtual] |

Stub implementation, which always returns -L4_ENOTSUPP.

Implemented here as a dummy to avoid unnecessary overriding in descendant classes. This function is intended to be overridden.

Reimplemented from device_base.

References detail::resource_region< AddressT >::base, pci_device_base< piix_ide_config_space >::ioregions, and pci_device_base< piix_ide_config_space >::name().

| int piix_ide::write_config_space | ( | pci_config_header16::offset_t | offset, | |

| l4_umword_t | data, | |||

| access_size | access_size | |||

| ) | [virtual] |

Emulates a device's PCI configuration space write access.

This function is intended to be overridden.

Reimplemented from pci_device_base< piix_ide_config_space >.

References pci_device_base< piix_ide_config_space >::config_space, pci_device_base< piix_ide_config_space >::name(), and pci_device_base< piix_ide_config_space >::write_config_space().

| int piix_ide::ioregion_relocated | ( | uint8_t | region_num, | |

| l4_gpa_t | old_base | |||

| ) | [virtual] |

Called whenever the PCI configuration space write handler updates an address register.

The corresponding pci_ioregion has already been updated. Only resources may be freed/(re-)requested to respond to the new location's accesses. The default implementation simply unregisters and registers itself.

Reimplemented from pci_device_base< piix_ide_config_space >.

References detail::resource_region< AddressT >::base, pci_device_base< piix_ide_config_space >::ioregion_relocated(), pci_device_base< piix_ide_config_space >::ioregions, pci_ioregion::is_used(), pci_device_base< piix_ide_config_space >::name(), and pci_ioregion::print_short().

Member Data Documentation

const piix_ide::chip_descriptor piix_ide::chip_descriptors [static, protected] |

Initial value:

{

{name: "ich3", deviceID: 0x248b, device_name: "ICH3 IDE", native_supported: true},

{name: "piix", deviceID: 0x1230, device_name: "PIIX IDE", native_supported: false},

{name: "piix3", deviceID: 0x7010, device_name: "PIIX3 IDE", native_supported: false},

{name: "piix4", deviceID: 0x7111, device_name: "PIIX4 IDE", native_supported: false},

{name: "ich0", deviceID: 0x2421, device_name: "ICH0 IDE", native_supported: false},

{name: "ich1", deviceID: 0x2411, device_name: "ICH1 IDE", native_supported: false},

{name: "ich2", deviceID: 0x244b, device_name: "ICH2 IDE", native_supported: false},

{name: "ich4", deviceID: 0x24cb, device_name: "ICH4 IDE", native_supported: true},

{name: "ich5", deviceID: 0x24db, device_name: "ICH5 IDE", native_supported: true},

{name: "ich6", deviceID: 0x266f, device_name: "ICH6 IDE", native_supported: true},

{name: "ich7", deviceID: 0x27df, device_name: "ICH7 IDE", native_supported: true},

{name: "ich8m", deviceID: 0x2850, device_name: "ICH8M IDE", native_supported: true},

{name: nullptr, deviceID: 0xffff, device_name: nullptr, native_supported: false}

}

The documentation for this struct was generated from the following files:

- piix_ide.hpp

- piix_ide.cpp